外部拓展芯片

IS62WV51216A

芯片手册

支持高速时钟通道时间为45、55ns

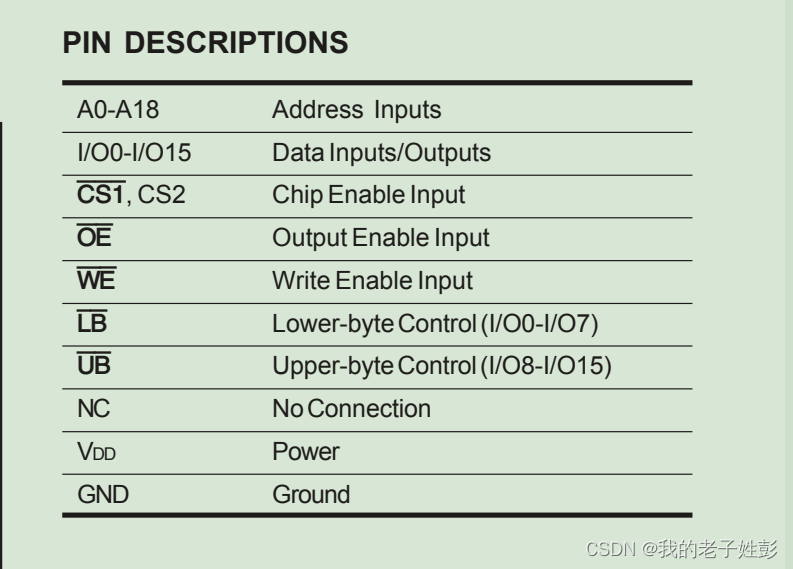

芯片引脚定义

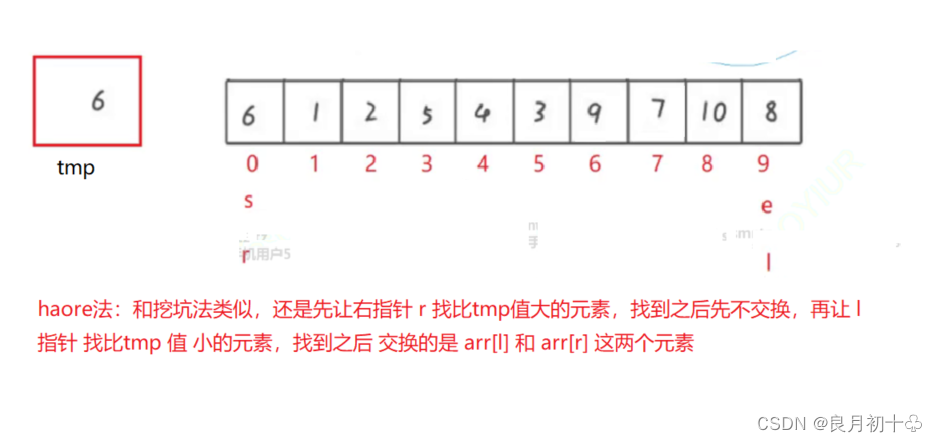

通道时序

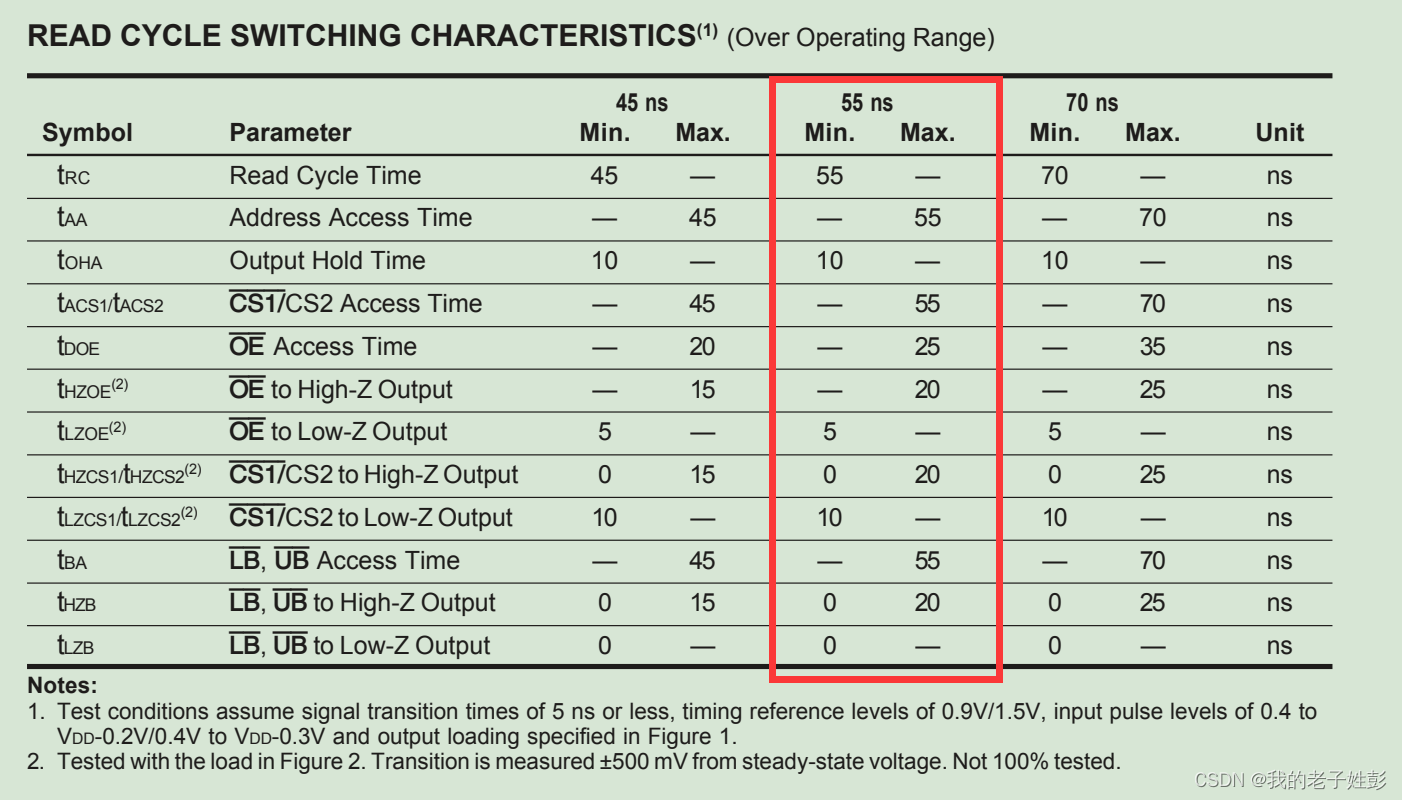

读定义表

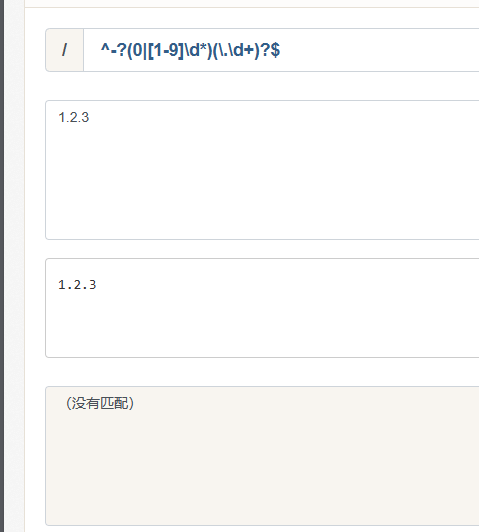

一个纵列表示当前使用的高速通道的时间,选一个纵列作为参数标准。

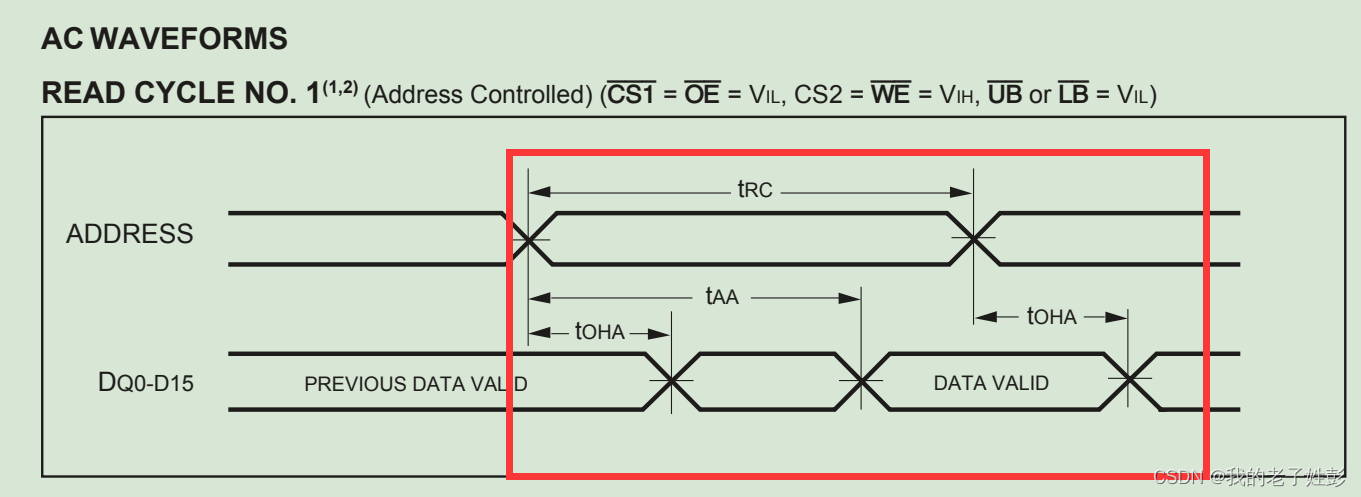

地址控制读时序

如图,大概需要三个参数

写时序定义表

还是选择55ns参数

写时序图

CS1和OE控制

关键在Twc和Thd,但是Thd为0

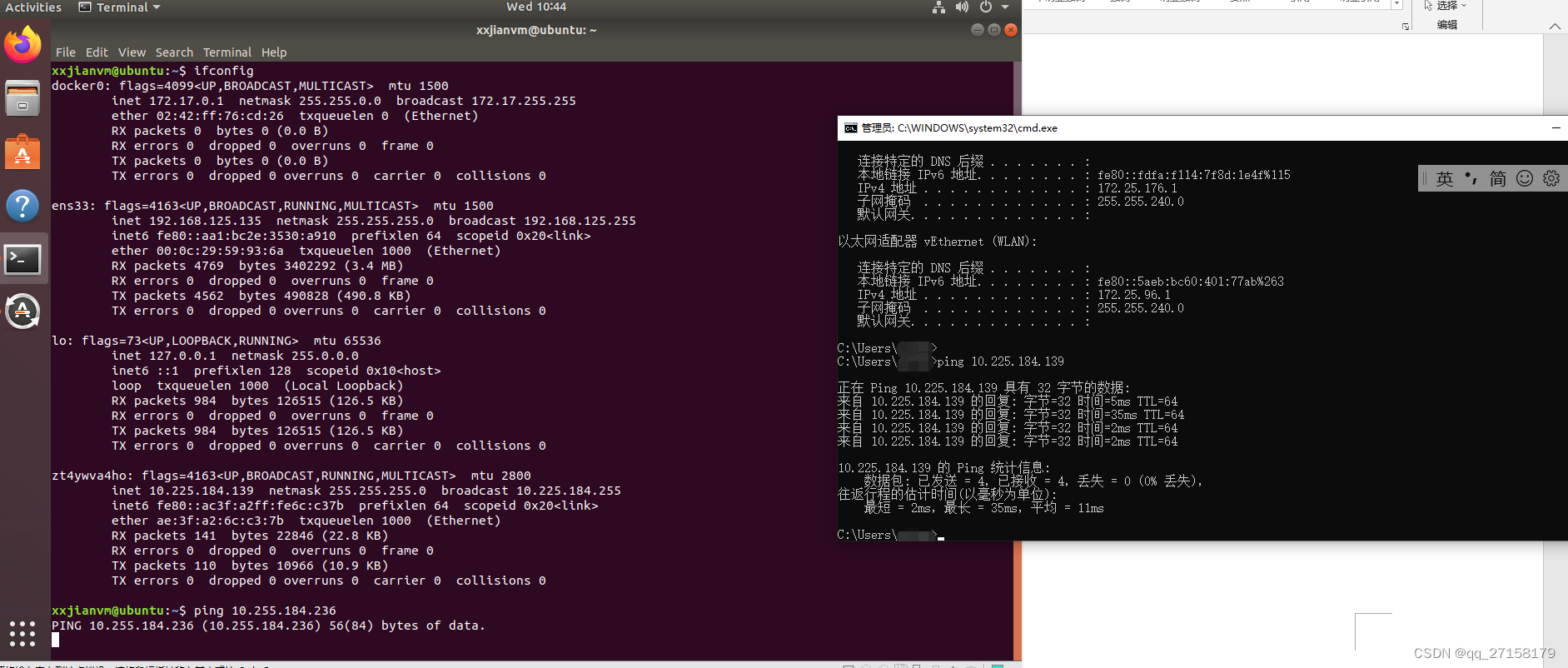

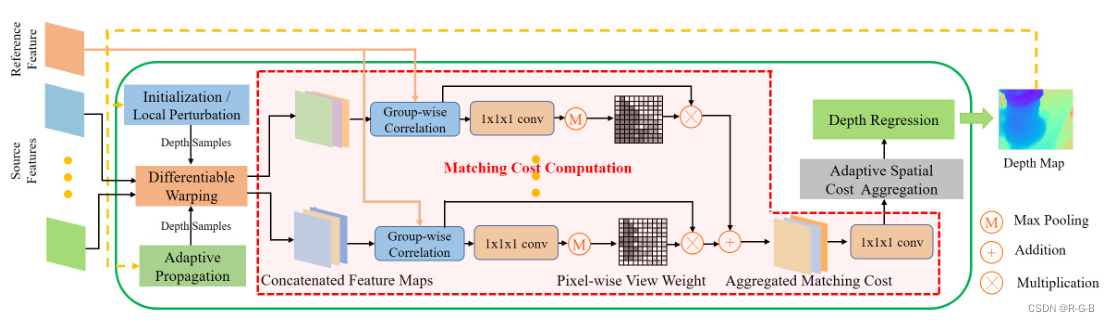

STMF4的FSMC灵活的静态存储控制器

概述

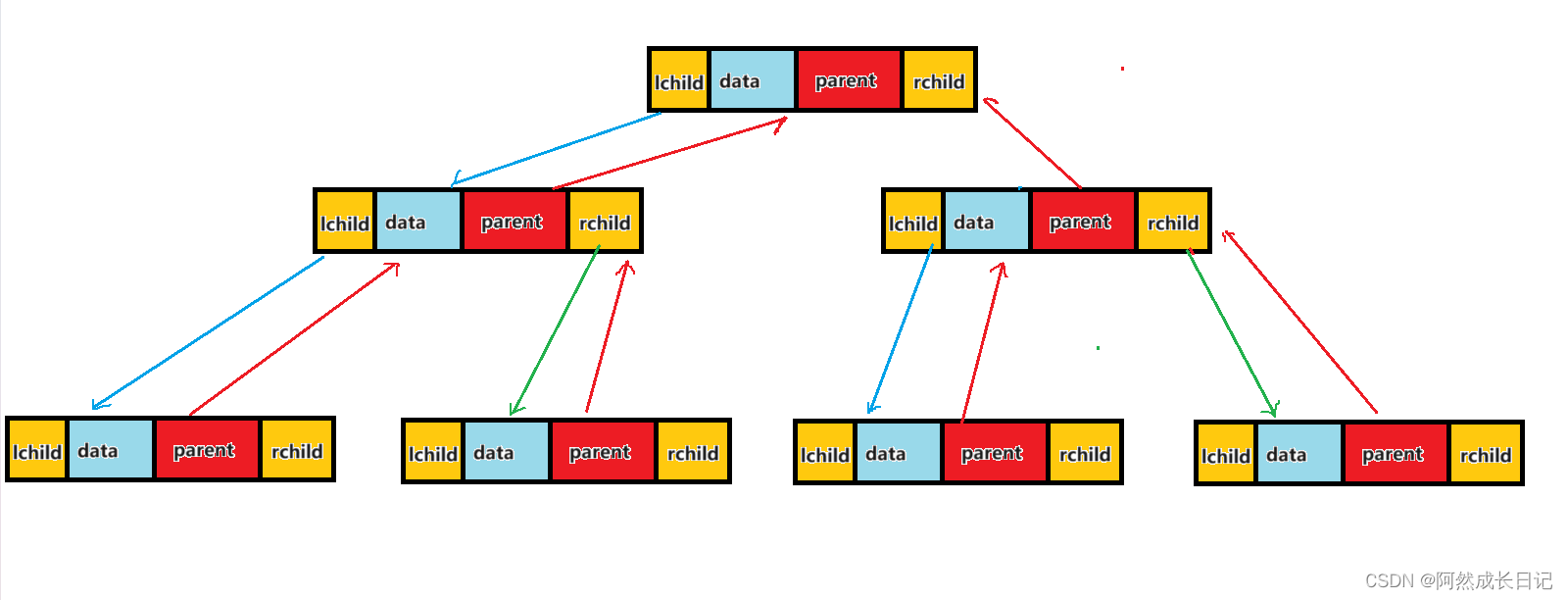

FSMC 包含四个主要模块:

● AHB 接口(包括 FSMC 配置寄存器)

● NOR Flash/PSRAM 控制器

● NAND Flash/PC 卡控制器

● 外部器件接口

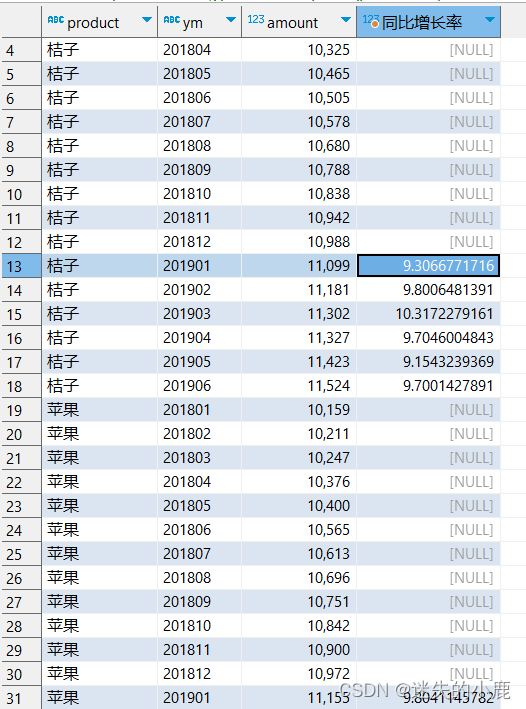

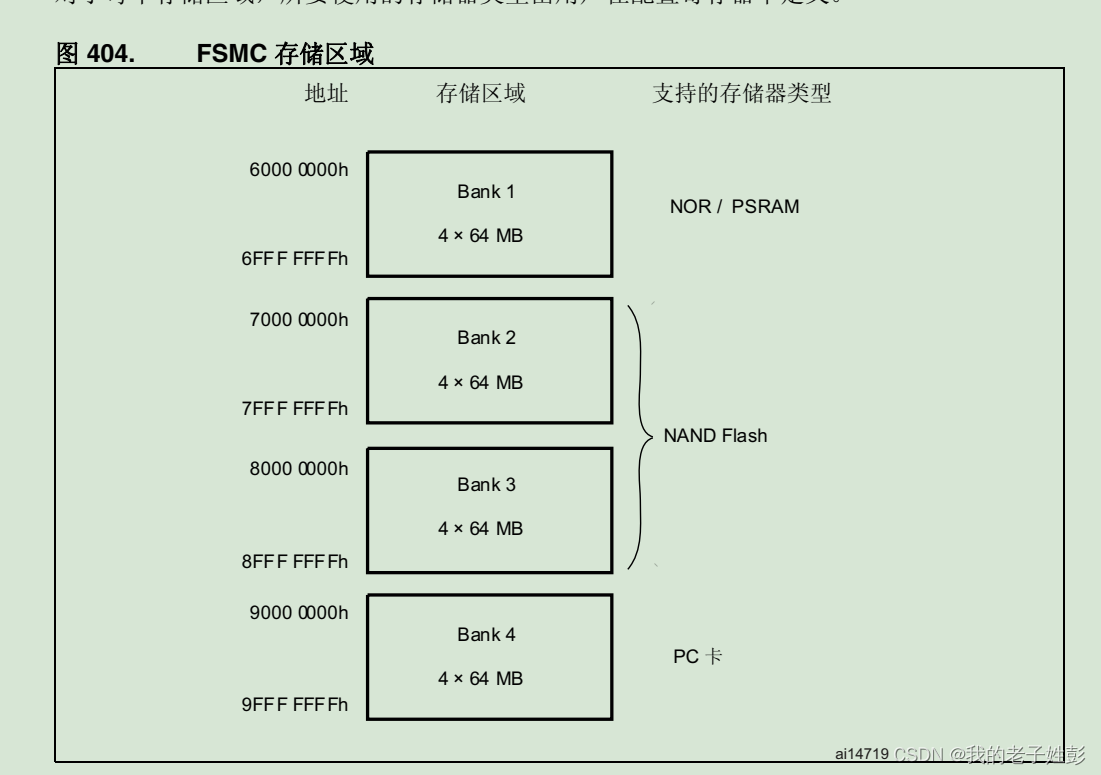

FSMC的存储区域

可以知道外扩SRAM的应该使用的地址范围为0x6000 0000 到0x6FFF FFFF,是FSMC存储区域的块1;

并且因为FSMC是AHB总线的延伸,所以由上可以直接访问地址操作,就可以读写外扩的SRAM

SRAM的接口表和引脚定义

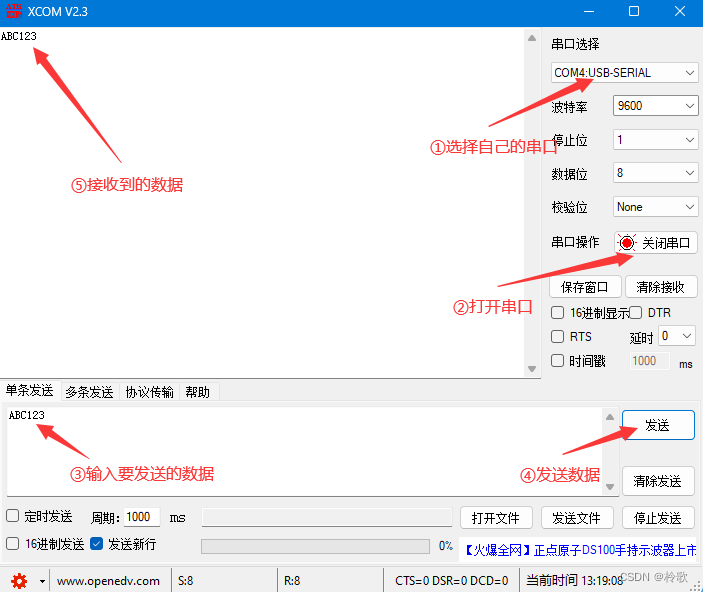

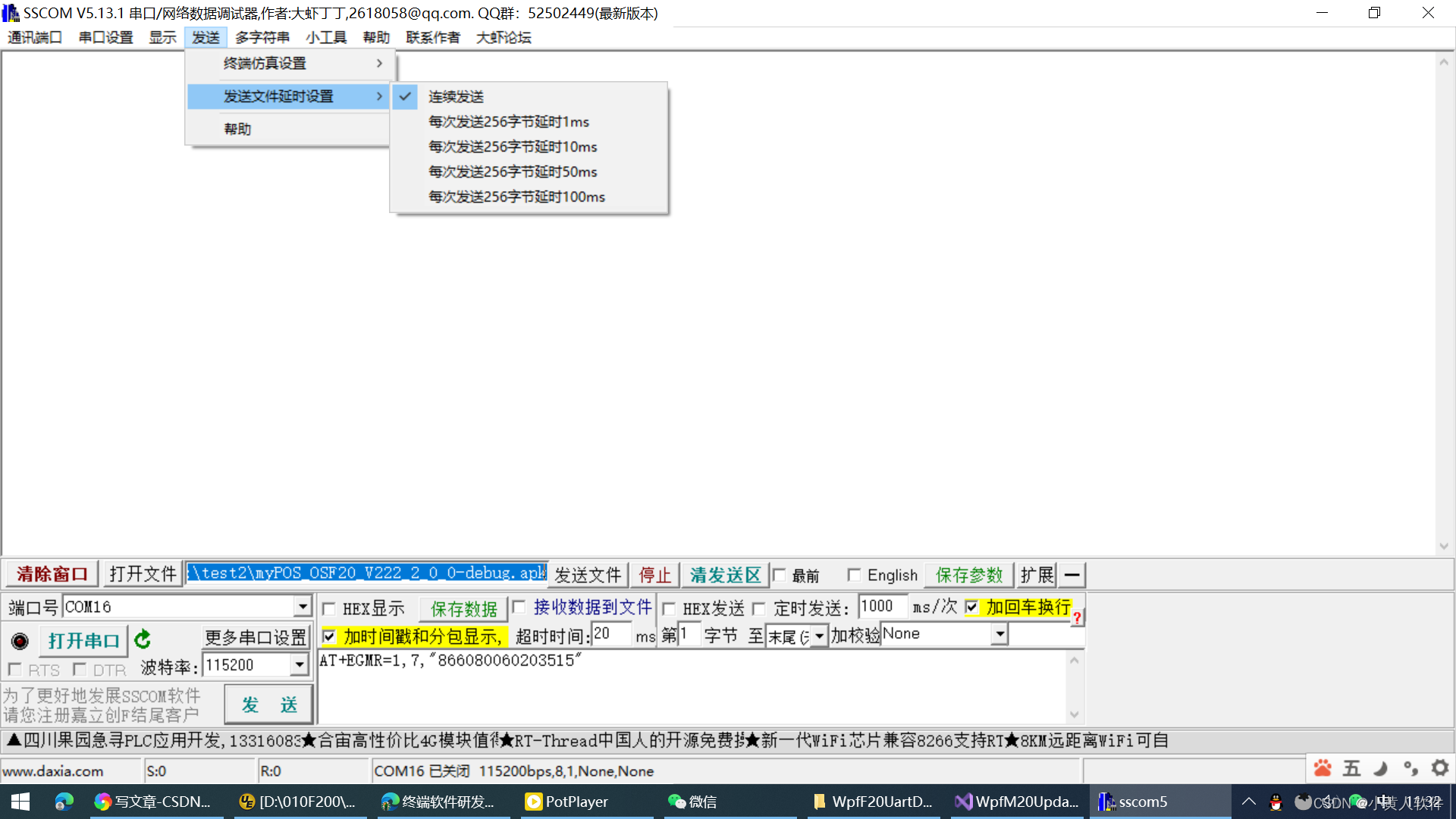

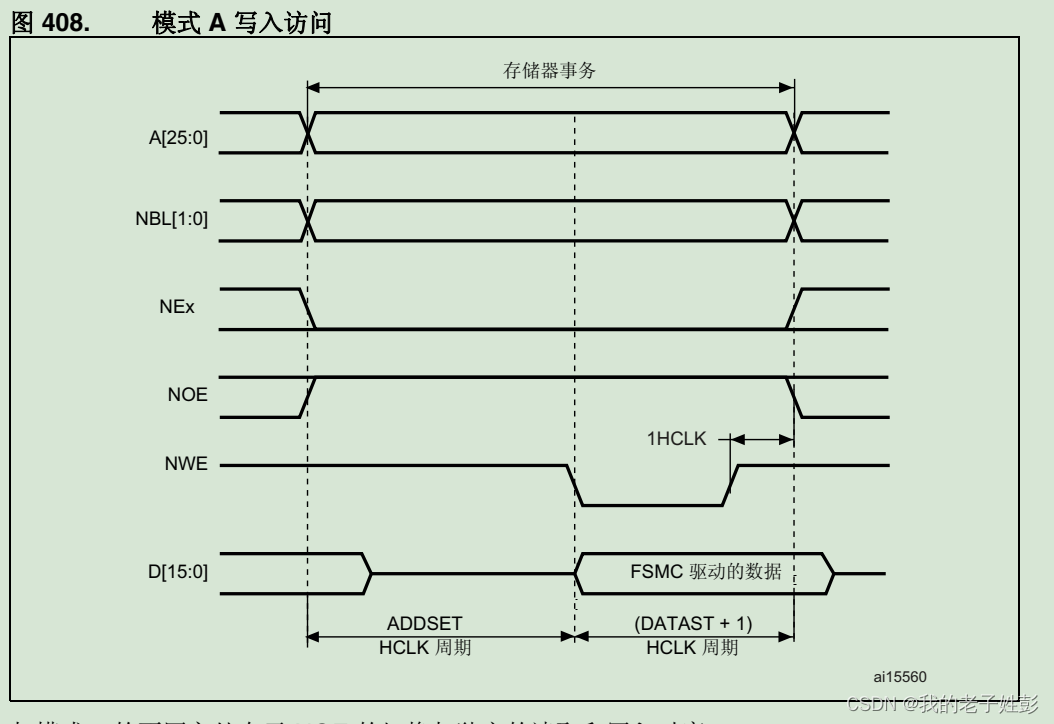

模式A

读取

NBL[1:0] 在进行读取访问时为低电平。

可以看出真个读取事物需要ADDSET 和DATAST时钟合

写入

可以看出整个读取事物需要ADDSET和DATAST+1个时钟周期