FPGA:卷积编码及维特比译码仿真

本篇记录一下在FPGA中完成卷积编码和维特比译码的过程,通过代码解释编码的过程和译码的过程,便于理解,同时也方便移植到其他工程中。

1. 准备工作

- 卷积编译码IP核—

convolutionIP核和viterbiIP核 - 卷积编码原理知识—网上有很多关于原理性的解释

- 卷积编码对照仿真过程—可以对照之前的MATLAB仿真程序便于更好的理解编译码的过程,但是有一点不同,在FPGA仿真代码中利用自然数编码,最后译码回自然数,方便对照正确性。

2. 编码过程

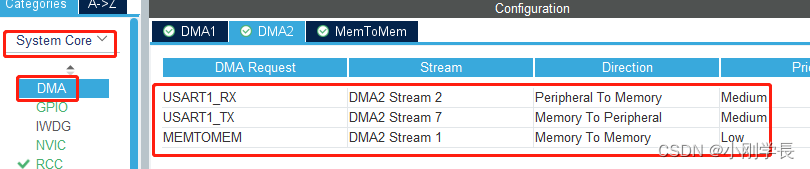

首先添加convolutionIP核,可以看到首先有如下的需要配置的参数。

按照上图的设置方式为2,1,7形式的卷积编码器,这个没有什么需要注意的,按照常规设置就可以了。

然后添加viterbiIP核,打开之后可以看到如下的设置参数。

在第一个Viterbi Type栏中可以可以选择Standard,然后约束长度和编码过程的设置一致,回溯深度可以利用公式计算5*(约束长度-1),这个是最小的设置的值,回溯深度至少要大于这个值。

在第二个配置页中,按照如下的参数进行设置,这个可以参考MATLAB仿真。

这个页面配置的传入的bit数据,因为编码设置的是2,1,7所以这个设置为2,

3. 仿真过程

整个仿真过程利用0-15的自然数循环,对其进行卷积编码,然后通过viterbi译码还原出原来的自然数。

程序的设置流程思路:

- 为了方便移植到其他的工程中,同时为了转换数据速率,在自然数信源和卷积编码中间添加了一个fifo

- 同样的操作,在译码结束之后添加了一个fifo,与前一个fifo对称。

- 在利用译码的过程中,有一点注意事项:编码之后的2bit数据输入到viterbi译码的IP核中时,需要在第0位和第8位填充,构成两bit。这个技术手册中有说明。

下面给出两个fifo的参数设置,自然数位宽为[0:3],首先是信源和编码之间的fifo。

然后是译码之后的fifo。

4. 完整代码

`timescale 1ns / 1psmodule conv_encoder(input clk, //时钟input rst_n // 复位 高电平复位);parameter K = 1; // 对应MATLAB仿真中的k和n的值,这个在IP核设置中已经有体现

parameter N = 2; //

parameter L = 7; // 编码之后的数据长度reg [5:0] datain_num; // 每一组编码的原始数据个数

reg [3:0] datain;

//reg [5:0] dataout_num; //输出编码数据的个数// 定义viterbi IP核需要用到的信号

wire vit_datain_valid; // 当vit ip的ready信号有效同时 conv的输出有效的时候,这个信号有效

wire vit_datain_ready; //

wire vit_dataout_valid;

wire vit_dataout_ready;

wire vit_data_out; // 译码结果输出// 信源处fifo的相关信号线,该fifo是用来把多位数转为比特流传入到卷积编码中。

wire fifo_encode_empty;

wire fifo_encode_full;

wire fifo_encode_out;

wire fifo_decode_empty;

wire fifo_decode_full;

wire [3:0] fifo_decode_out;wire rd_en; //第一个fifo的读写控制信号

wire wr_en;

reg wren;always@(posedge clk)beginif(~rst_n)beginwren <= 1'b0;endelse beginif(fifo_encode_full==1'b1)beginwren <= 1'b0;endelse beginwren <= 1'b1;endend

end

assign wr_en = wren & (!fifo_encode_full); // fifo没有满就往fifo中写数据

wire rd_en2; // 第二个fifo的读写控制信号

wire wr_en2;assign rd_en2 = !fifo_decode_empty; // 最后一个fifo 非空就可以读数据

assign wr_en2 = (!fifo_decode_full) & vit_dataout_valid;

assign vit_dataout_ready = 1'b1; // 最后直接进fifo了,这里不做特殊控制了,直接常为1,就可以仅看vit_dataout_valid信号了// 编码信号的控制型号 valid 和 ready

wire conv_datain_ready;

reg conv_datain_valid;

wire [1:0] conv_dataout;

wire conv_dataout_valid;

wire conv_dataout_ready;// 设计输入数据 这里面需要对输入的数据转化弄成位的形式,

// 这个和卷积编码的参数设置有关,2,1,7,接受一个输入bit生成两个bitalways@(posedge clk)beginif(~rst_n)begindatain <= 4'b0;datain_num <= 6'b0;endelse beginif(wr_en == 1'b1)begin // 数据只在wr_en有效的情况下才逐渐累加,这个是为了通过连续的数值检验译码正确性datain <= datain + 4'b1;datain_num <= datain_num + 6'b1;endelse begindatain <= datain;datain_num <= datain_num;endend

end// 在这里添加转换bit 可以用fifo实现,同时能够控制速率 assign rd_en = conv_datain_ready;

fifo_encode u1 (.clk(clk), // input wire clk.srst(~rst_n), // input wire srst.din(datain), // input wire [3 : 0] din.wr_en(wr_en), // input wire wr_en.rd_en(rd_en), // input wire rd_en.dout(fifo_encode_out), // output wire [0 : 0] dout.full(fifo_encode_full), // output wire full.empty(fifo_encode_empty)

);always@(posedge clk)beginif(~rst_n)beginconv_datain_valid <= 1'b0;endelse beginconv_datain_valid <= rd_en;end

endassign conv_dataout_ready = 1'b1;convolution_0 conv (.aclk(clk), // input wire aclk.aresetn(rst_n), // input wire aresetn.s_axis_data_tdata(fifo_encode_out), // input wire [7 : 0] s_axis_data_tdata 注意这个只能接受1bit有效数据.s_axis_data_tvalid(conv_datain_valid), // input wire s_axis_data_tvalid.s_axis_data_tready(conv_datain_ready), // output wire s_axis_data_tready.m_axis_data_tdata(conv_dataout), // output wire [7 : 0] m_axis_data_tdata.m_axis_data_tvalid(conv_dataout_valid), // output wire m_axis_data_tvalid.m_axis_data_tready(conv_dataout_ready) // input wire m_axis_data_tready

);assign vit_datain_valid = conv_dataout_valid & conv_dataout_ready;// 编码完成后进行译码过程

viterbi_0 viterbi (.aclk(clk), // input wire aclk.aresetn(rst_n), // input wire aresetn.s_axis_data_tdata({7'b0,conv_dataout[1],7'b0,conv_dataout[0]}), // input wire [15 : 0] s_axis_data_tdata 这个经过编码之后的数据需要按照此种方式输入。.s_axis_data_tvalid(vit_datain_valid), // input wire s_axis_data_tvalid.s_axis_data_tready(vit_datain_ready), // output wire s_axis_data_tready.m_axis_data_tdata(vit_data_out), // output wire [7 : 0] m_axis_data_tdata.m_axis_data_tvalid(vit_dataout_valid), // output wire m_axis_data_tvalid.m_axis_data_tready(vit_dataout_ready) // input wire m_axis_data_tready

);// 添加一个把数据恢复成自然数的fifo

fifo_decode u2 (.clk(clk), // input wire clk.srst(~rst_n), // input wire srst.din(vit_data_out), // input wire [3 : 0] din.wr_en(wr_en2), // input wire wr_en.rd_en(rd_en2), // input wire rd_en.dout(fifo_decode_out), // output wire [0 : 0] dout.full(fifo_decode_full), // output wire full.empty(fifo_decode_empty) // output wire empty

);endmodule下面为tb文件:

`timescale 1ns / 1psmodule conv_tb();reg l_clk;

reg rst_n;conv_encoder conv_test_ins(.clk(l_clk), //时钟.rst_n(rst_n) // 复位 高电平复位

// input [7:0] data_in, // 输入的待编码数据

// output [7:0] dataout // 输出的解码数据);initial l_clk = 1;

always #5 l_clk= !l_clk; //15.625 initial beginrst_n <= 0;#40;rst_n <= 1;#320;//#50000000;#320;

// $stop;

end

endmodule5. 结果分析

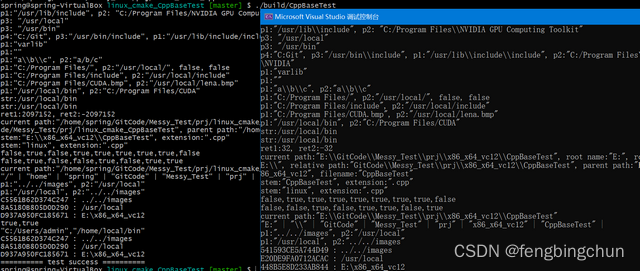

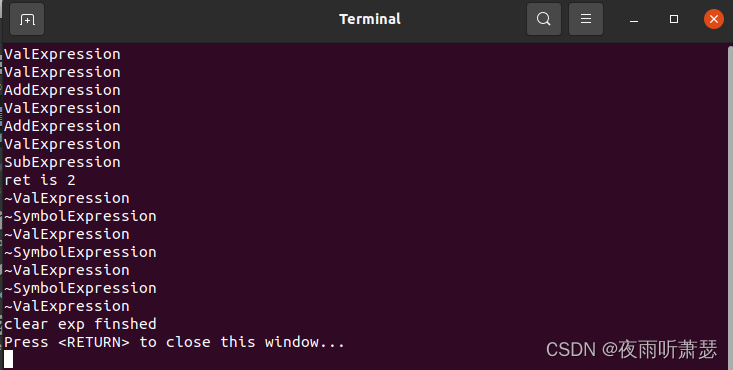

以下为仿真结果图:

最下面的红色线是译码之后经过fifo速率转换之后的结果,可以看到是从0依次递增的自然数,一直到15,然后循环下去。这个有效是和rd_en2这个信号保持一致的,但是看这组红线,译码的结果是两个0,这是因为fifo读数据的时候是有一个clk的时钟延时的,这也是为什么在给出fifo参数设置的时候把latency=1用红线框起来。所以把rd_en2延迟一个系统时钟对照fifo_decode_out看数据就正确了。在使用的时候看接下来数据处理的过程需求,采用合适的操作,这里只做简单的仿真验证。