本文验证乘法器IP核Multiplier进行无符号(unsigned)与有符号数(signed)相乘的正确性,其中也遇到了一些问题,做此记录。

配套工程:https://download.csdn.net/download/weixin_48412658/88354179

文章目录

- 问题的讨论

- 验证过程

- IP核配置

- 例化乘法器

- 仿真代码

- 仿真波形分析与结论

- 补充:vivado乘法器IP核简单调用

问题的讨论

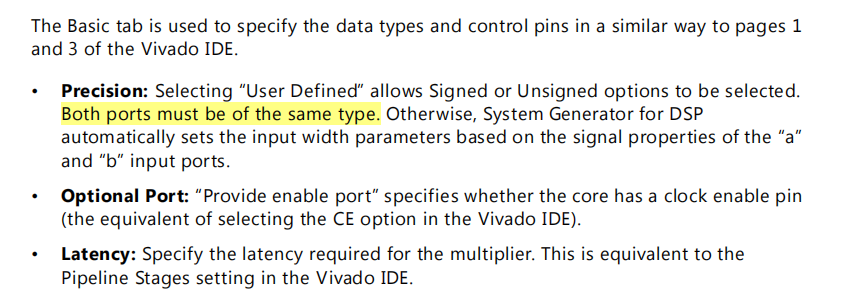

在IP核手册中提到pg108-mult-gen.pdf>,两端口的类型必须一致。进行验证后发现AB的数据类型不一致时也能够计算出正确的输出值,是否意味着两端口类型可以不一致进行计算啦?

验证过程

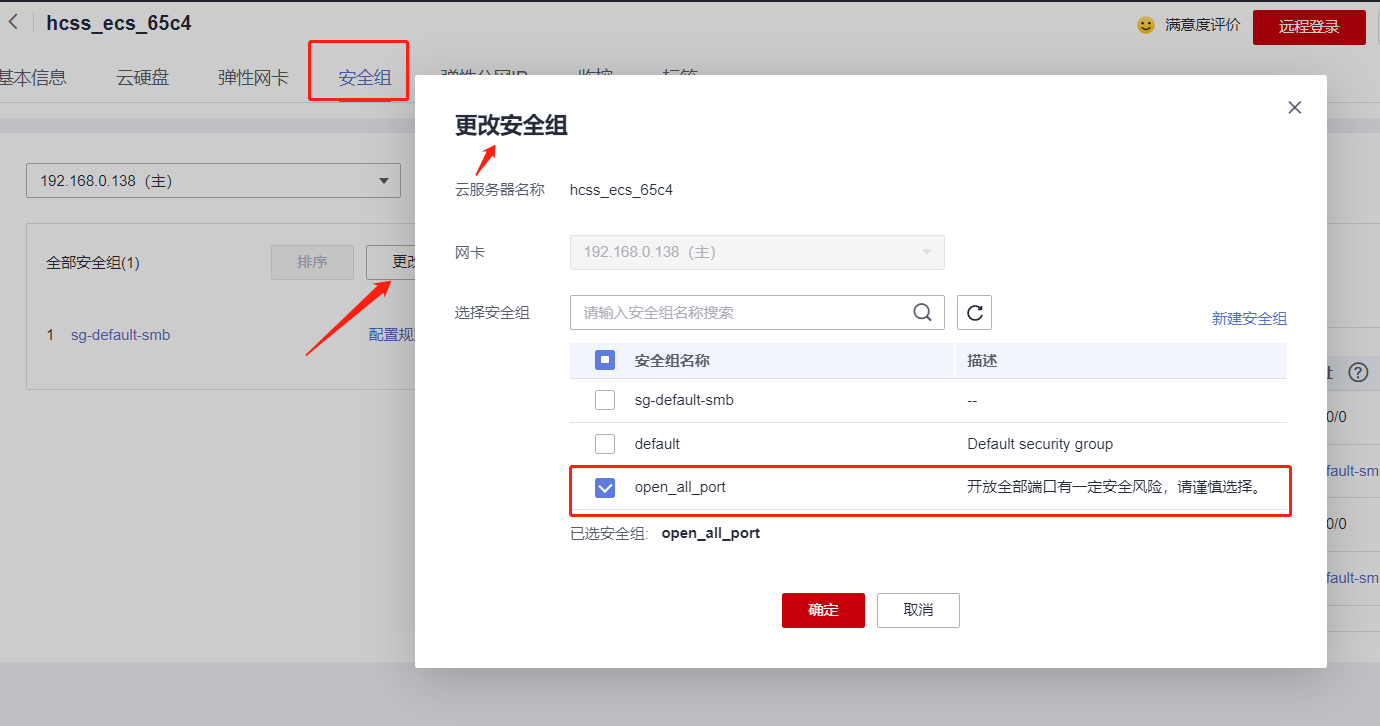

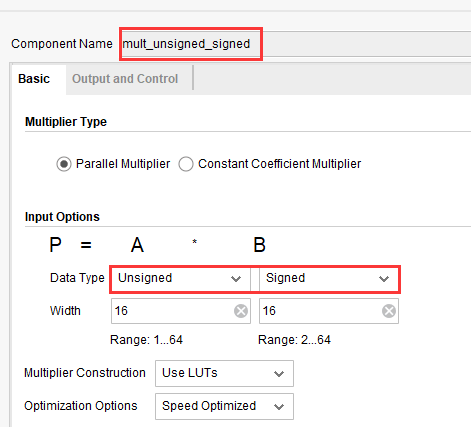

IP核配置

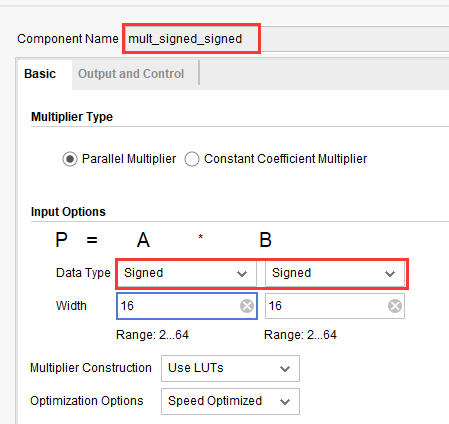

首先配置两个乘法器IP核:

第一个是有符号的相乘。

第二个是有无符号与有符号的相乘。

例化乘法器

变量输入类型:

reg signed [15 : 0] A_sig;

reg [15 : 0] A_unsig;reg signed [15 : 0] B_sig; //例化中B始终是有符号类型//输出

wire signed [31 : 0] P_sig;wire [31 : 0] P_unsig;

wire signed [31 : 0] P_sig2; //用于mult_unsigned_signed IP核

设置初始值:

A_sig = 16'b1101_1101_1101_1101;A_unsig = 16'b1101_1101_1101_1101;B_sig = -50;

例化中前第一个使用的是第一个IP核,第二三个使用的是第二个IP核。

//例化待测设计

mult_signed_signed mult_signed_signedi (.CLK(sys_clk), .A(A_sig), .B(B_sig), .P(P_sig)

);mult_unsigned_signed mult_unsigned_signed1 (.CLK(sys_clk), .A(A_unsig), .B(B_sig), .P(P_unsig) //将输出赋值给P_unsig

);mult_unsigned_signed mult_unsigned_signed2 (.CLK(sys_clk), .A(A_unsig), .B(B_sig), .P(P_sig2) //将输出赋值给P_sig2

);

仿真代码

`timescale 1ns / 1ps

//

// Module Name: tb_mult

//

module tb_mult();//输入

reg sys_clk;

reg signed [15 : 0] A_sig;

reg [15 : 0] A_unsig;

reg signed [15 : 0] B_sig;//输出

wire signed [31 : 0] P_sig;wire [31 : 0] P_unsig;

wire signed [31 : 0] P_sig2; //用于mult_unsigned_signed IP核

//信号初始化

initial beginsys_clk = 1'b1;A_sig = 16'b1101_1101_1101_1101;A_unsig = 16'b1101_1101_1101_1101;B_sig = -50;

end//生成时钟

always #10 sys_clk = ~sys_clk;initial begin#10forever begin#(100);A_sig = A_sig + 1'b1;B_sig = B_sig + 1'b1;end

endinitial begin#10 forever begin#(100);A_unsig = A_unsig + 1'b1;end

end

//例化待测设计

mult_signed_signed mult_signed_signedi (.CLK(sys_clk), .A(A_sig), .B(B_sig), .P(P_sig)

);mult_unsigned_signed mult_unsigned_signed1 (.CLK(sys_clk), .A(A_unsig), .B(B_sig), .P(P_unsig) //将输出赋值给P_unsig

);mult_unsigned_signed mult_unsigned_signed2 (.CLK(sys_clk), .A(A_unsig), .B(B_sig), .P(P_sig2) //将输出赋值给P_sig2

);endmodule

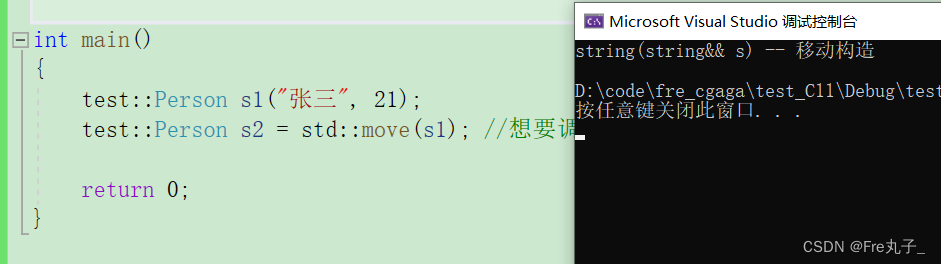

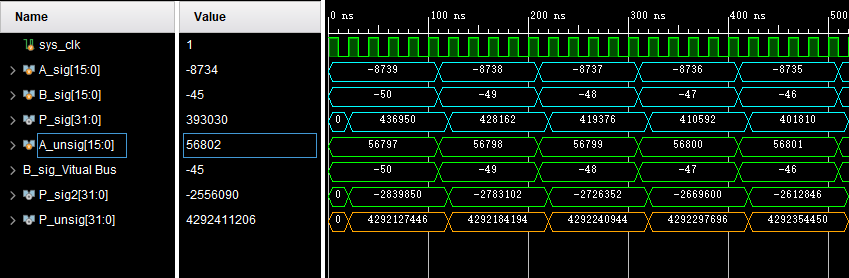

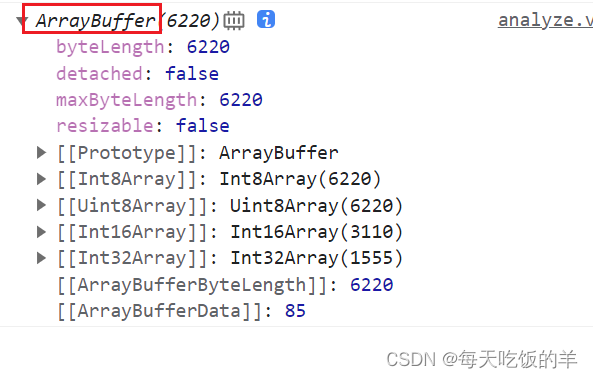

仿真波形分析与结论

波形中的进制Radix均根据是sig还是unsig设置成对应的进制。

可以看出:

有符号(signed)与有符号数(signed)相乘,输出赋值给有符号能得到正确输出。

无符号(unsigned)与有符号数(signed)相乘,输出赋值给有符号能得到正确输出。

无符号(unsigned)与有符号数(signed)相乘,输出赋值给无符号得到错误的输出,实质上将P_unsig的进制设置成signed的显示时则和P_sig2相同,表示两种是补码的关系。

通过试验可以验证无符号(unsigned)与有符号数(signed)相乘的乘法器IP核输出的值赋值给有符号数时能够计算正确。

补充:vivado乘法器IP核简单调用

vivado乘法器IP核简单调用:https://blog.csdn.net/Master_0_/article/details/123694290

![[C++ 网络协议] I/O流分离所带来的半关闭问题](https://img-blog.csdnimg.cn/633ae9c2908b43e28de2a608cca4cc8a.png)