课程链接:

计算机组成_北京大学_中国大学MOOC(慕课)

7 - 2 - 702-DRAM和SRAM(13-'22-'-')_哔哩哔哩_bilibili

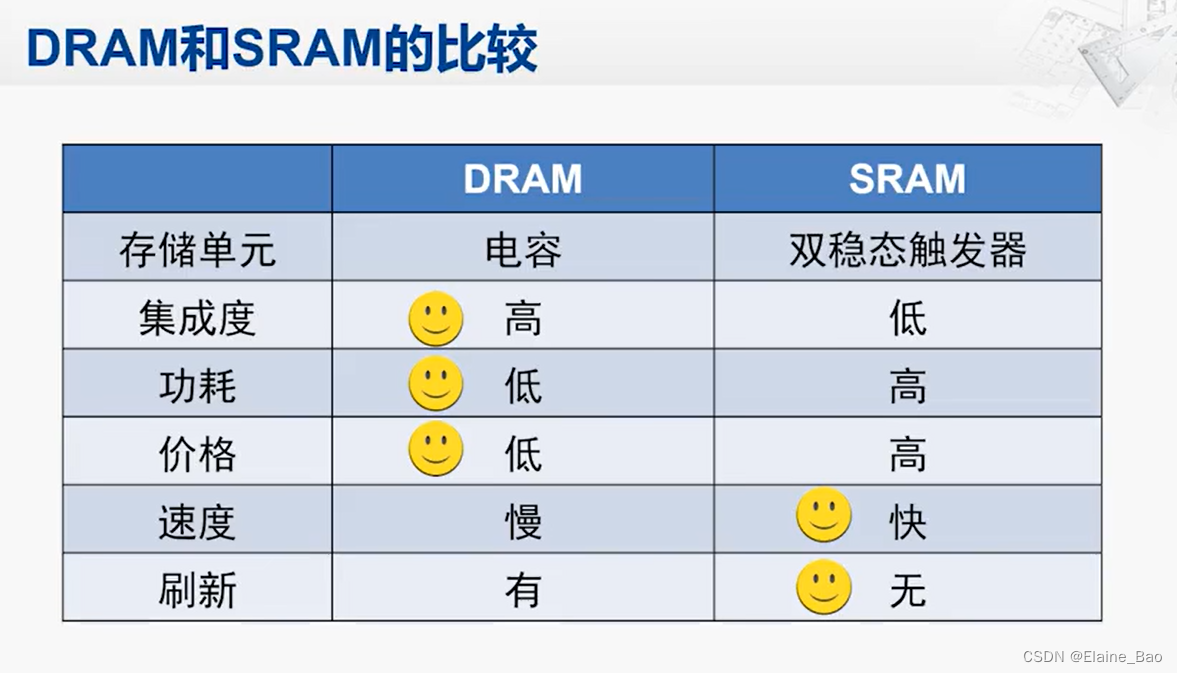

从【计算机组成 课程笔记】7.1 存储层次结构概况_Elaine_Bao的博客-CSDN博客中,我们了解到:SRAM比较快,DRAM比较慢,SRAM比较贵,DRAM比较便宜。记住这些结论是很容易的, 但是比是什么更重要的是为什么,这一节我们就从电路的级别来探索DRAM和SRAM为什么会具有它们这样各自的特点。

DRAM

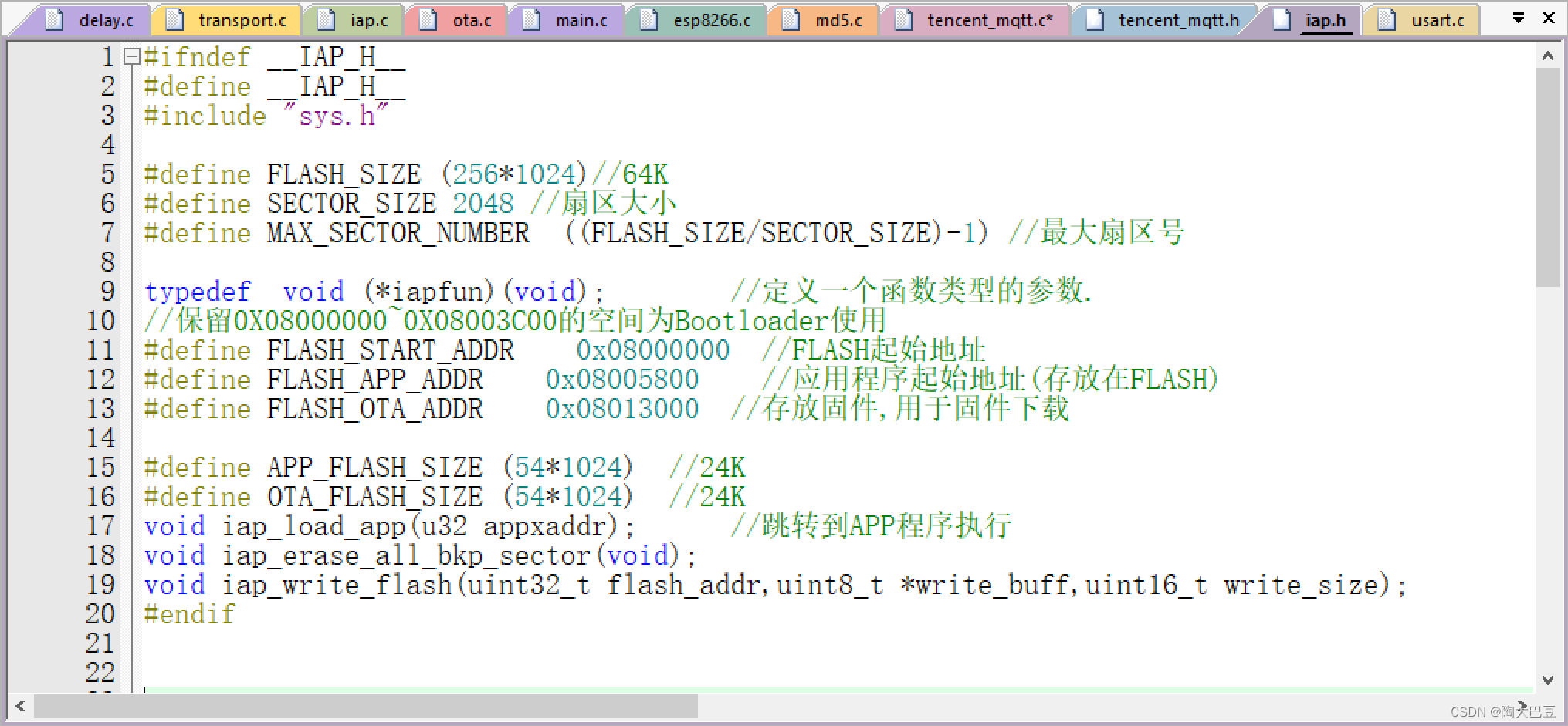

这是我们计算机中使用的内存条,准确的说叫内存模组,图中这个内存模组中共有8块DRAM芯片。

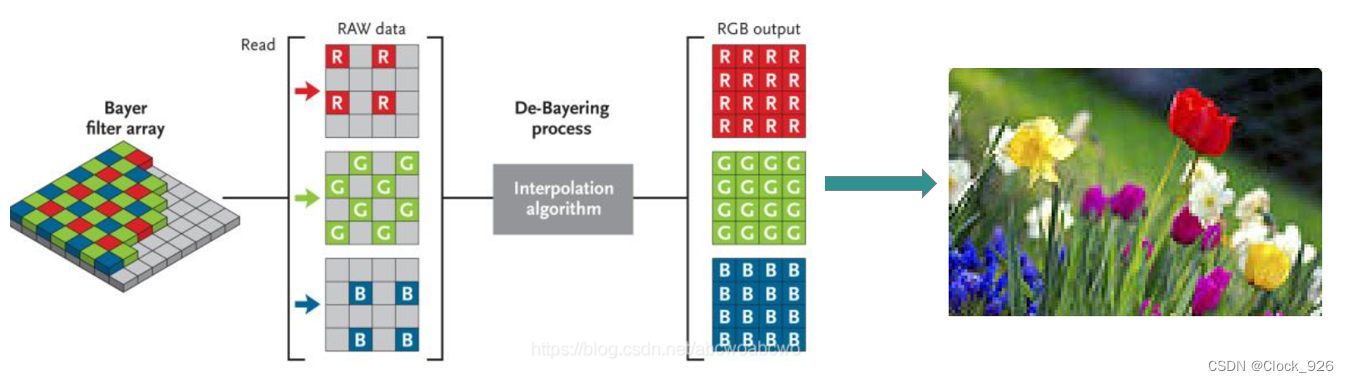

DRAM芯片内部的核心结构就是这个存储阵列,由若干行、若干列构成。如果外部给定行地址和列地址,DRAM中有地址译码逻辑电路,能够选中一个存储单元,而每个存储单元往往包含若干个比特,常见的有4比特和8比特。每个比特都采用如下的电路结构,称为DRAM的基本存储单元。

DRAM的基本存储单元(1bit)

这个基本单元就是通过一个电容来保存一个比特的信息。写入就是由外部的数据线驱动对电容进行充电或者放电的操作,从而完成写入0或1,读操作则是由电容对外部的数据信号线进行驱动,从而完成读出0或1。

这个电路结构非常简单,但是我们要注意,电容是存在漏电效应的,如果经过一段时间,电容上的电荷流失过多,我们就会丢失它所存的信息。因此,为了保证DRAM的存储信息的正确性,我们需要定期对所有的单元进行“刷新”。如果初始保存的数据是0,则通过刷新使它保持无电荷状态,如果原先保存的数据为1,则补充这个电容的电荷。这就是DRAM的基本结构和运行原理。

DRAM的特点和主要用途

现在PC机中大多是采用DRAM作为主存储器,也就是内存。当然,DRAM也有很多种不同的实现,比如SDRAM,这个S是同步的缩写,它是在DRAM的基本结构基础上,对输入输出接口进行时钟同步,从而提高了读写的效率。而现在更为常用的内存,则是在SDARAM的基础上又进行了进一步的改进,比如说这些年有DDR1,DDR2,DDR3, 这些不同的内存标准都是在SDRAM的基础上进行的改进和升级。

总体来说,由于每个DRAM的基本存储单元非常简单,所以能做到很高的集成度,而且功耗也比较低,我们可以用较低的成本制造大容量的DRAM芯片。当然它的缺点也跟它的这个结构有关,因为采用了电容充放电的方式,所以DRAM的读写速度还是比较慢的,而且它还需要定期刷新,这进一步影响了DRAM的读写性能。

SRAM

那么与DRAM相对的,还有一种常用的存储部件,就是SRAM。我们先来看看SRAM的基本结构。

SRAM的基本存储单元(1bit)

SRAM的基本存储单元共有6个晶体管构成,我们分别用M1~M6表示,这6个晶体管合在一起才可以保存一个比特,显然比DRAM的结构要复杂得多。

这个基本存储单元对外有3个接口信号,其中BL、~BL用于传送读写数据信息,WL用于控制外部是否可以访问这个存储单元。

下面通过读写的实例来看看SRAM是如何工作的。

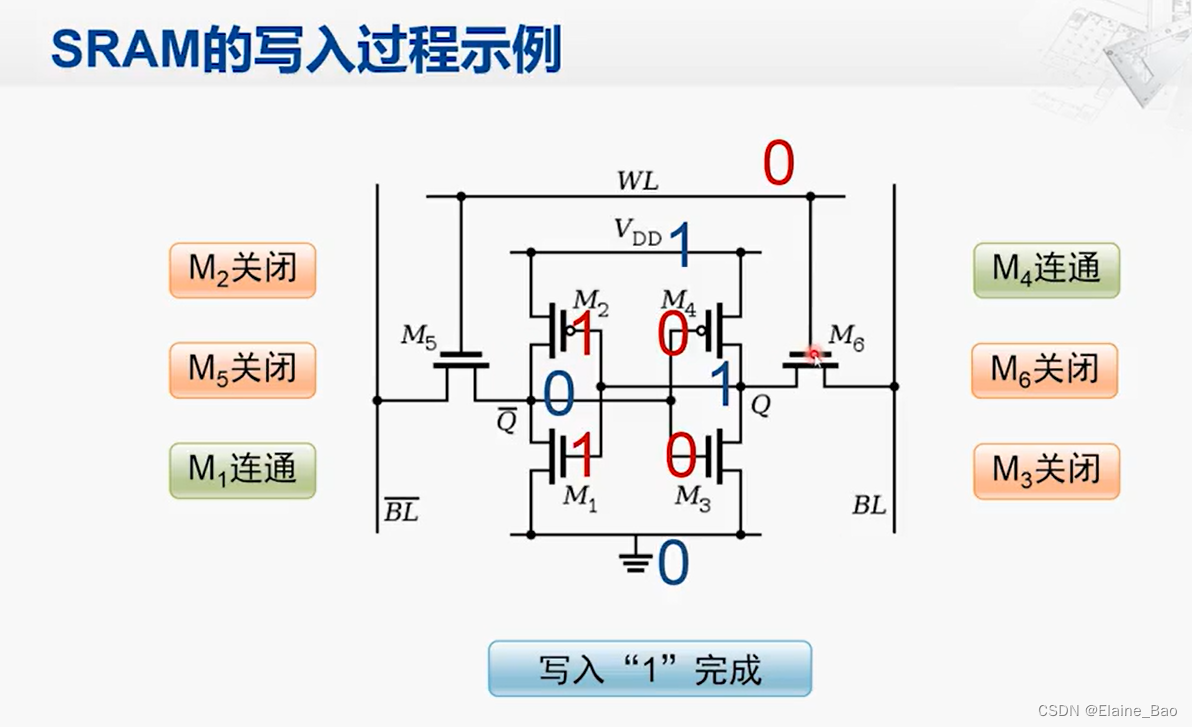

SRAM的写入过程示例

以写入数据1为例进行分析。

- 首先,这个存储单元中连接了电源和地,分别代表1和0。只要SRAM处于通电状态,VDD和地的信号的值都会保持稳定,为1和0。

- 如果要写入1,则将BL置为1,与之相对~BL则为0,这样就准备好了要写入的数据。

- 然后我们需要访问这个SRAM单元,就要将WL置为1。WL信号为1,则M5、M6两个晶体管的gate端也为1。由于M5和M6都是NMOS晶体管,当NMOS晶体管的gate端为1时,它是处于连通状态的。因此BL上的值就会通过M6传递进来,则Q信号为1,类似的,~Q信号为0。

- Q信号控制了M2晶体管的gate端,它是一个PMOS晶体管,当PMOS晶体管的gate端为1时,它是处于关闭状态的,所以VDD的信号不会被传到~Q,与步骤3中由~BL信号传递进来的0是一致的。类似的,Q信号还控制了M1晶体管,则它处于连通状态。M3和M4被~Q信号控制,分别处于关闭和连通状态,此时VDD的信号传到Q,与步骤3中由BL信号传递进来的1也是没有冲突的。

这样由外部的BL和~BL输入的信号就驱动了这个SRAM的存储单元的晶体管达到了一个稳定的状态。因为晶体管的工作速度很快,所以SRAM的写入过程也很快,当这几个晶体管达到稳定后,写入过程就结束了。

现在我们可以撤销WL信号了(由1变0),从而将M5、M6两个晶体管关闭。然后撤销BL和~BL的信号,那在外部的信号撤销之后,因为M5和M6都关闭了,所以并不是由外部的信号驱动M2和M1这两个晶体管的gate端,但是由于在刚才写入的过程中,M4晶体管处于连通状态,所以电源传导的这个1会始终驱动M2和M1的gate端保持为1。而只要M2和M1的gate端保持为1,由地传导过来的0又会反过来驱动M4和M3的gate端为0。那么在这4个晶体管的相互作用下,SRAM就保持住了刚才写入的1。只要WL信号保持为0,这个存储单元就会始终保持住之前存储的信号,当然前提是要保持通电的状态。

SRAM的读出过程示例

以读取刚才写入的数据1为例。

- 首先把WL信号置为1,这样M5、M6两个晶体管都会处于连通的状态。

- 此时外部并不驱动BL和~BL,因此它们会通过M5、M6被SRAM驱动。

- BL被驱动为1,~BL被驱动为0,这样读出1的过程就完成了。

这就是SRAM基本存储单元的结果和工作原理。

SRAM的特点和主要用途

如果我们把很多个这样的存储单元组合在一起,就可以构成一个存储矩阵,从外部可以输入若干的地址线,通过增加一些地址译码的驱动电路,就可以根据地址线的值选中存储矩阵当中对应的若干个存储单元,再通过读写控制,就可以将存储单元和数据线进行连通。

由此看来,因为晶体管的开关速度远比电容充放电速度快,所以相对于DRAM,SRAM更快。但是我们也看到,SRAM中每存储一个比特就需要6个晶体管,晶体管数量多会造成芯片面积大,从而带来集成度和价格高的问题。同时每个晶体管都是要耗电的,晶体管越多功耗就越高,这些都是SRAM的缺点。

那现代CPU中的高速缓存都是用SRAM实现的。比如这就是一颗4核CPU的版图,在这个芯片当中,这些大面积的看起来非常规整的电路,实际上都是SRAM。所以仅从制造成本上来看,这些作为高速缓存的SRAM往往要占到整个CPU的一半或者更多。而且由于高速缓存大多采用和CPU相当的时钟频率,所以它们的功耗也非常高。

DRAM和SRAM的比较

![[架构之路-228]:目标系统 - 纵向分层 - 计算机硬件与体系结构 - 硬盘存储结构原理:如何表征0和1,即如何存储0和1,如何读数据,如何写数据(修改数据)](https://img-blog.csdnimg.cn/img_convert/ec8a420edd3c717b8212414255d52239.png)