名称:数字秒表VHDL精度毫秒可回看

软件:Quartus

语言:VHDL

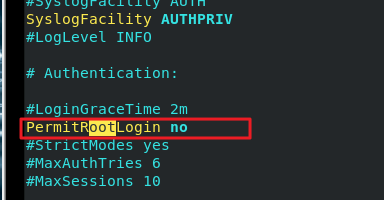

代码功能:

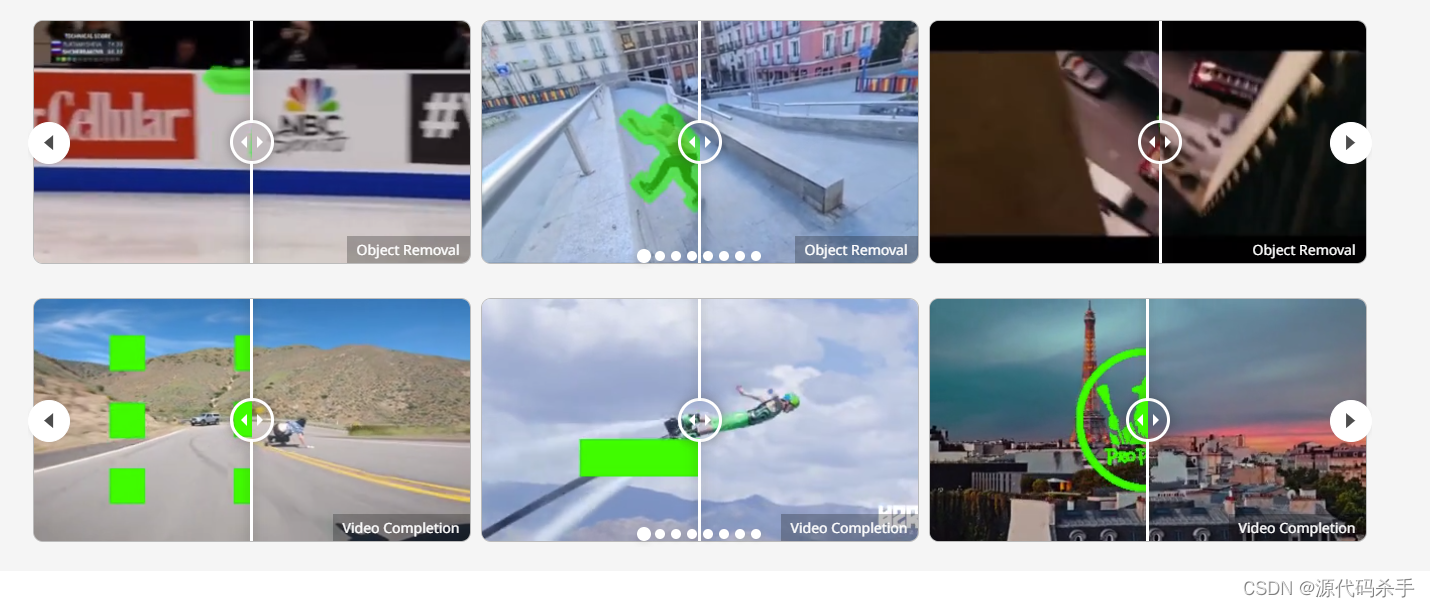

数字秒表的VHDL设计,可以显示秒和毫秒。可以启动、停止、复位。要求可以存储6组时间,可以回看存储的时间

本资源内含2个工程文件,两个工程文件功能相同,均能实现上述数字秒表功能,但是代码实现方式不同,详见下述设计文档_1和设计文档_2.

本代码已在实验箱验证,实验箱资料:

实验电路结构图及芯片引脚对应表(1).doc

演示视频:数字秒表VHDL实验箱验证精度毫秒可回看_Verilog/VHDL资源下载

FPGA代码资源下载网:hdlcode.com

代码下载:

数字秒表VHDL实验箱验证精度毫秒可回看_Verilog/VHDL资源下载名称:数字秒表VHDL精度毫秒可回看(代码在文末付费下载)软件:Quartus语言:VHDL代码功能: 数字秒表的VHDL设计,可以显示秒和毫秒。可以启动、停止、复位。要求可以存储6组时间,可以回看存储的时间 本资源内含2个工程文件,两个工程文件功能相同,均能实现上述数字秒表功能,但是代码实现方式不同,详见下述设计文档_1和设计文档_2. 本代码已在实验箱验证,实验箱资料:实验电![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=199

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=199

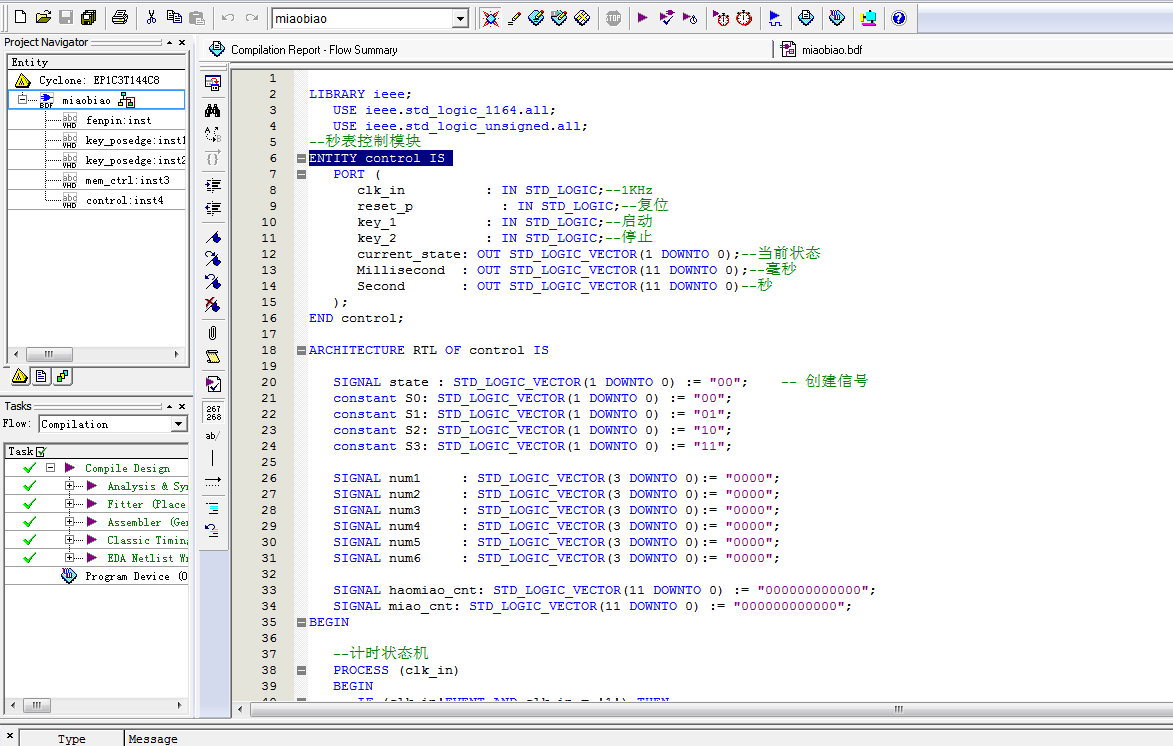

部分代码展示

LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_unsigned.all; --秒表控制模块 ENTITY control ISPORT (clk_in : IN STD_LOGIC;--1KHzreset_p : IN STD_LOGIC;--复位key_1 : IN STD_LOGIC;--启动key_2 : IN STD_LOGIC;--停止current_state: OUT STD_LOGIC_VECTOR(1 DOWNTO 0);--当前状态Millisecond : OUT STD_LOGIC_VECTOR(11 DOWNTO 0);--毫秒Second : OUT STD_LOGIC_VECTOR(11 DOWNTO 0)--秒); END control; ARCHITECTURE RTL OF control ISSIGNAL state : STD_LOGIC_VECTOR(1 DOWNTO 0) := "00"; -- 创建信号 constant S0: STD_LOGIC_VECTOR(1 DOWNTO 0) := "00";constant S1: STD_LOGIC_VECTOR(1 DOWNTO 0) := "01";constant S2: STD_LOGIC_VECTOR(1 DOWNTO 0) := "10";constant S3: STD_LOGIC_VECTOR(1 DOWNTO 0) := "11";SIGNAL num1 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000";SIGNAL num2 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000";SIGNAL num3 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000";SIGNAL num4 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000";SIGNAL num5 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000";SIGNAL num6 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000";SIGNAL haomiao_cnt: STD_LOGIC_VECTOR(11 DOWNTO 0) := "000000000000";SIGNAL miao_cnt: STD_LOGIC_VECTOR(11 DOWNTO 0) := "000000000000"; BEGIN--计时状态机PROCESS (clk_in)BEGINIF (clk_in'EVENT AND clk_in = '1') THENIF (reset_p = '1') THEN--按下复位state <= S3;--复位状态ELSECASE state ISWHEN S3 =>--复位状态state <= S0;WHEN S0 =>--空闲状态IF (key_1 = '1') THEN--按下启动state <= S1;ELSEstate <= S0;END IF;WHEN S1 =>--计时状态IF (key_2 = '1') THEN--按下停止state <= S2;ELSEstate <= S1;END IF;WHEN S2 =>--停止状态state <= S2;WHEN OTHERS =>END CASE;END IF;END IF;END PROCESS;PROCESS (clk_in)BEGINIF (clk_in'EVENT AND clk_in = '1') THENIF (reset_p = '1') THEN--复位num1 <= "0000"; num2 <= "0000"; num3 <= "0000"; num4 <= "0000"; num5 <= "0000"; num6 <= "0000";ELSIF (state = S1) THEN--计时状态 if(num6="0010" and num5="0100" and num4="0000" and num3="0000" and num2="0000" and num1="0000")then num1 <= num1; num2 <= num2; num3 <= num3; num4 <= num4; num5 <= num5; num6 <= num6; elsif num1="1001" then num1<="0000"; --此IF语句完成个位十进制计数 if num2="1001" then num2<="0000"; --此IF语句完成十位十进制计数 if num3="1001" then num3<="0000"; --此IF语句完成百位十进制计数 if num4="1001" then num4<="0000"; --此IF语句完成千位十进制计数 if num5="1001" then num5<="0000"; --此IF语句完成万位十进制计数 if num6="1001" then num6<="0000"; --此IF语句完成十万位十进制计数 else num6<=num6+"0001"; end if; else num5<=num5+"0001"; end if; else num4<=num4+"0001"; end if;else num3<=num3+"0001";end if; else num2<=num2+"0001"; end if; else num1<=num1+"0001"; end if; end if; end if; --end if;END PROCESS;haomiao_cnt<=num3 & num2 & num1;--毫秒百十个位 miao_cnt<=num6 & num5 & num4;--秒百十个位--信号输出Millisecond <= haomiao_cnt;Second <= miao_cnt;current_state<=state;END RTL;

设计文档:

设计文档_1.doc

设计文档_2.doc

1. 工程文件

2. 程序文件

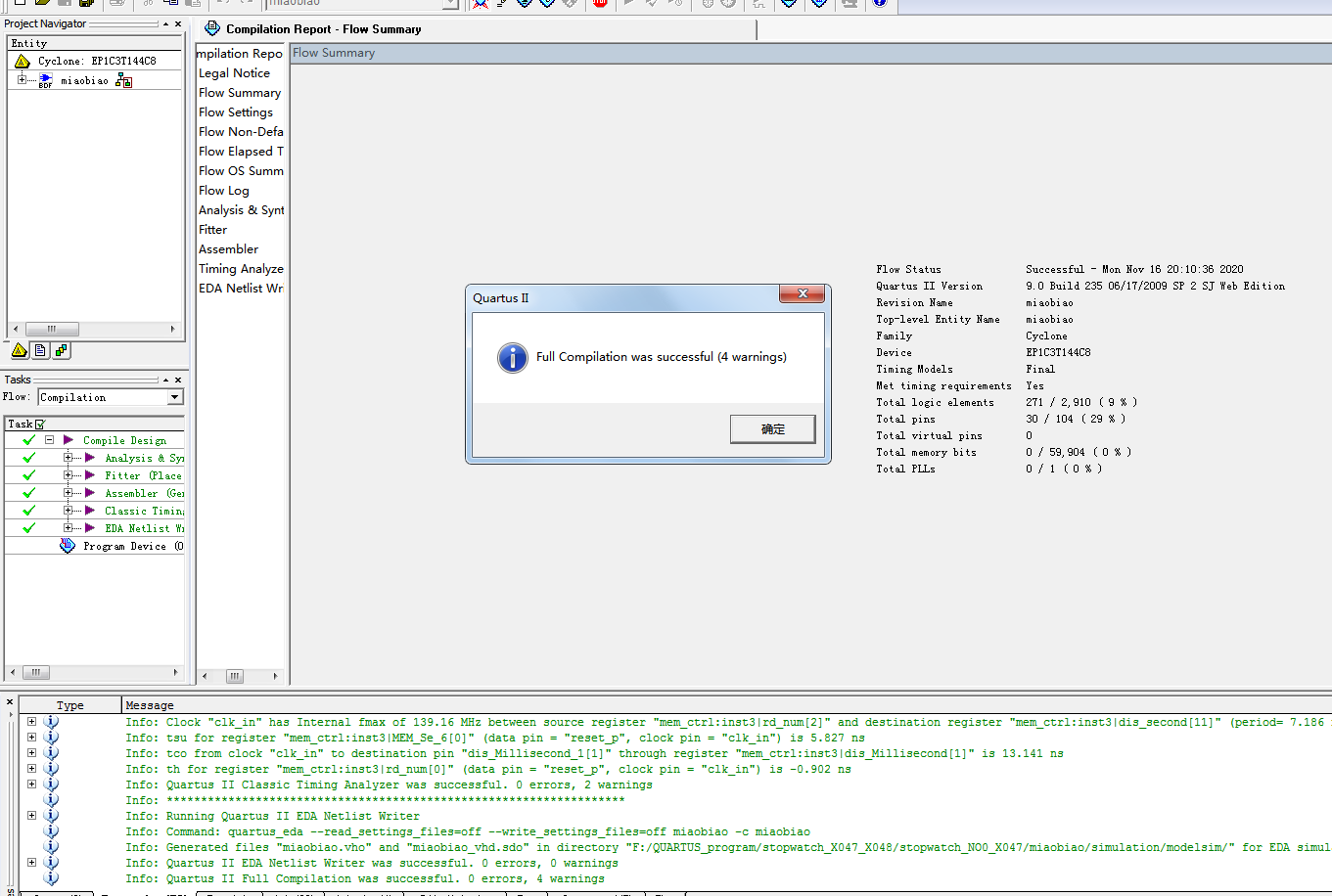

3. 程序编译

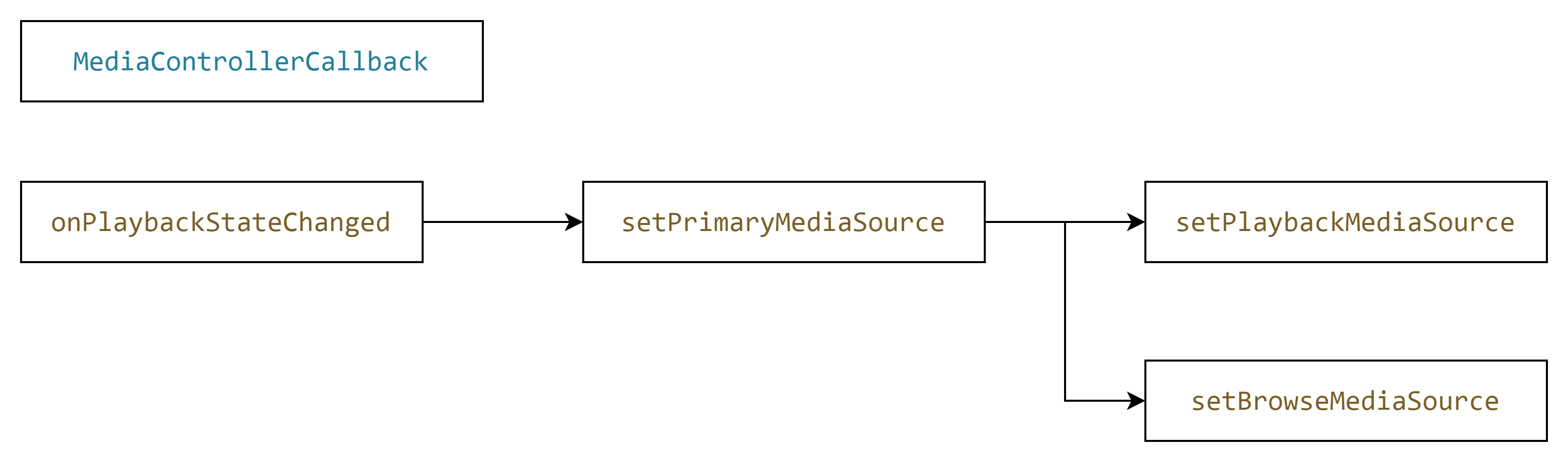

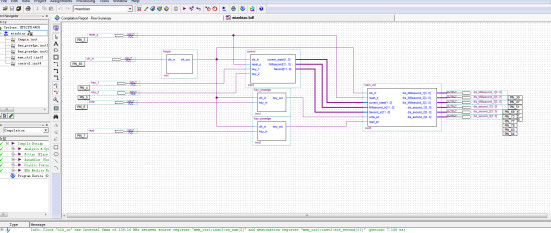

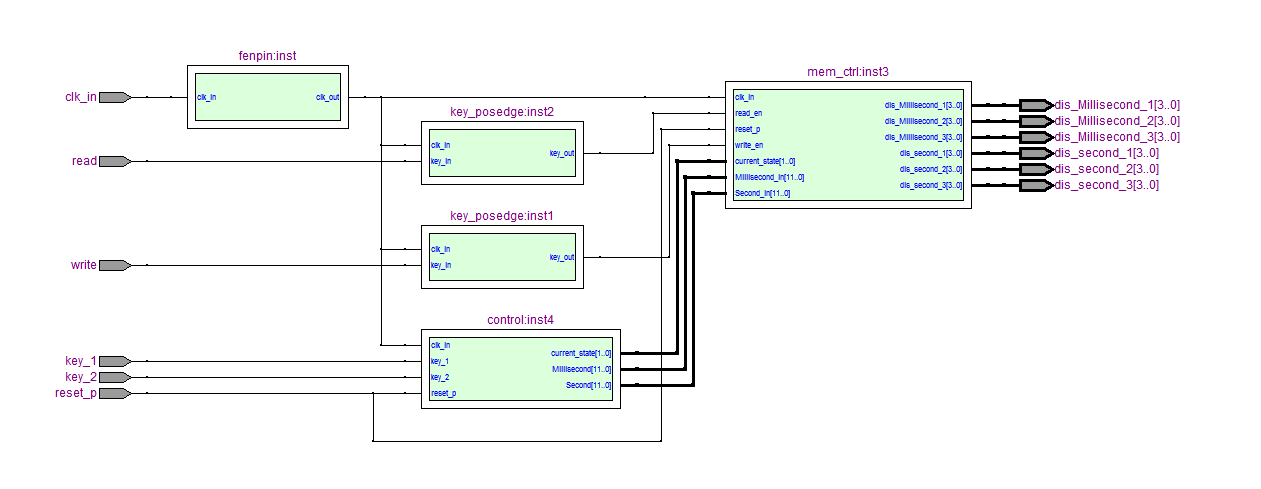

4. RTL图

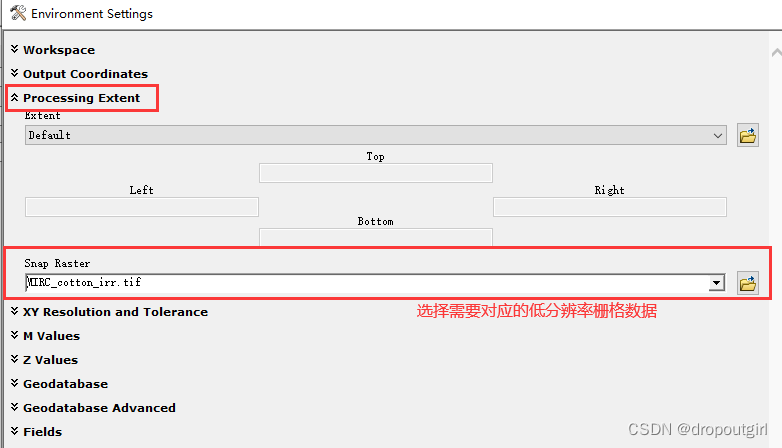

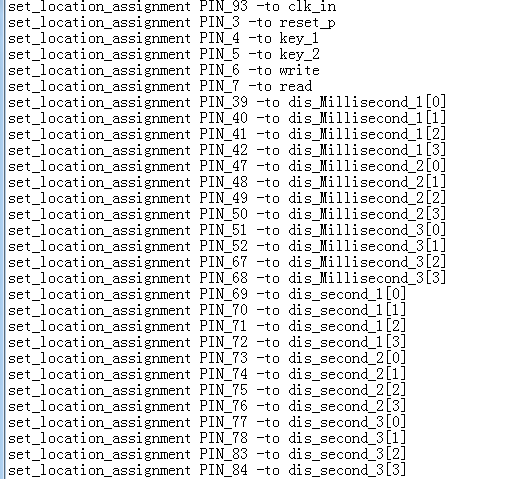

5. 管脚分配

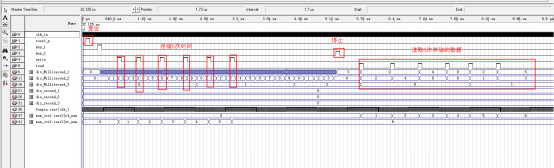

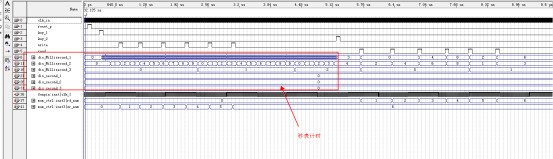

6. 仿真图