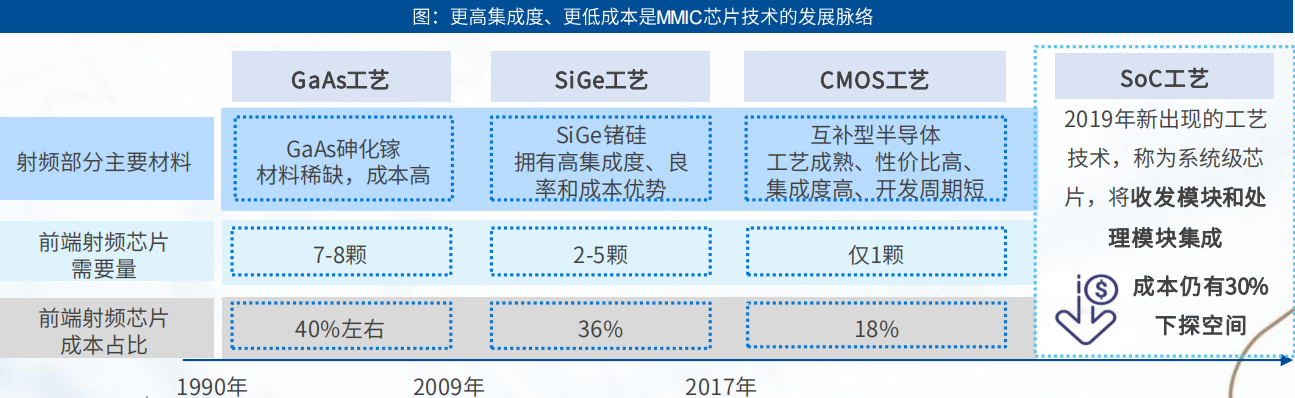

2.1 MMIC芯片工艺发展至CMOS时代,芯片集成度更高、体积与成本下降

MMIC芯片工艺经GaAs、SiGe已发展至CMOS时代,CMOS MMIC具有更低成本、更高集成度的优势。 工艺的主要变化发生在MMIC芯片的射频材料部分,目前SiGe仍为主流工艺。 SiGe虽在高频特性、导热性等方面据有优势,但SiGe MMIC大多为分立式,造成雷达整体体积较大使其应用前景受到限制,同时相较集成度更高的CMOS MMIC在成本、尺寸和研发周期上占劣势,未来将逐步被CMOS工艺所替代。

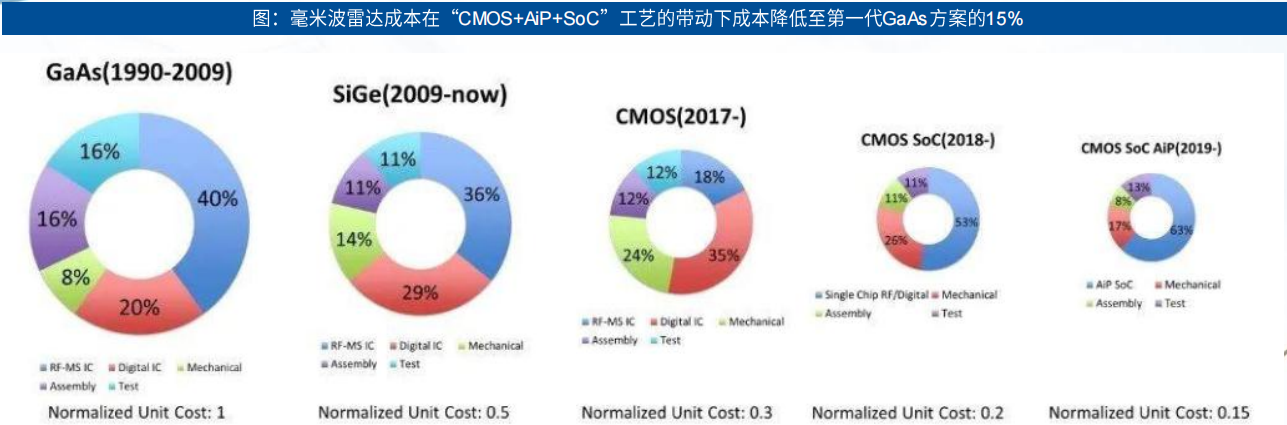

CMOS MMIC集成度更高,带来成本、体积和研发周期的优势 。 CMOS晶圆的低价、CMOS工艺在大规模生产上的成本优势,基于CMOS工艺的MMIC占系统总成本比重相较SiGe的36%下降至18%,结合SoC。受益于更高集成度, CMOS工艺的毫米波雷达体积进一步缩小、雷达适配性更好,同时前端射频芯片需要量从AsGa和SiGe的7-8颗、2-5颗降低至1颗,雷达模块设计复杂度和难度大幅降低,从而使研发周期缩短。

2.2 AiP(封装天线)进一步带动毫米波雷达集成度提高、体积与成本下降

AoB(Antenna on Board,板载天线) 将天线以及电源管理电路、闪存等集成在PCB基板上,AoB方案中的天线放置在高频PCB基板材料上,增加了PCB的成本和结构复杂性,因而成本较高。 AoB是当前前向毫米波雷达的主流天线设计方案。

AiP(Antenna in Package,封装天线)是将收发天线、MMIC芯片以及雷达专用处理芯片集成在同一封装内,是将毫米波雷达向更高集成化推进的 技术方案。 由于整体面积大幅缩小且绕过高频PCB材料需求,AiP技术带动体积更小、成本更低的毫米波雷达诞生。同时更紧凑集成化的设计使芯片到天线的路径更短,带来更低功耗和更高效率,但因使用小型天线将导致雷达探测距离以及角分辨率下降。

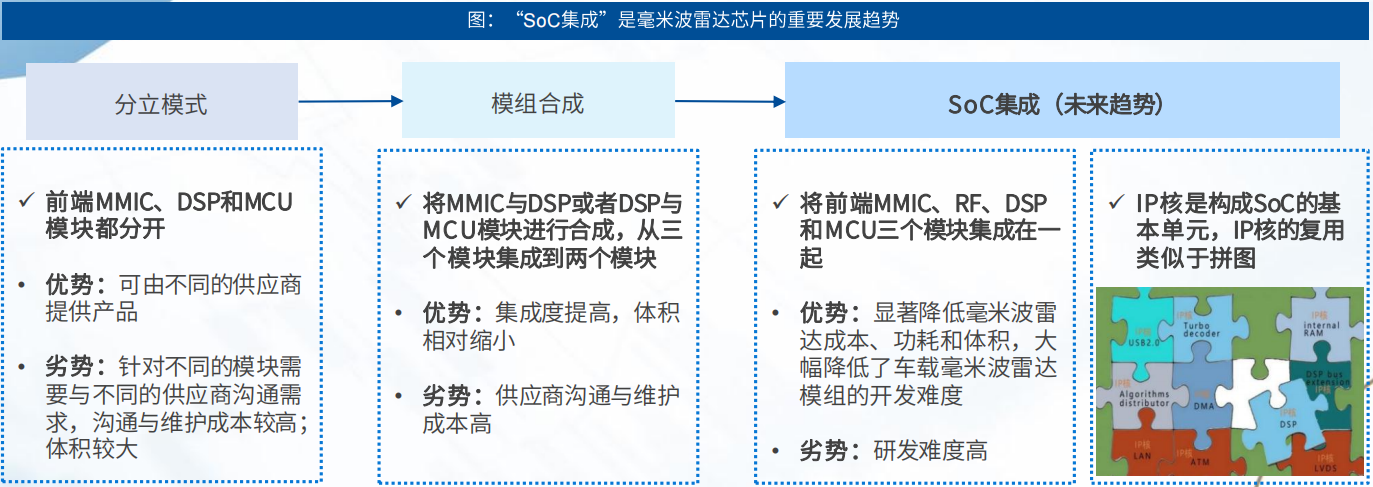

2.3 毫米波雷达SoC芯片开启高集成度、小型化、平台化和系列化时代

在毫米波雷达CMOS工艺、AiP封装技术走向成熟并大量应用的背景下,毫米波雷达已逐步从不同模块分立向模块高度集成的“毫米波雷达SoC”形态进 化。 毫米波雷达SoC技术将收发模块(MMIC、RF)和处理模块(DSP、MCU)集成于同一块芯片中,充分满足汽车及IoT行业对于整体小型化、集成化要求,是毫米波雷达产品形态的一次巨大提升,并使产品的平台化、系列化发展和下游模组研发变得更容易。

平台化、系列化的毫米波雷达SoC使下游用户的研发效率提高。 毫米波雷达SoC支持各种调试功能,CPU资源管理更加便捷,符合Automotive SPICE标准,可以让下游模组、毫米波雷达应用端用户导入更加容易,相关产品更快上市。

毫米波雷达SoC研发和规模化生产难度较高,掌握核心技术且能稳定量产的雷达芯片厂商具有较强竞争力。 由于集合了多种模块,研发毫米波雷达SoC需要集合芯片设计、天线设计、封装设计等研发资源,车规领域还需配备强大的过车规团队和资源,并在制造环节投入较大的资源以稳定良率,对研发厂商的要求较高。较高的门槛亦是护城河,掌握核心技术并能稳定量产的毫米波雷达芯片产商将在未来分享更多市场份额。

CMOS半导体工艺、AiP先进封装技术与SoC集成使得采用SoC芯片的毫米波雷达集成化更高、体积更小。一方面带动成本进一步降低约25%,另一方面 使毫米波雷达尺寸更小、应用场景大幅拓宽,结合同时带来的低功耗和模组开发难度降低,共同推动毫米波雷达的性价比不断提升,毫米波雷达及芯片 产业已越过大规模落地应用的临界点。

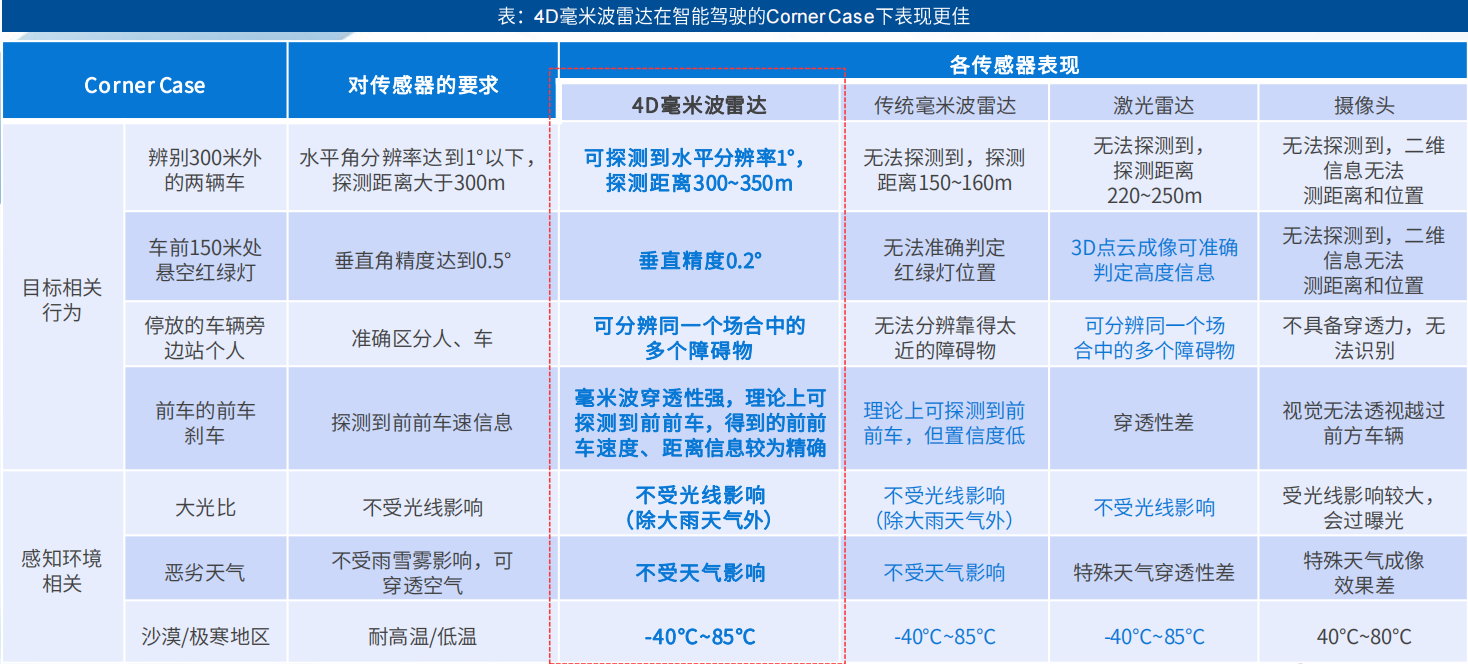

2.4 新兴的4D毫米波雷达克服传统毫米波雷达短板,产业空间进一步拓宽

4D毫米波雷达通过增加虚拟通道数在输出信息数量以及质量上有所提升,克服传统毫米波雷达短板。

数量上:4D毫米波雷达能够输出z维度的信息,进行静物识别。 传统毫米波雷达无法获得高度信息,使用时会发生静物误识别、漏识别等问题,造成“幽灵刹车”或是车祸撞击,4D毫米波雷达通过增加虚拟通道的数量实现俯仰角度的测量,用立体化的测量信息弥补缺陷;

质量上:虚拟通道数量的增加使得4D毫米波雷达输出距离、速度和角度信息的分辨率大幅提升。 以以色列毫米波雷达公司Arbe的4D毫米波雷达产品Phoenix为例,其水平分辨率较传统产品提升了5-10倍。

4D毫米波点云相较传统毫米波能形成更多、更丰富的点云数据,一定程度上具备成像功能,或在中低端场景成为激光雷达的平替,因而具备更加广阔 的应用空间。

![[RoarCTF 2019]Easy Java(java web)](https://img-blog.csdnimg.cn/direct/81b05b993f2943a9961cb736c5c21e12.png)

![[鹏城杯 2022]简单包含](https://img-blog.csdnimg.cn/direct/ce4932b5e1a449a38cc25c3db381e28c.png#pic_center)