一、前言

Xilinx FPGA通过加载比特流到内部存储单元来进行配置。

Xilinx FPGA存在两种数据配置路径,一种是满足最小引脚需求的串行路径,一种是可用8位、16位或32位来连接到行业的高性能通用接口,如处理器,8位或者16位并行的闪存。与处理器和处理器外围设备一样, FPGA可以在系统中按需无限次重新编程。

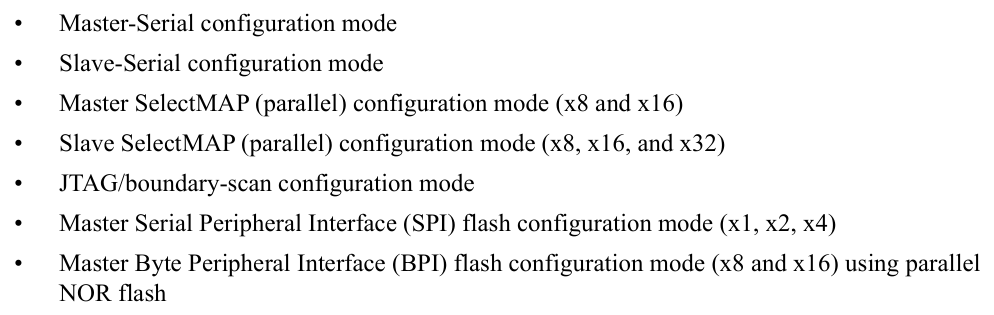

由于Xilinx FPGA 配置数据存储在 CMOS 配置锁存器 (CCL) 中,因此必须在断电后重新配置。比特流每次都通过特殊的配置引脚加载到器件中。常用的配置模式可以分为:

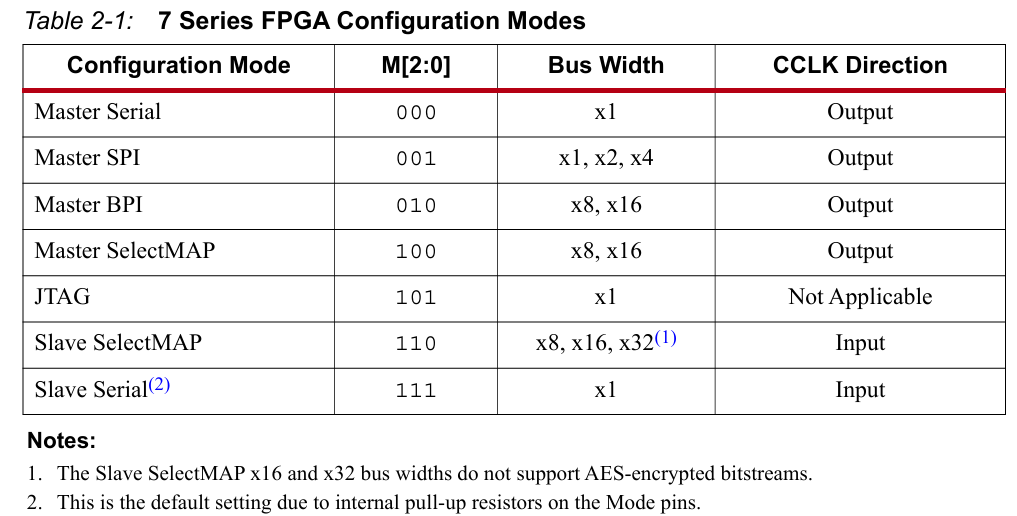

通过在输入引脚M[2:0]专用模式上设置适当的级别来选择特定的配置模式。M2、M1和M0模式引脚应通过上拉或下拉电阻(≤1kΩ),或直接连接到地或VCCO_0l来设置在恒定的DC电压电平,并且引脚不应在配置期间和配置之后变化。

通过在输入引脚M[2:0]专用模式上设置适当的级别来选择特定的配置模式。M2、M1和M0模式引脚应通过上拉或下拉电阻(≤1kΩ),或直接连接到地或VCCO_0l来设置在恒定的DC电压电平,并且引脚不应在配置期间和配置之后变化。

此外,如果M[2:0]为101,则该FPGA只支持JTAG进行配置。处于其余配置模式下时,依旧可以使用JTAG模式进行调试,并且优先级最高。

主和从的概念于配置时钟(configuration clock,CCLK)的方向有关:

- 在主配置模式下,7系列设备通过内部振荡器驱动CCLK。要选择所需的频率,使用比特流-g ConfigRate选项,具体可以参考UG628(ISE命令行工具用户指南)的BitGen部分和UG908 (Vivado编程和调试用户指南)的“设备配置比特流设置”部分。配置后,除非选择了持久选项或使用了SEU检测,否则CCLK将关闭。CCLK引脚为三态,上拉较弱。

-

在从配置模式中,CCLK是一个输入。

FPGA 自加载配置模式,通常称为主模式,可用于串行或并行数据路径。主模式利用各种类型的非易失性存储器(如Flash、EEPROM等)来存储 FPGA 的配置信息。 FPGA 在驱动配置逻辑的内部振荡器中生成配置时钟信号,并在 CCLK 输出引脚上可见。

外部控制加载 FPGA 配置模式,通常称为从模式,也可用于串行或并行数据路径。在从模式下,处理器、微控制器、DSP 处理器或测试仪等外部“智能代理”将配置映像下载到 FPGA 中,从配置模式的优势在于 FPGA 比特流几乎可以驻留在整个系统中的任何位置。从串行模式非常简单,仅由时钟和串行数据输入组成。JTAG模式也是一种简单的串行配置模式,流行于原型设计,并高度用于板测试。Slave SelectMAP模式是一个简单的8位、16位或32位宽处理器外围接口,包括芯片选择输入和读/写控制输入。

二、FPGA 配置

一般必然存在的JTAG调试模式,另外使用较多的是主SPI模式和从串行配置模式,其余并行配置模式由于消耗引脚较多,一般不会使用,与这几种串行模式的区别仅在于数据引脚的区别。

2.1 配置信号

每个配置模式都有一组对应的接口引脚,这些引脚跨越7系列FPGA上的一个或多个I/O bank。bank 0包含专用配置引脚,并且始终是每个配置接口的一部分。bank 14 和 bank15包含涉及特定配置模式的多功能引脚。7系列FPGA数据表规定了在3.3V、2.5V、1.8V或1.5V下工作的bank中配置引脚的开关特性。

所有JTAG和专用配置引脚都位于一个单独的专用bank中,该bank具有专用电压电源(VCCO_0)。多功能配置针脚位于bank 14和15中。

CFGBVS(Configuration Banks Voltage Select)

CFGBVS决定专用配置bank0、bank14和bank15中多功能配置引脚的I/O电压操作范围。CFGBVS总是控制7系列FPGA的bank0电压,仅在配置期间控制bank14和bank15的电压。如果为bank0的VCCO_0电源提供2.5V或3.3V,则CFGBVS引脚必须连接为高电平(比如连接到VCCO_ 0)。仅当bank0的VCCO_0小于或等于1.8V,将CFGBVS连接到低电平(比如连接到GND)。在配置过程中,bank14和bank 15的电压应与施加到bank0的VCCO电平相匹配。

PROGRAM_B(program bar)

PROGRAM_B拉低(下降沿)时复位配置逻辑,PROGRAM_B低脉冲(下降沿)可以清除FPGA内部的所有配置信息,并初始化新的配置序列。注意在上电时把PROGRAM_B 保持为低电平不会使 FPGA 配置保持复位状态,延迟配置的时间需要使用INIT_B信号配合完成。PROGRAM_B 引脚外部需要通过小于等于4.7KΩ的电阻上拉至VCCO_0来确保稳定的高电平输入,推荐连接到GND来使能配置复位。

INIT_B(initialization bar)

低电平有效。当 FPGA 处于配置复位状态、FPGA 正在初始化(清除)其配置存储器或 FPGA 检测到配置错误时,FPGA 将该引脚驱动为低电平。

完成 FPGA 初始化过程后,INIT_B 被释放到高阻态,此时外部电阻器应将 INIT_B 拉高(将 INIT_B 连接到一个 ≤ 4.7 kΩ 的上拉电阻到VCCO_0)。当初始化过程完成后在 INIT_B 输入检测到高电平时,FPGA 继续执行由 M[2:0] 引脚设置指示的配置序列的其余部分。

Done

该信号高电平表示FPGA配置序列完成,默认情况下,该引脚为开漏输出,内部有一个大约10KΩ的上拉电阻,外部只需要通过一个330Ω的电阻上拉即可。

2.2 配置流程

配置流程包含三个大步骤(建立,加载程序,初始化启动),分为8个小步骤

对于所有配置模式,7系列的基本配置流程都是相同的,主要可以分为三个大块:设备启动,数据流加载,启动序列。

后面内容来源于:

谁说配置难?这篇文章让你轻松掌握xilinx 7系列FPGA配置技巧 - 知乎 (zhihu.com)

1.设备上电

配置流程的第一步自然是设备上电,这里也就解释了为何固化程序后需要下电再上电才能生效。配置涉及到的电源如下:

VCCO_0以及VCCO_14、VCCO_15在前文已经提及,其他的电源需要参照对应的数据手册推荐值进行配置,例如K7对应手册【DS182】:

FPGA在设备启动阶段(流程1-3)的时序关系:

TPOR :Power-on Reset (POR) ;TICCK :CCLK Output Delay

FPGA上电启动后电压达到VCCO后在10~50ms后INIT_B信号拉高,初始化完成,FPGA开始加载配置工作。

上电后可以通过拉低将 PROGRAM_B 引脚切换为低电平来重新配置器件:

INIT_B 在初始化期间被内部驱动为低电平,然后在上电情况下(第一次上电配置)在TPOR(图 5‑4)之后释放,在其他情况下(触发退回或者重配置等)在TPL之后释放。如果 INIT_B 引脚在外部保持低电平,则器件在初始化过程中的这一点等待,直到该引脚被释放,并且需要满足TPOR或TPL延迟。

FPGA上电第一次加载与PROGRAM_B没有关系,只要达到延迟时间,FPGA就会初始化完成,init_b信号拉高,直接进入配置数据过程。只有第二次重新配置才使用PROGRAM_B。

图中的时间参数可以在对应的FPGA数据手册中查看,如K7系列对应【DS182】:

2.清除配置寄存器

在器件上电后、PROGRAM_B 引脚脉冲低电平后、使用 JTAG JPROGRAM 指令或 IPROG 命令后或在回退重试配置序列期间,配置存储器会顺序清除。在此期间:

Block RAM 被重置为其初始状态,并且触发器通过全局设置重置 (GSR) 的断言重新初始化。除少数配置输出引脚外,I/O 通过使用全局三态 (GTS) 置于 High‑Z 状态,如果 PUDC_B 为低电平,则内部上拉。

PUDC_B用于设置配置期间的上拉,低电平有效,电路上通过直连或者 ≤ 1kΩ 连接到VCCO_14或GND,禁止悬空。

清除配置寄存器发生在INIT_B为低的这个阶段。通常这个时间为3ms。

3ms的时间来自于复旦微的手册中:JFM7K325T清除配置寄存器时间为20ms,而对标产品为3ms。在从模式中推荐等待INIT_B拉高再进行配置。

3.采样模式引脚

当 INIT_B 引脚转换为高电平时,器件对模式引脚 M[2:0] 进行采样并开始驱动 CCLK(如果处于主模式)。此时,器件开始在配置时钟的上升沿对配置数据输入引脚进行采样。

对于 BPI 和 SelectMAP 模式,总线宽度最初为 x8,可以在状态寄存器查看。在总线宽度检测序列之后,状态寄存器被更新。从串行、主串行、SPI 和 JTAG 模式忽略总线宽度检测模式。

只有在通过电源循环或PROGRAM_B置位进行重新配置时,才会再次对模式引脚进行采样。

4.同步

FPGA正常数据加载前,需要做一个FPGA与配置方(如FLASH)之间的同步检查。方法是将一个特殊的 32 位同步字 (0xAA995566) 发送到FPGA。同步字会提醒FPGA即将到来的配置数据并将配置数据与内部配置逻辑对齐。

除“总线宽度自动检测”序列外,同步之前配置输入引脚上的任何数据都将被忽略。

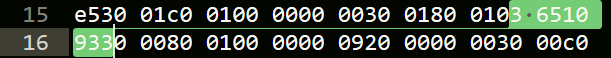

Xilinx在生成的.bit文件中已经自动加入了这个同步字。可以进行查看:

表5-19说明了bit流的定义:

5. 检测设备ID

设备同步后,必须通过设备 ID 检查才能加载配置数据帧。这可以防止配置具有针对不同设备格式化的比特流。如果在配置期间发生 ID 错误,设备会尝试执行回退重新配置。

设备 ID 检查内置于比特流中,器件 ID 检查是通过配置逻辑的比特流中的命令执行的,而不是通过 JTAG IDCODE 寄存器。ID可以在【UG470】的表1-1中查找到,例如7K325T对应3651093,可以在.bit文件中查找到:

6.加载配置数据

在准备工作完成后,FPGA开始加载配置数据。在这个过程中,FPGA的所有可配置I/O根据HSWAPEN引脚的设置变为弱上拉(HSWAPE=1)或者高阻态(HSWAPE=0)。这个阶段的I/O引脚还没有变为用户需要的状态,也最有可能影响到其他外围电路的上电时序和运行。

设计硬件电路时要特别注意并采取必要措施,如加入上下拉电阻或改变器件加电顺序来尽量避免或减少FPGA配置时对电路其他器件的影响。

7.CRC校验

加载配置数据帧时,器件会根据配置数据包计算循环冗余校验 (CRC) 值。加载配置数据帧后,配置比特流可以向设备发出校验 CRC指令,然后是预期的 CRC 值。如果设备计算的 CRC 值与比特流中的预期 CRC 值不匹配,则设备将 INIT_B 拉低并中止配置,此时用户必须把PROG-B引脚拉低,才能进行重新配置。

默认情况下,CRC 校验包含在配置比特流中,如果禁用 CRC 检查,则存在加载错误配置数据帧的风险,从而导致错误的设计行 为或损坏器件。

8.启动序列

加载配置帧后,FPGA不会马上执行用户的逻辑,比特流指示设备进入启动序列。启动顺序由 8 阶段(阶段 0‑7)顺序状态机控制。用户可以选择每个启动事件的特定阶段(见【UG628】):

可以强制启动序列等待 MMCM 锁定或等待 DCI 与适当的选项匹配。这些选项通常设置为在 MMCM 锁定和/或 DCI 匹配之前防止 DONE、GTS 和 GWE 被断言(防止设备操作)。

默认情况下,启动顺序:

与启动相关的信号:

| 信号名称 | 描述 |

|---|---|

| DONE | 表示配置完成。可以在外部保持低电平以与其他 FPGA 同步启动。 |

| Release_DONE | 指示设备是否已停止将 DONE 引脚驱动为低电平。如果引脚在外部保持为低电平,Release_DONE 可能与 DONE 引脚上的实际值不同。 |

| GWE | 全局写使能 (GWE)。置位后,GWE 启用 CLB 和 IOB 触发器以及FPGA 上的其他同步元件。 |

| GTS | 全局三态 (GTS)。置位后,GTS 禁用所有 I/O 驱动程序,除了少数配置管脚。 |

| EOS | 启动结束 (EOS)。 EOS 表示配置和启动过程的绝对结束。 |

| DCI_MATCH | 指示所有数控阻抗 (DCI) 控制器何时将其内部电阻器与外部参考电阻器匹配。 |

| MMCM_LOCK | 指示所有时钟管理块何时就绪。该信号默认置位。如果在MMCM 上使用了 LOCK_WAIT 选项并且在生成比特流时使用了LockCycle 选项,则它处于活动状态。 |

DONE信号可通过DONE 引脚或7 系列FPGA状态寄存器获取,其余只能通过7 系列FPGA状态寄存器获取。对应的信号时序如下:

![[问题记录] oracle问题汇总记录](https://img-blog.csdnimg.cn/direct/c0ce29a1d53f478c9e18daa0b9e06057.png)

![[C语言][数据结构][动态内存空间的开辟]顺序表的实现!](https://img-blog.csdnimg.cn/direct/a58c5df3438f4c088fe261fe3b686e31.png)