NVIDIA GPU 架构梳理

近期深入研究并行计算,需探究底层硬件精髓。高性能计算界,英伟达显卡稳居霸主地位。本文旨在梳理NVIDIA GPU架构之演进历程,助您洞悉其技术脉络,把握未来计算趋势。

目录:

NVIDIA GPU架构历经数次革新:从Tesla架构奠定基石,到Fermi架构提升性能,再到Kepler架构优化能效,Maxwell架构深化节能设计。Pascal架构强化深度学习,Volta架构推动高性能计算,Turing架构引领光线追踪,直至Ampere架构重塑游戏与创作体验。每一代都是技术革新的里程碑。

一、NVIDIA GPU的架构演变历史和基本概念[1]

截止2021年,发布时间离我们最近的8种NVIDIA GPU微架构是:

- Tesla

- Fermi

- Kepler

- Maxwell

- Pascal

- Volta

- Turing

- Ampere

NVIDIA以其独特的命名方式,将GPU微架构与历史上的杰出科学家相结合,其八大微架构分别致敬了特斯拉、费米、开普勒、麦克斯韦、帕斯卡、伏打、图灵和安培等科学巨匠。

其中最新的是2020年宣布的Ampere架构。

二、Tesla 架构

经典型号是G80,在Fermi架构白皮书的开篇部分有对G80的简要介绍:

- G80 GPU创新支持C语言,程序员无需另学新语言,即可畅享GPU强大性能。作为首款支持C语言的GPU,G80引领行业新潮流。

- G80作为首款采用单一统一处理器的GPU,颠覆了传统独立的顶点和像素管道设计,强效执行顶点、几何、像素及计算程序,开创图形处理新纪元。

- G80 是第一款使用标量线程处理器的 GPU,无需程序员手动管理向量寄存器

- G80革命性引入单指令多线程(SIMT)执行模型,实现一条指令驱动多个独立线程并发执行,效能飞跃,引领计算新纪元。

- G80革命性引入共享内存与屏障同步机制,为线程间通信开辟新天地。这一创新设计,不仅提升了通信效率,更确保了数据同步的精准性,为多线程应用带来了前所未有的性能提升。

G80 显卡

三、Fermi架构[2]

Fermi 架构是NVIDIA GPU 架构自初代 G80 以来最重大的飞跃。

NVIDIA GPU研发团队汲取G80与GT200精华,创新设计,缔造全球首款计算GPU。研发过程聚焦关键领域:性能提升、能效优化与技术创新,为计算领域树立新标杆,引领行业未来。

- GPU在单精度浮点性能上已超越桌面CPU十倍,但针对部分计算密集型应用,双精度性能的提升同样至关重要,我们致力于不断突破,满足您的更高需求。

- ECC支持功能强大,助力GPU计算在数据中心安全部署。通过ECC,用户可以放心安装大量GPU,保障医疗成像、金融期权定价等敏感数据应用免受内存错误侵扰,确保数据完整性与系统稳定性。

- True Cache Hierarchy——对于无法使用GPU共享内存的并行算法,用户渴望一个高效的缓存架构。True Cache Hierarchy应运而生,为您解决这一难题,实现更顺畅的运算体验。

- CUDA程序员渴望更多共享内存,以加速应用。众多开发者需求超16KB的SM共享内存,助力程序飞速运行,满足高效计算新挑战!

- 实现更迅捷的上下文切换,用户渴望在应用程序间流畅穿梭,享受极速的图形与计算互操作体验,让工作娱乐更加高效畅快。

- 用户急需优化并行算法效率,期望实现更迅捷的读-修改-写原子操作,以满足高速处理数据的迫切需求,从而大幅提升算法执行效率。

基于以上出发点,Fermi架构有以下四大亮点:

第三代流式多处理器 (SM)

- 每个 SM 有 32 个 CUDA 内核,是 GT200 的 4 倍

- 8 倍于 GT200 的峰值双精度浮点性能

- Dual Warp Scheduler,实现双warp指令的高效调度与分派,确保并行处理,提升整体运算效率,助力实现更快速、更稳定的数据处理。

- 64 KB RAM,可配置共享内存和 L1 cache

第二代并行线程执行 ISA

- 具有完整 C++ 支持的统一地址空间

- 针对 OpenCL 和 DirectCompute 进行了优化

- 完整的 IEEE 754-2008 32 位和 64 位精度

- 带有 64 位扩展的完整 32 位整数路径

- 支持过渡到 64 位寻址的内存访问指令

- 通过预测提高性能

改进的内存子系统

- NVIDIA Parallel DataCache TM 层次结构,拥有可配置的L1与Unified L2 Caches,以卓越性能提升数据处理效率,为您带来前所未有的计算体验,让每一份数据价值最大化。

- 第一个支持 ECC 内存的 GPU

- 大幅提升原子内存操作性能

NVIDIA GigaThread TM 引擎

- 应用程序上下文切换速度提高 10 倍

- 并发内核执行

- 乱序线程块执行

- 双重叠内存传输引擎

以上是Fermi 架构相较于初代架构提升的地方

下面具体看看Fermi 架构的配置

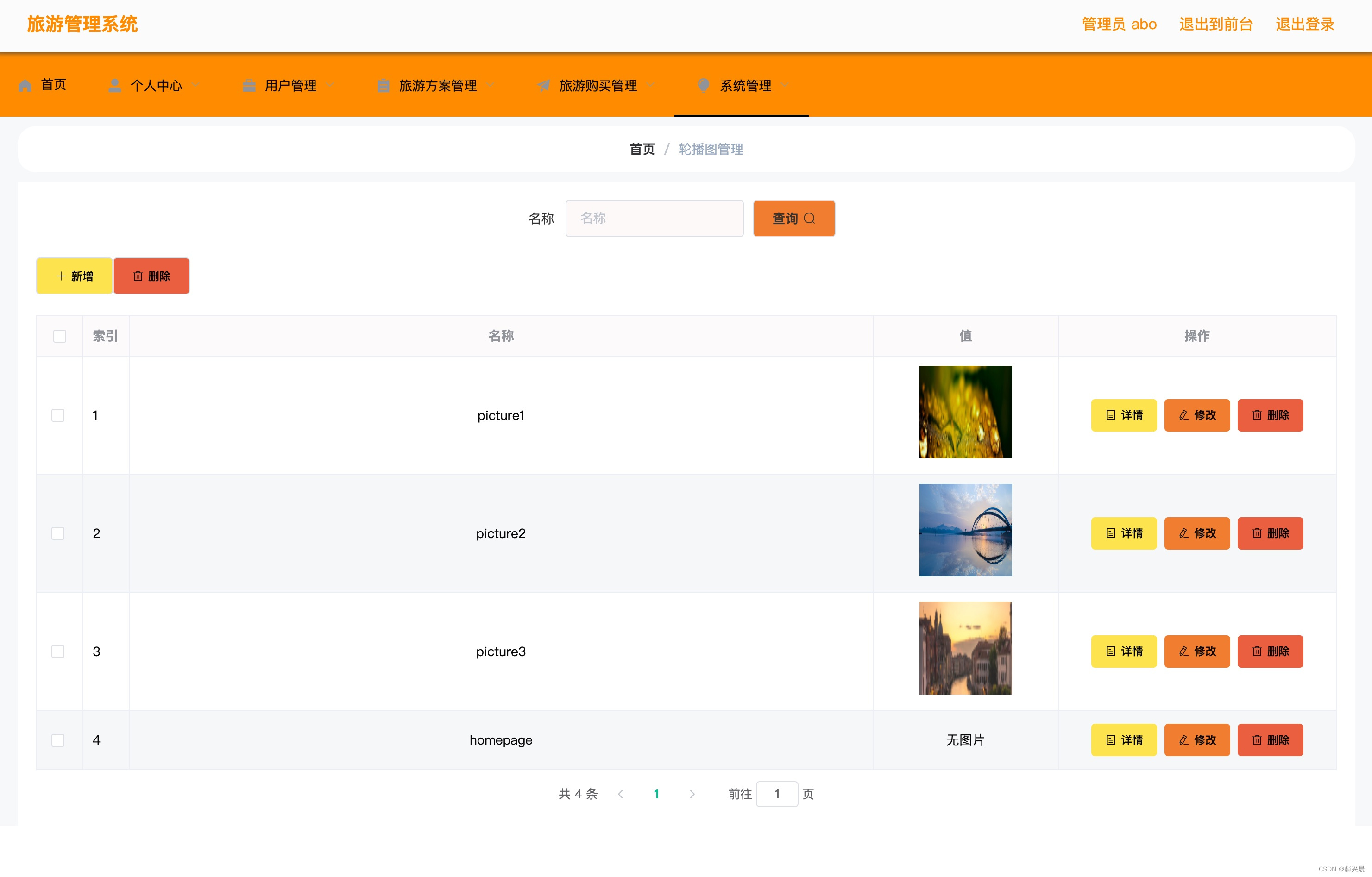

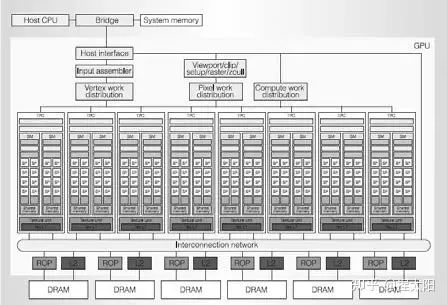

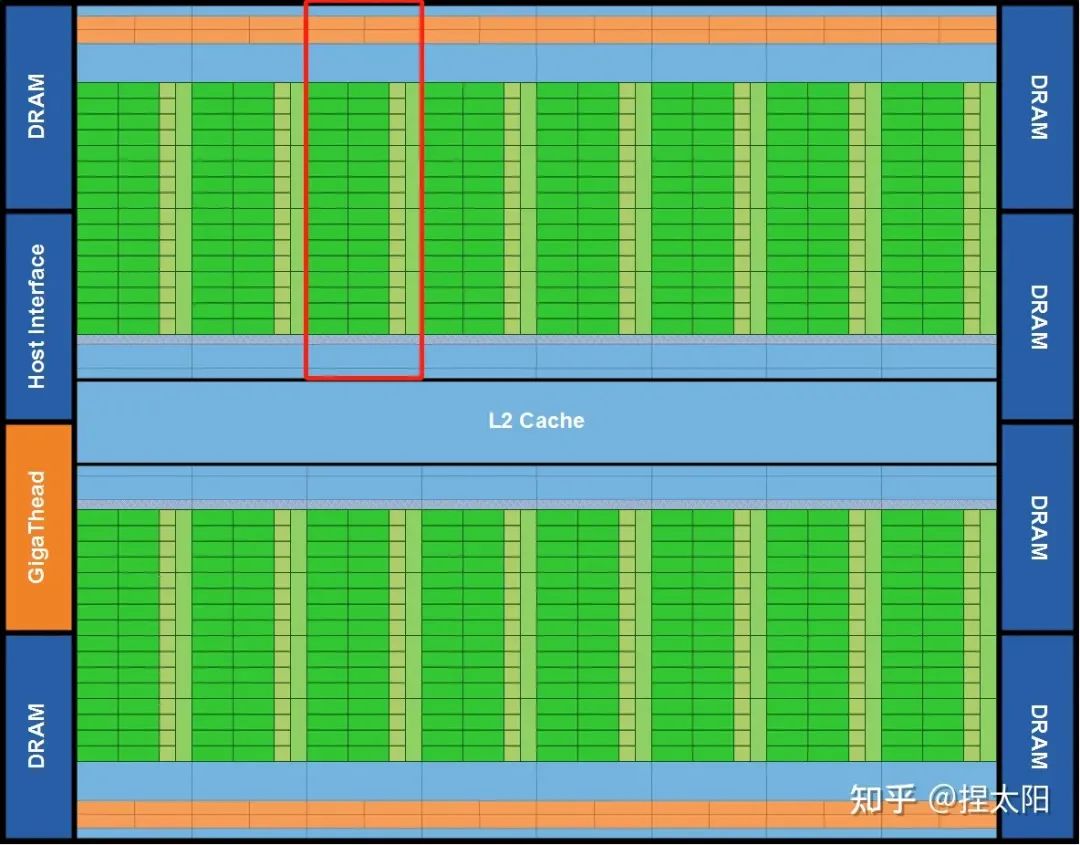

Fermi 架构

首款基于Fermi架构的GPU震撼登场,采用30亿晶体管精心打造,拥有强大512个CUDA内核,性能卓越,引领行业新风尚!

这512个CUDA内核巧妙布局,形成16个SM模块,宛如垂直的矩形阵列,紧密环绕在共享的L2缓存周围。每个SM模块均内含32个CUDA内核,高效协作,共同构建出强大的计算力,助力各类复杂任务的快速处理。

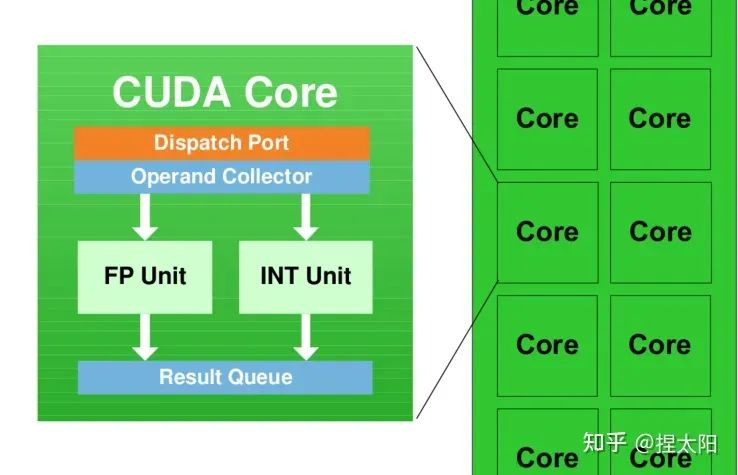

一个CUDA 内核为一个线程在每个时钟周期里执行一条浮点或整数指令。

6个64位显存分区,构建出强大的384位显存接口,赋予显卡强劲性能。总支持容量高达6GB的GDDR5 DRAM显存,确保流畅运行各类高负载任务。

GDDR5:第五版图形用双倍数据传输率存储器

DRAM:动态随机存取存储器

主机接口凭借PCI-Express技术,高效连接GPU与CPU。Giga Thread全局调度器精准分配线程块至SM线程调度器,确保处理任务迅速而有序。此系统结构专业,操作精准,助力计算性能大幅提升,为用户带来前所未有的高效体验。

Fermi图形渲染架构

NVIDIA GPU自Fermi系列起,均内置GPC(图形处理集群),这一强大单元宛如独立GPU般的存在。每个GPC配备一光栅引擎与四个SM(流式多处理器),共同构筑起强大的图形处理体系。众多GPC协同工作,确保了GPU的高效运行与卓越性能,为用户带来无与伦比的图形处理体验。

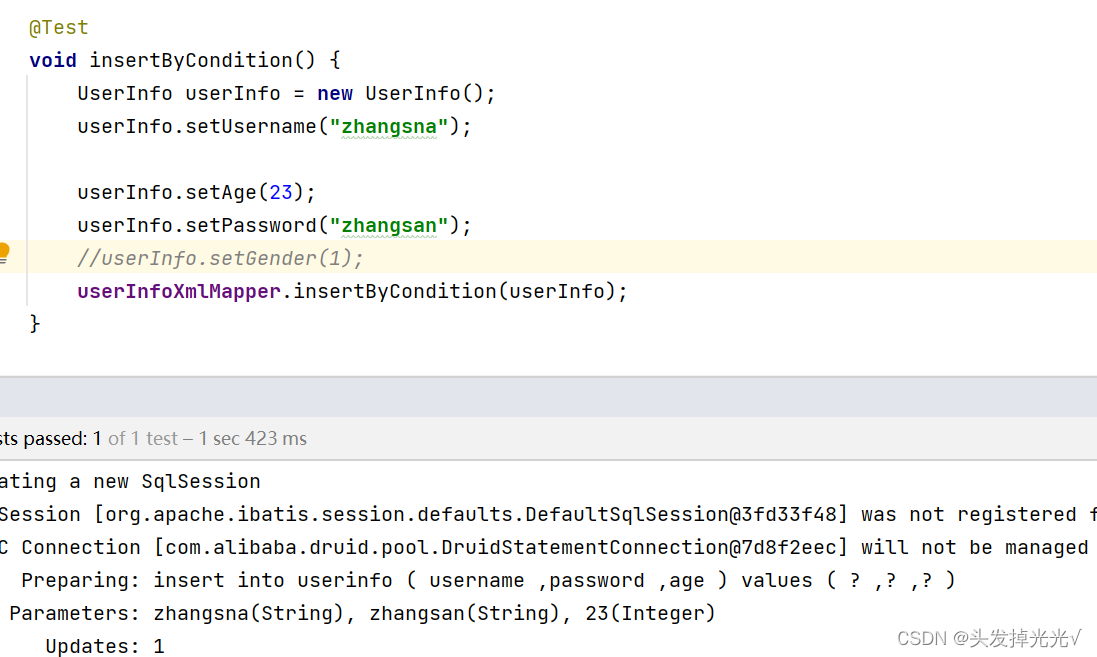

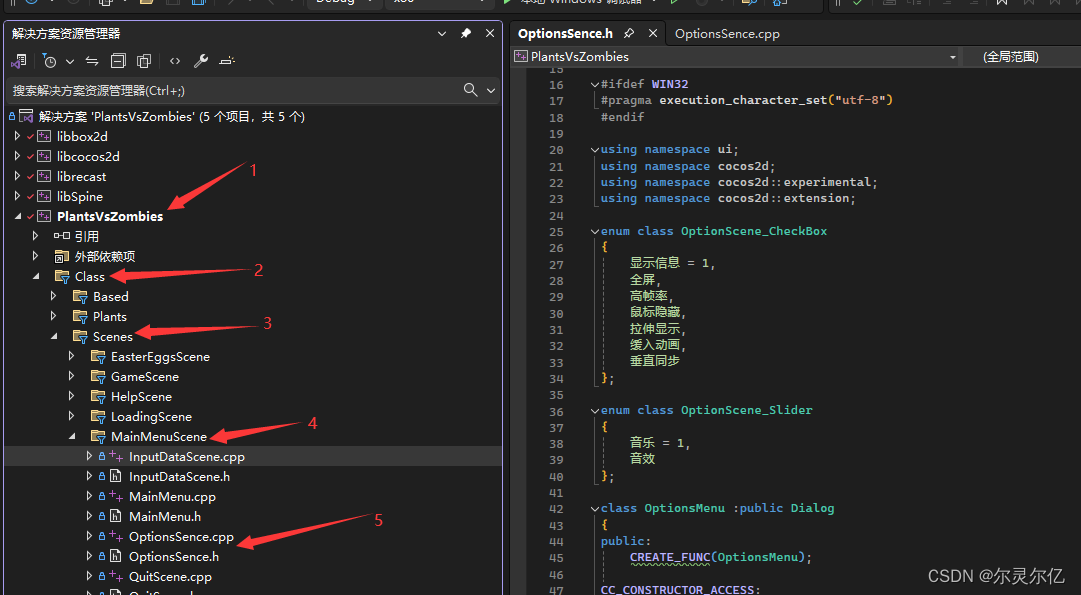

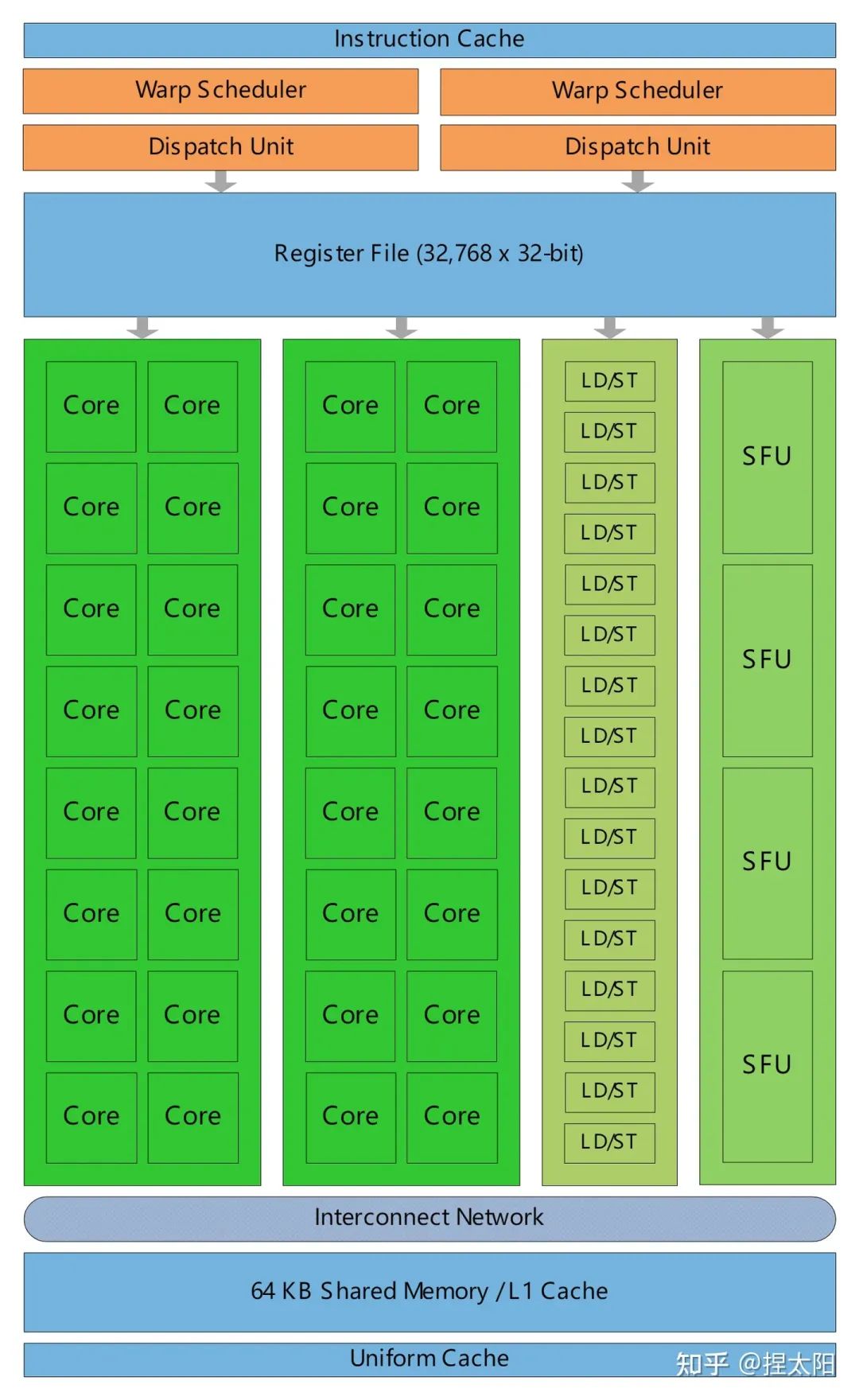

Fermi Streaming Multiprocessor (SM)

上图是将16个SM中的 1 个拿出来放大后的详细结构图,其中包含:

- 橙色部分:2 个 Warp Scheduler/Dispatch Unit

- 绿色部分:32 个 CUDA 内核,分在两条 lane 上,每条分别是 16 个

- 浅蓝色部分:register file-寄存器文件和 L1 cache

- 16 个 Load/Store units (LD/ST Unit)

- 4 个 Special Function Units (SFU)

每款SM均搭载32个CUDA内核,即图中绿色的Core小方块。每个内核均配备全流水线化的整数算术逻辑单元(ALU)和浮点单元(FPU),确保高性能计算。SM的卓越设计,让计算效能得到显著提升,为您带来前所未有的体验。

CUDA 内核

SM,作为GPU架构的核心组件,是实现硬件并行性的关键所在。其重要性不言而喻,正是SM的卓越性能,赋予了GPU强大的并行处理能力。

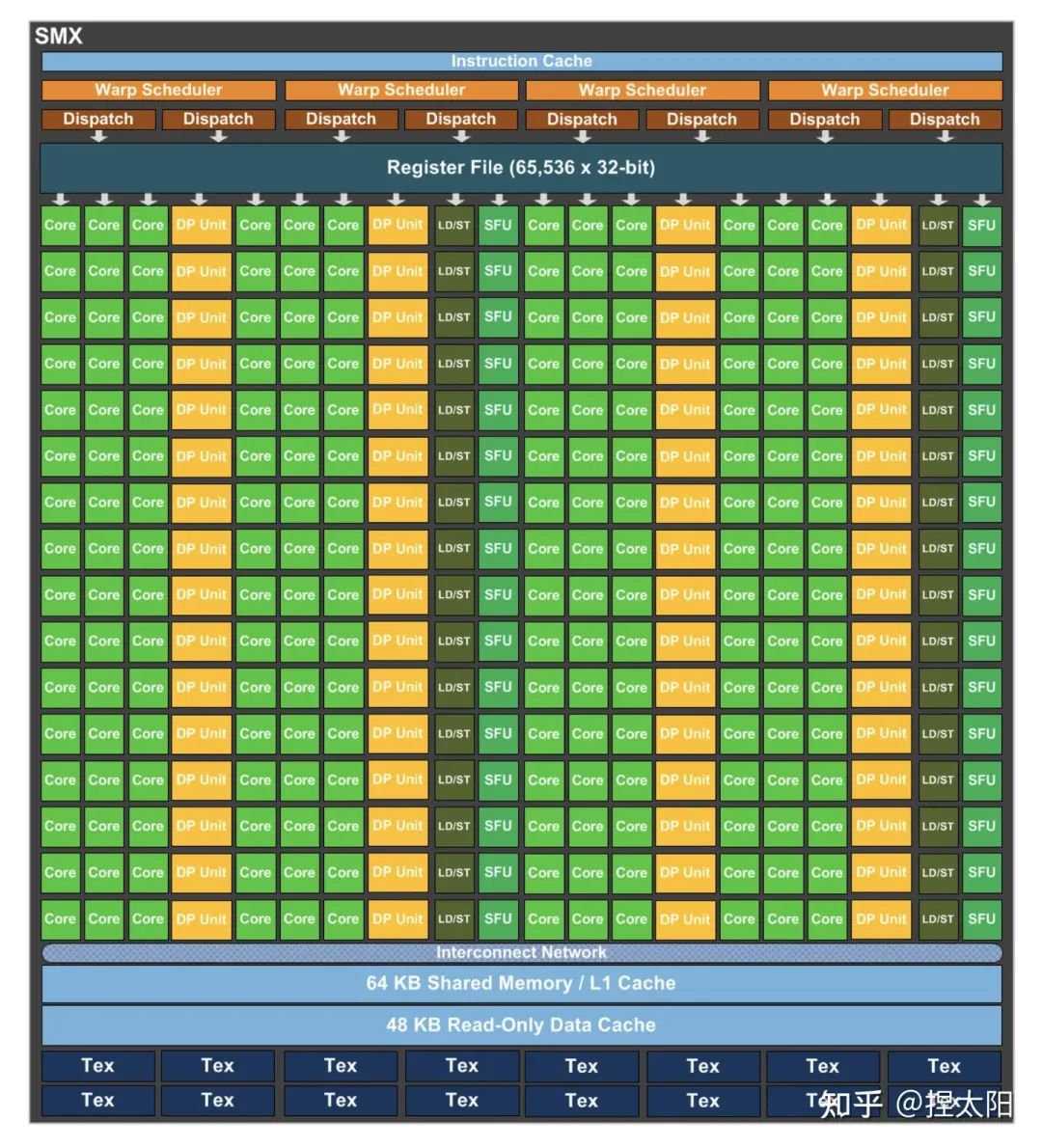

四、Kepler架构

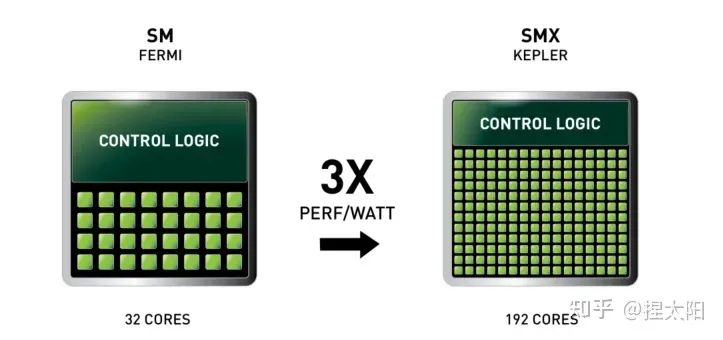

Kepler架构以精简SM单元数(现称SMX单元)并大幅扩充每组SM单元中的CUDA内核数为核心理念。相较于Fermi架构,Kepler架构实现了跨越式提升,每个SM单元的CUDA内核数激增五倍,从32个跃升至192个,展现了其强大的计算能力。

在每个SMX中:

- 4 个 Warp Scheduler,8 个 Dispatch Unit

- 绿色:192个 CUDA 内核,分在12条 lane 上,每条分别是 16 个

- 黄色:搭载64个DP双精度运算单元,高效分布于4条lane,每条lane精准配置16个单元,运算性能卓越。

- 32 个 LD/ST Unit

- 32 个 SFU

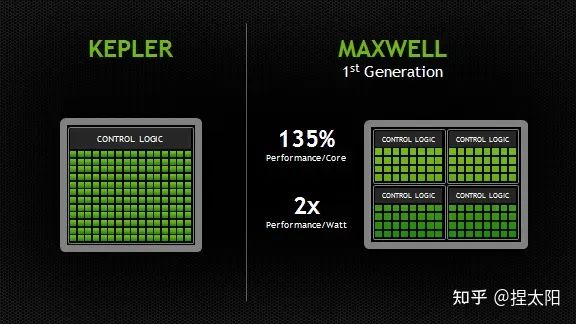

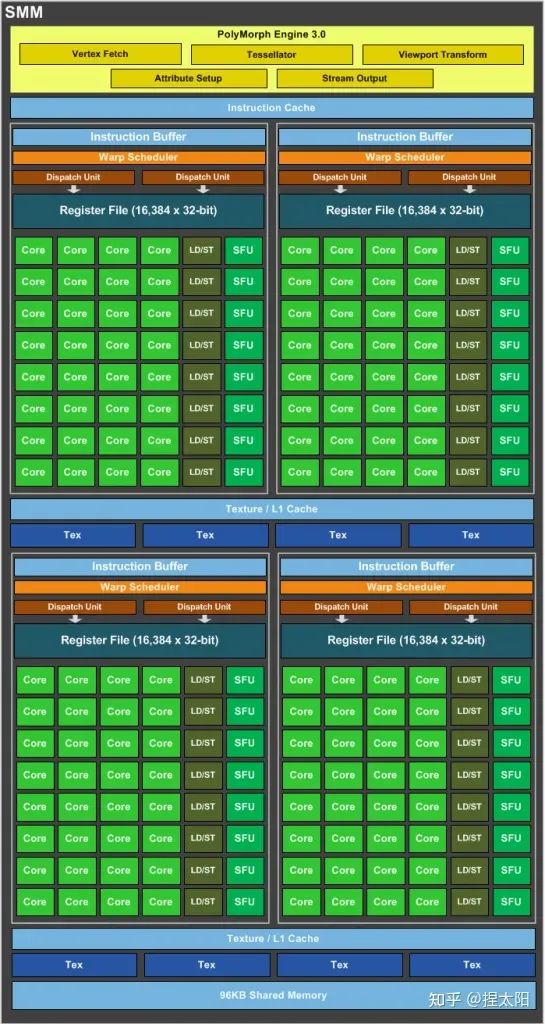

五、Maxwell架构

Maxwell架构的SM单元与Kepler架构相比,经历了显著变革。此代SM单元独特之处在于,它巧妙地模仿了4个Fermi架构SM单元的2x2排列方式,这一创新设计被称为SMM单元,展现了架构的先进性与高效性。

SMM采用创新的象限设计,拥有四个32核处理块,每块配备专用warp调度程序,实现高效并行处理。该设计能在每个时钟周期内迅速分派两条指令,大幅提升计算效率,满足高性能计算需求。

每个 SMM 单元提供

- 八个纹理单元(texture units)

- 一个多态引擎(polymorph engine-图形的几何处理)

- 专用寄存器文件和共享内存。

每个处理块中:

- 1个 Warp Scheduler,2 个 Dispatch Unit

- 绿色:32个 CUDA 内核

- 8个 LD/ST Unit

- 8个 SFU

CUDA内核总数自Kpler时代起,每组SM单元由192个精简至128个,尽管数量减少,但每组SMM单元逻辑控制电路更为丰富,实现了更精细的控制,展现了技术的优化与进步。

Maxwell:NVIDIA开发者博客盛赞的顶级CUDA GPU!其卓越性能超越以往,堪称史上最强。引领技术革新,成就无限可能,让你轻松驾驭最复杂计算任务,尽显科技魅力!

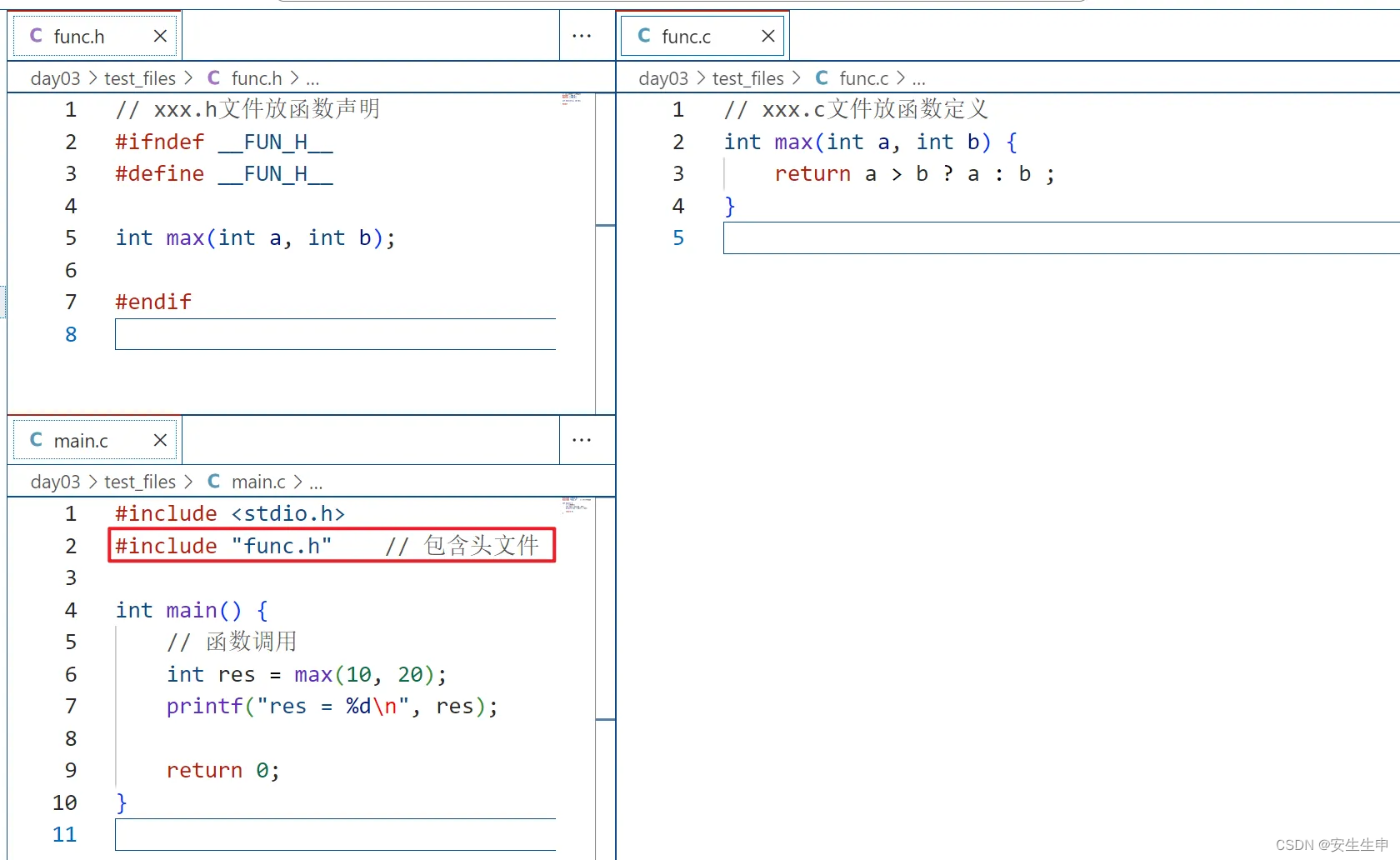

六、Pascal架构

pascal架构的GP100核心

这里有一个新概念:核心

NVIDIA架构各异,Pascal架构独领风骚,其核心阵容强大,包括GP100与GP102两大核心,展现卓越性能。

- GP100:3840个CUDA核心,60组SM单元;

- GP102:3584个CUDA核心,28组SM单元;

第2组数据存疑

核心为完整GPU模组,图示pascal架构GP100核心,内含60个SM单元,高效强大,尽显技术之精髓,为您带来卓越性能体验。

各类显卡产品灵活采用不同GP100配置,既可选择满配,亦可进行减配。例如,Tesla P100显卡便巧妙运用56个SM单元,实现高效能输出,展现卓越性能。

GP100核心的SM单元

每个SM单元精巧划分为两个Process Block,每个Block内藏高效处理机制,实现双重效能,助力计算速度飙升,性能卓越非凡。

- 1个 Warp Scheduler,2 个 Dispatch Unit

- 绿色:32个 CUDA 内核

- 黄色:搭载16个DP双精度运算单元,均匀分布于2条lane中,每条lane均配备8个单元,高效能计算尽在掌控。

- 8个 LD/ST Unit

- 8个 SFU

CUDA内核总数自Maxwell时代起,每组SM单元从128个精简至64个,显著提升了效率。这一代最亮眼之处在于重新引入了DP双精度运算单元,实现了性能与精度的双重提升。

制程工艺升级到了16nm,性能大幅提升,功耗却不增加。

七、Volta架构

Volta架构的GV100核心

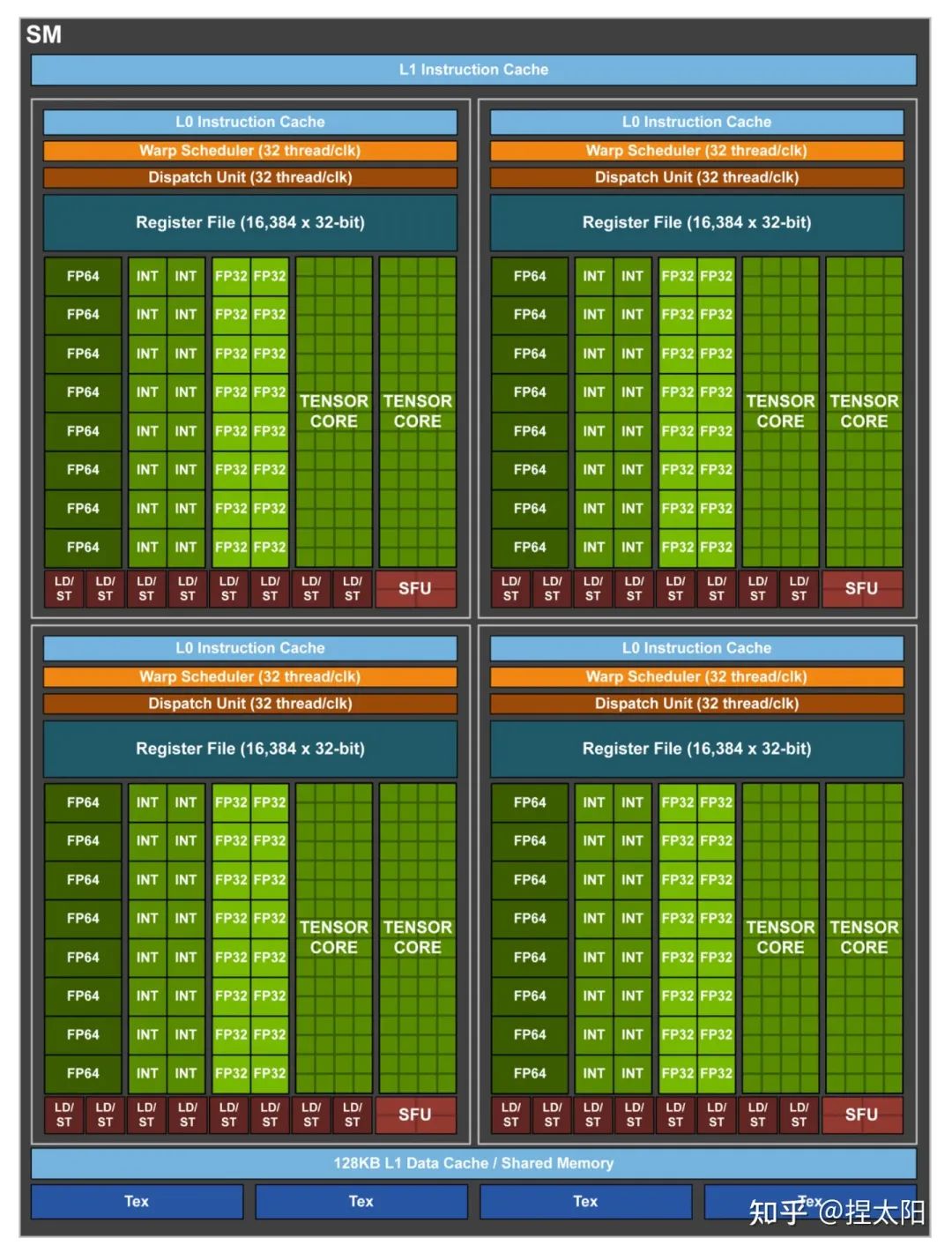

GV100核心的SM单元

每个SM单元精细划分为四个Process Block,每个Block独立运作,高效协同,确保数据处理速度与精度的双重提升。

- 1个 Warp Scheduler,1个 Dispatch Unit

- 8 个 FP64 Core

- 16 个 INT32 Core

- 16 个 FP32 Core

- 2 个 Tensor Core

- 8个 LD/ST Unit

- 4个 SFU

在前几代架构中:

一个CUDA 内核在每个时钟周期里只能为一个线程执行一条浮点或整数指令。

自Volta架构起,CUDA内核巧妙地被拆分为FP32与INT32两部分,此举之妙在于每一时钟周期内,浮点与整数指令得以并行执行,从而显著提升计算效率,为高性能计算领域带来革命性的进步。

Volta架构不仅擅长传统的单双精度计算,更独特的是新增了专用的Tensor Core张量单元,专为深度学习、AI运算等高效能需求而设计,性能卓越。

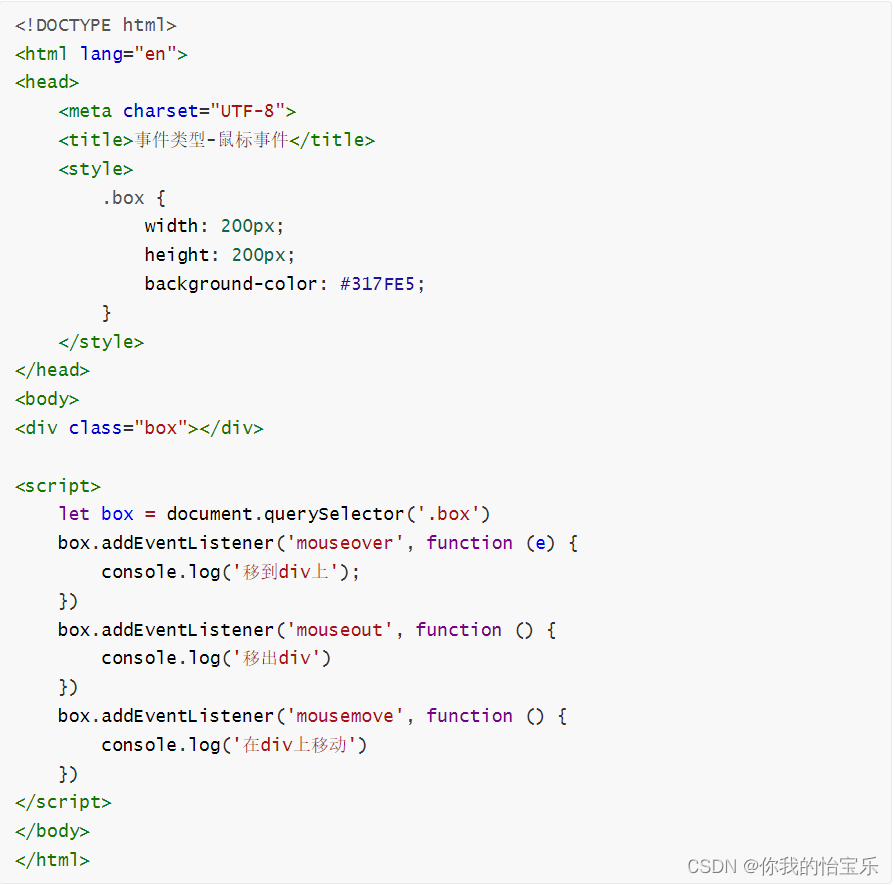

八、Turing架构

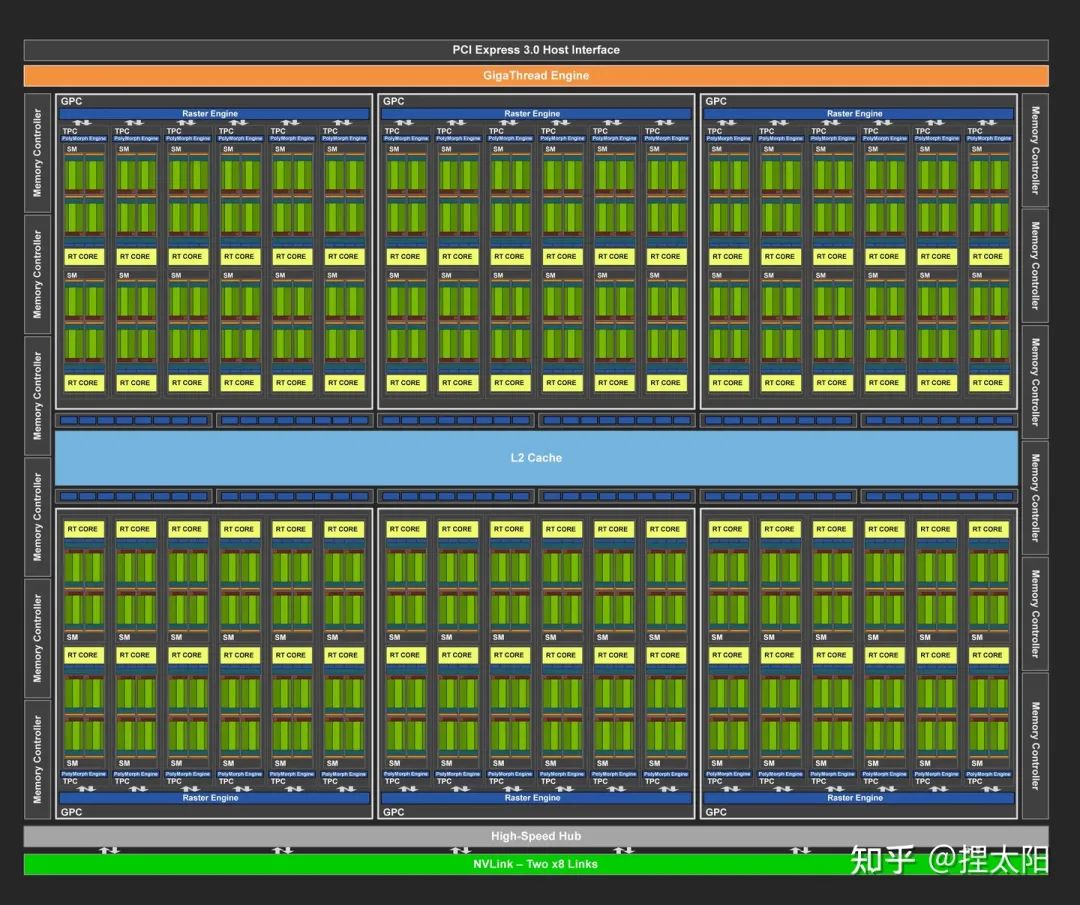

Turing架构的TU102核心

Turing架构目前一共有三种核心:

- TU102核心

- TU104核心

- TU106核心

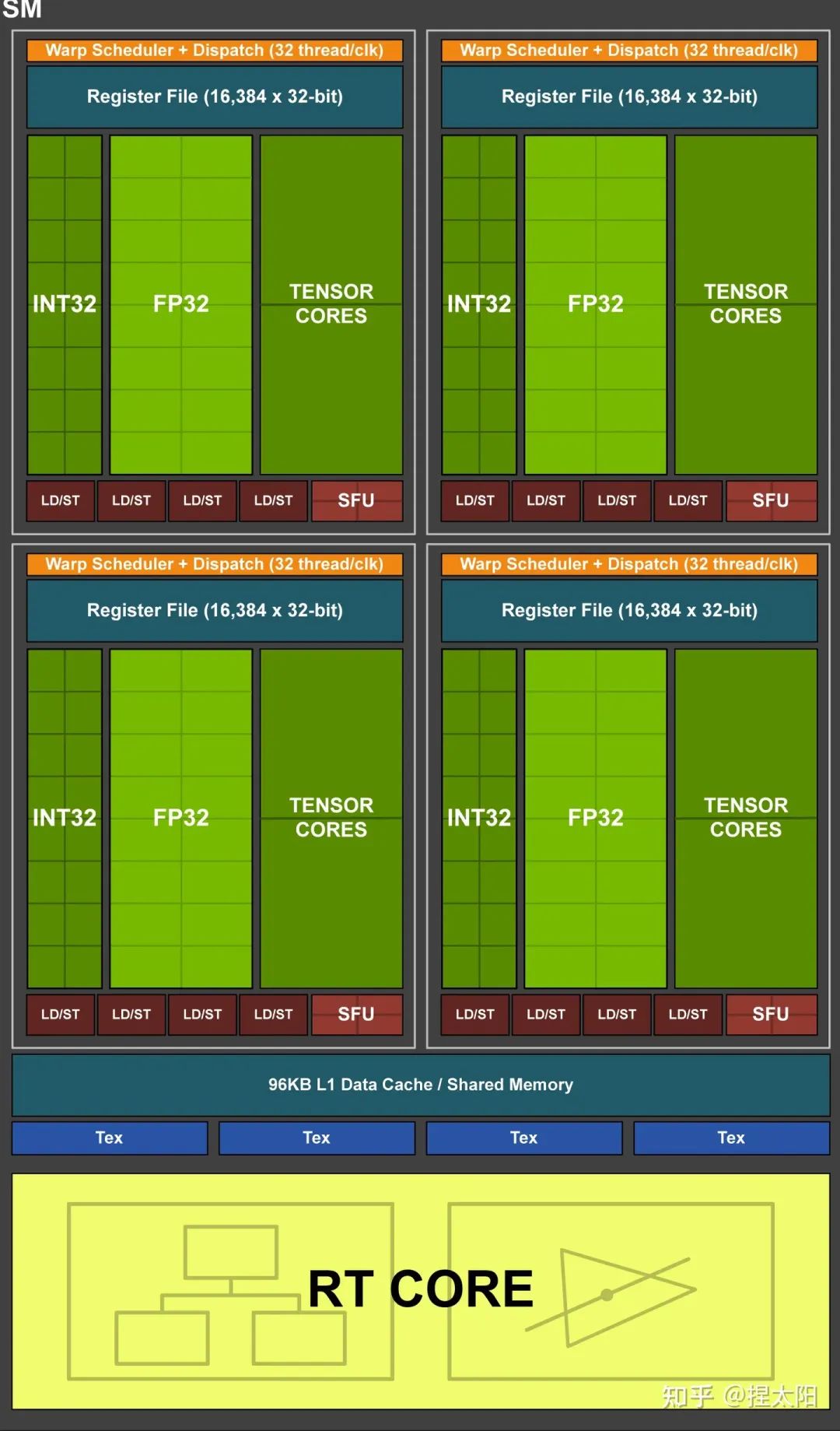

TU102核心的SM单元

每个SM单元有4个处理块,每个处理块中:

- 1 个 Warp Scheduler,1 个 Dispath Unit

- 16 个 INT32 Core

- 16 个 FP32 Core

- 2 个 Tensor Core

- 4 个 LD/ST Unit

- 4 个 SFU

这一代架构去掉了对FP64的支持。

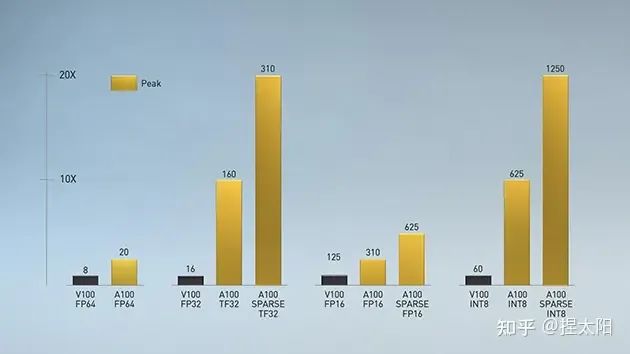

九、Ampere架构

Ampere架构的GA102核心

GA102核心的SM单元

每个SM单元分成4个处理块,每个处理块中:

- 1 个 Warp Scheduler,1 个 Dispatch Unit

- 8 个 FP64 Core

- 16 个 FP32 Core

- 16 个 INT32 Core

- 1 个 Tensor Core

- 8 个 LD/ST Unit

- 4 个 SFU

本代架构创新回归FP64 Core,更承袭Volta架构之精髓,推出NVIDIA第三代Tensor技术。我们秉持每代架构更新一次Tensor的承诺,不断推动技术革新,为您带来前所未有的计算体验。

-对此,您有什么看法见解?-

-欢迎在评论区留言探讨和分享。-