在进行电路设计时LDO是经常用到的,尤其在为芯片,晶振等敏感电路进行供电时应用更多,下面选取一款比较常用的LDO芯片,一起进行更深入的学习。

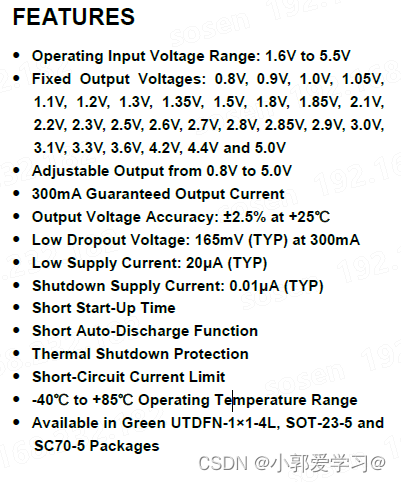

SGM2036特点简介

SGM2036,圣邦微一款比较常用的LDO芯片手册

可以先大致看一下芯片的特点,

输入电压的范围比较宽:1.6-5.5V;比较多的固定输出电压,在0.8-5V范围内是可以调节的;可以输出300mA的电流;输出电压精度较高;压降165mV;过热保护;过流保护;快速掉电等特点。从Features可以大致确定该LDO是否可以满足我们的需求,仔细阅读这些特点,对我们初步筛选是有益的。

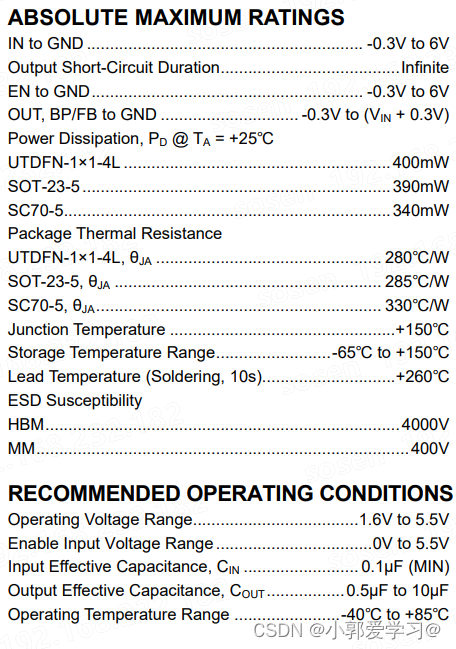

LDO的极限参数

极限参数包括输入引脚,EN引脚的输入电压,以及不同封装的LDO的耗散功率和不同封装对应的热阻,以及在进行电路设计的时候推荐的一些相关参数。

在选用或者进行参数设计的时候,LDO的功耗以及温升都是必须要考虑的。

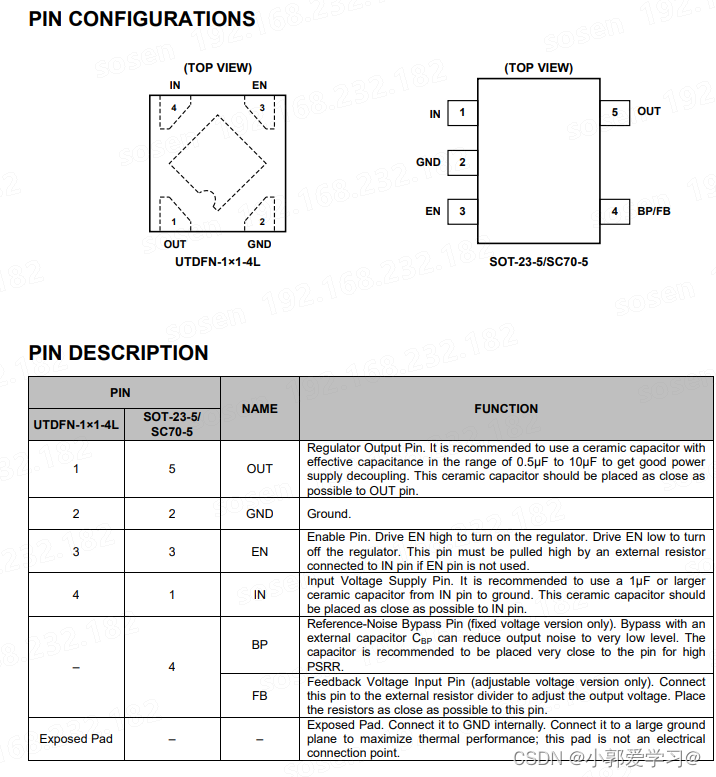

SGM2036引脚定义

从芯片手册中可以看到LDO的引脚封装,以及各个引脚的功能。

在OUT引脚手册建议使用1uF电容,但在实际应用中,会使用10-22uF电容的才能满足需求。

EN使能引脚,接高电平的时候,LDO才能正常工作。

IN输入引脚,同样需要接一个电容,减少一些高频干扰

BP/FB旁路,反馈引脚,外接合适的电容可以减少输出噪声,或者外接电阻可以调节输出电压。

LDO芯片底部通常还有一个散热焊盘与内部GND连接,有些芯片没有单独GND引脚,用这种焊盘当作GND引脚。

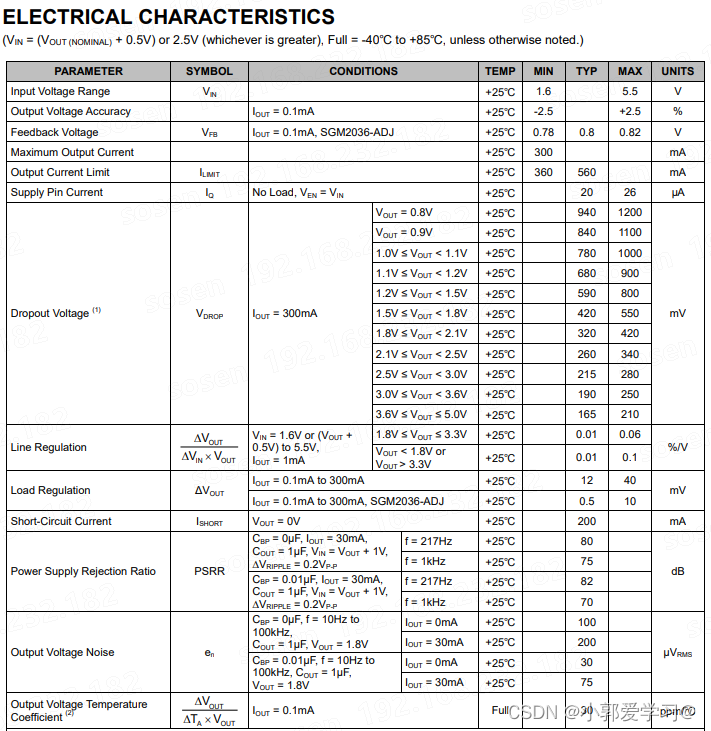

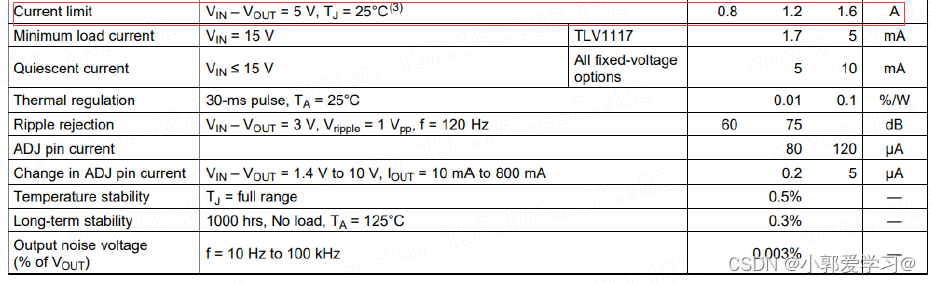

电气参数

电气参数有输入,输出电压,反馈引脚的电压,输出电流,供电电流,不同输出的情况下LDO的压降,负载调整率,线性调整率,电源抑制比等在上一篇博文中提到的参数。在进行设计选用的时候,电气参数也需要关注是否能满足我们的需求。

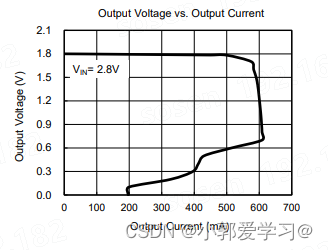

除了电气参数之外,还有一些电气参数的变化曲线,我们在选型应用的时候也应该注意用作参考,例如下面输出电压与输出电流的变化曲线

当长时间较大电流的输出时,LDO会产生比较多的热量,自行热关断进行保护,此时LDO停止工作,电流迅速下降,温度也会随之降低,在进行设计的时候应该避免LDO工作在超出额定电流的情况,避免过热损坏。

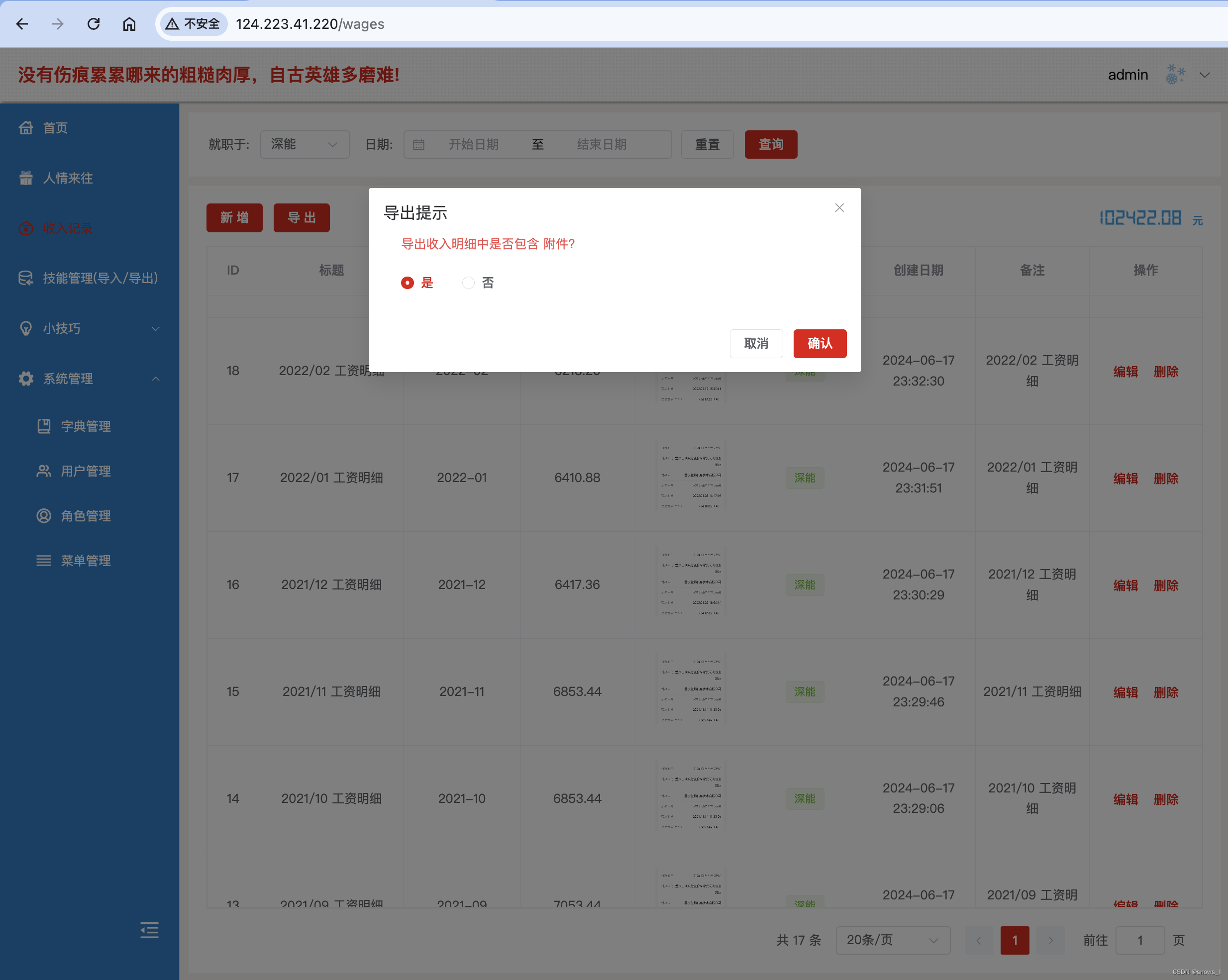

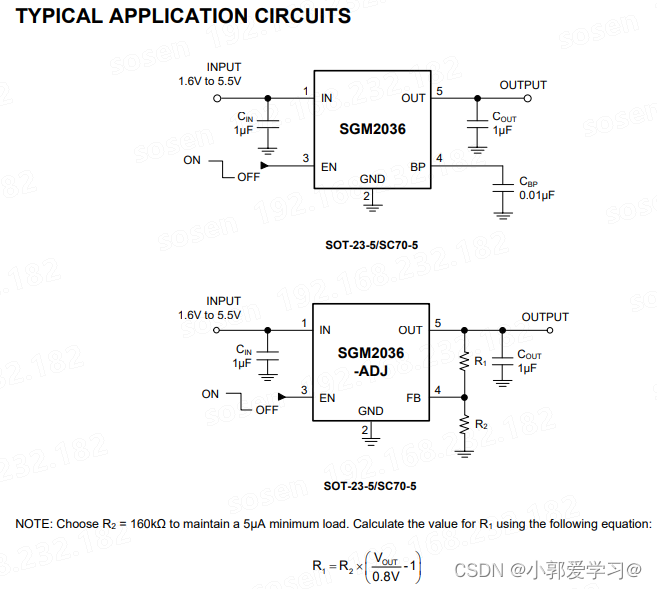

SGM2036推荐应用

上图是芯片手册提供的应用案例,当引脚4用作FB引脚使用的时候应该需要注意R1和R2的选择,阻值不能过大,因为引脚需要有一定的通流能力。

各种放大电路的接口是三极管或者是MOS器件,MOS管有漏电流, 漏电流是需要进行释放的,如果积累,影响MOS管的开关速度,进而会影响IO口输出高低电平的灵敏度,造成误动作。所以R2提供电流的泄放通路,不能过大,使环路反馈的稳定性得到保障。

思考题

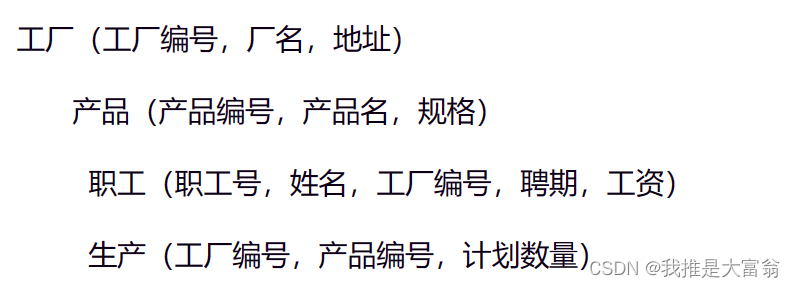

如果使用该款LDO设计:VIN3.3V,VOUT1.5V.能否正常输出250mA?

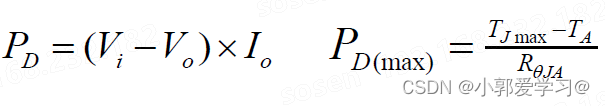

LDO能否满足设计要求,它的功率耗散是我们必须要考虑,即温升不能超过器件的结温。计算公式如下:

其中,Tjmax为节点最高温度

TA为环境温度

Rθja为节点温度到环境温度的热阻

通过计算我们可以看到,功率耗散的值已经超过上述三款封装的任何一个最大值,所以该设计是不符合要求的。

LDO芯片各外围器件作用

输入电容的作用

主要作用是对LDO的输入进行滤波,也可以抵消输入线较长时引入的寄生电感效应,防止电路产生自激振荡;所以LDO输入端一般采用两个电容并联的设计一大一小,较大的电容提供滤波作用,一般可以选取22uF左右,较小电容提供消除振荡作用,一般选用0.1uF,位置应该靠近输入引脚。

同时在选取电容的时候应该注意温度对电容特性的影响,电容都需要80%降额,钽电容需要50%的降额。可以选用,陶瓷电容X7R材质

并联多个不同容值的电容,滤波频带变宽,效果较好。

输出电容的作用

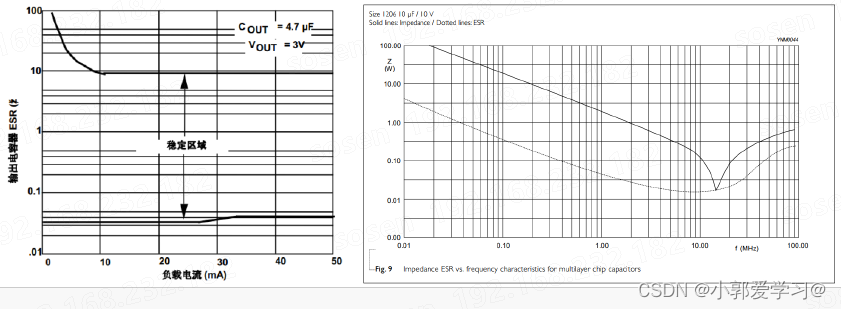

LDO的许多性能都受到输出电容的影响,其中电容值以及ESR对电路频率响应的影响是最主要的,输出电容以及ESR选择不当,非常容易引起电路的自激振荡。

一般也是一大一小进行并联,可以选用22uF左右,较小电容提供消除高频噪声的作用,一般选用0.1uF,位置应该尽量靠近引脚。

在选择电容的时候还需要考虑温度对容值以及ESR的影响,应该保证在整个温度范围内电路都是稳定的。

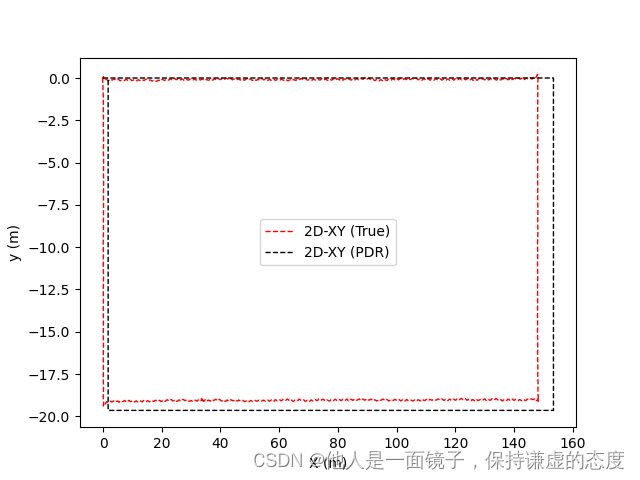

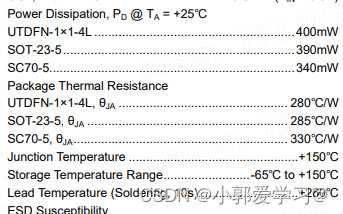

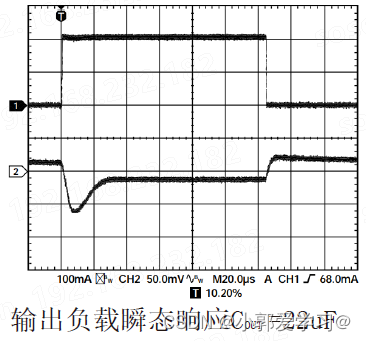

下图是不同容值的输出电容对负载响应的影响,在上一篇文章也有提到。

因为LDO控制环路的带宽有限,因此输出电容必须提供快速瞬变所需要的大多数负载电流

1uF电容产生约90mV的负载瞬变,

10uF电容将负载瞬变降低至约80mV

22uF电容将负载瞬变降低至约60mV,LDO控制回路就可捕捉并主动降低负载瞬变。

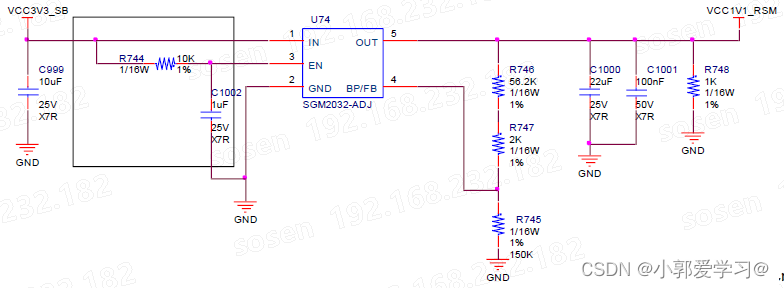

具体应用

1. 上述实例应用中可以看到使能引脚使用RC电路进行延时,可以满足缓启动的功能;

2. 输入电容10uF,也可以并联一个小的电容,以减少干扰;

3.在FB引脚反馈电容的选取是150K,是可以满足引脚泄放电荷的要求的;

4. 可以看到电路中加了一个1k的假负载

从参数手册中可以看到需要一个比较小的负载电流(1.7mA),进行维持负反馈是一个闭环系统,闭环增益,保持环路稳定性。因此增加一个假负载满足最低负载的要求。

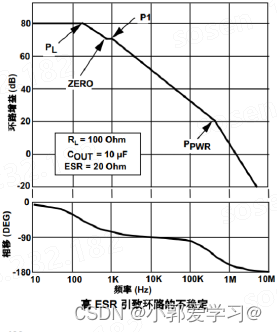

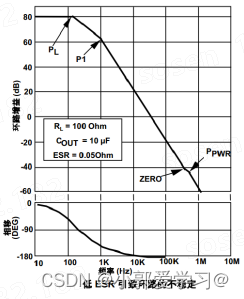

输出电容ESR对环路稳定性的影响

高的ESR将零点移到一个较低的频率;

这样增大了环路带宽,因而允许极点PPWR在0dB频率之前增加更多的相移;

由其他极点产生的相移(图中未进行标注)使得的ESR值往往会造成环路的不稳定;

低ESR将零点移至一个较高的频率;

零点出现的频率比0dB频率高1个十倍频以上;

由于零点在0dB下未添加任何正相移,因此两个低频极点将会导致相移达到-180°(不稳定)。

输出电容不能并联太多电容,电容并联较多,会有低ESR,可能会影响环路稳定性。

现在大部分LDO内部已经做了相位补偿。

我们一起探索了较多参数,但是LDO在实际应用中并没有想象的那么复杂,一般设计都是可以满足要求的,我们只是在理论上多一些了解。

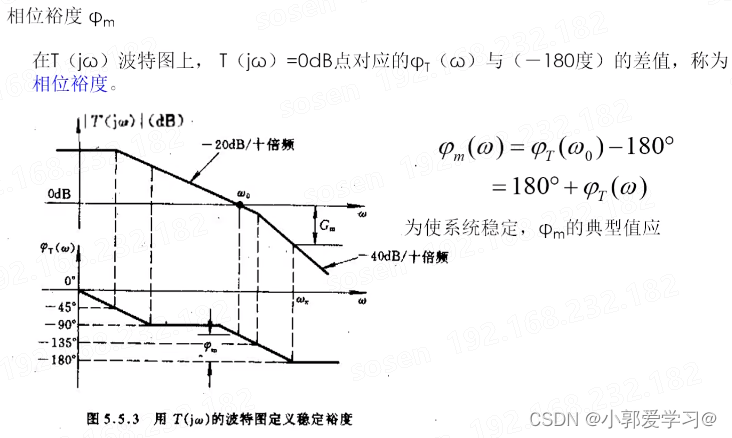

相位裕度的定义

波特图中,增益为零对应的相移与-180°的差值叫做相位裕度,这个值应该大于45°才能保证环路的稳定性。

电路优化

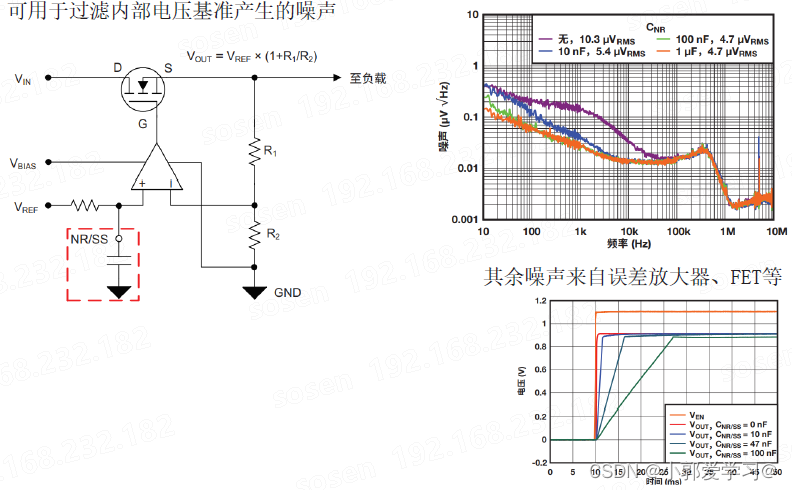

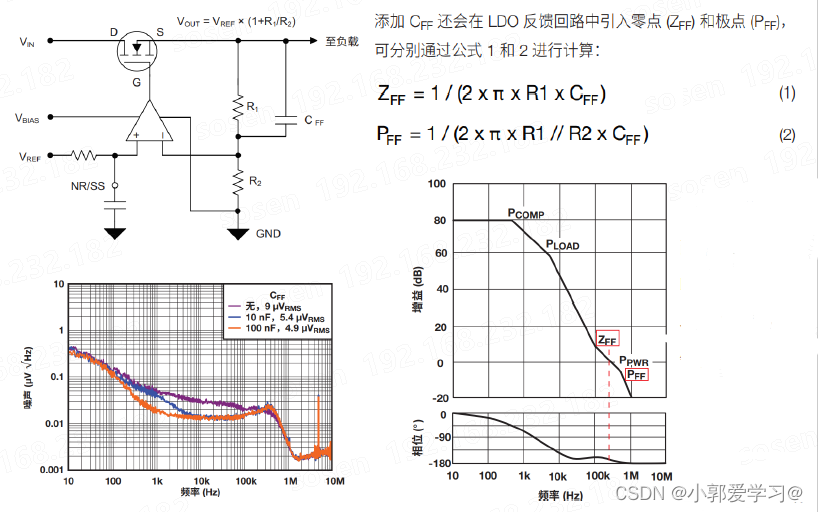

添加降噪电容

在LDO的误差放大器引脚添加降噪电容,用于过滤内部电压基准产生的噪声。不同容值的电容产生的效果也会有所不同,效果可以在下图中看到。

降噪电容,电压基准产生的干扰已经滤除。0.1uF的退耦半径2厘米左右,要靠近管脚摆放。

除了滤除干扰外还有第二个作用是:改善上电的时序,RC滤波电路,参考电压的上电变缓,LDO正常工作需要参考电压提供基准。可以使LDO上电过缓,避免浪涌电流的冲击,比较有意义。

添加电容CFF

实际使用中还会添加电容CFF进行电路优化

在负载与反馈电阻之间添加电容CFF,会在LDO反馈回路中引入零极点。这样增加了相位裕度,改善负载瞬态响应,输出将减少振铃并更快稳定。但是改善是有限度的,具体电路应该具体分析。

其他问题

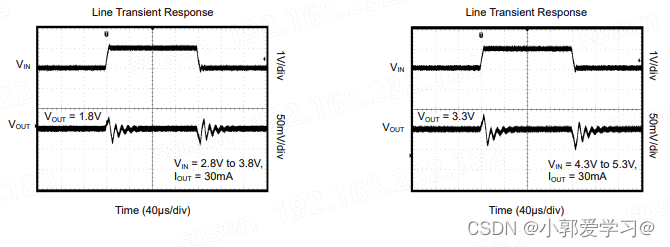

如果在设计LDO时,输出不稳或者关断,我们可以从以下方面进行思考

1.过载导致过温,芯片自行进行热保护,

2.输入电压有较大的波动

上图可以看出LDO的瞬态响应,如果输入电压有较大的波动,输出震荡会更加严重,甚至不能正常启动

3.环路不稳,导致震荡,电压跌落。输出电容的ESR不合适可能会导致问题的出现。

4.不符合压差,LDO不能够进行调节稳压。

LDO电路的PCBLayout

在进行布局布线的时候:

电容按照先大后小顺序就近摆放;

输入/输出布线路径宽度,换层过孔数量要满足电源电流的大小;

较大的GND焊盘需要打过孔,方便进行散热,背面应该开阻焊窗;

输入/输出的GND尽量连接在一起,保持完整的回流;

总结来说:一点接地,去耦支路尽可能短,大电流线尽可能短,同时做好散热设计。