(1)顶层文件:

module tft_colorbar(input clk ,input reset_n ,output hsync ,output vsync ,output [23:0] rgb_tft ,output tft_bl ,output tft_clk ,output tft_DE );wire locked ;wire clk_33M ;wire [23:0] data_in ;wire [9:0] hang ;wire [9:0] lie ;wire [23:0] data ;assign data_in = data ;PLL_33M PLL_33M_inst

(.clk_33M (clk_33M ), .resetn (reset_n ), .locked (locked ), .clk_in1 (clk )

);tft_ctrl tft_ctrl_inst

(.clk_33M (clk_33M ),.reset_n (locked ),.data_in (data_in ),.hang (hang ),.lie (lie ),.hsync (hsync ),.vsync (vsync ),.rgb_tft (rgb_tft ),.tft_bl (tft_bl ),.tft_clk (tft_clk ),.tft_DE (tft_DE )

);data_gen data_gen_inst

(.hang (hang),.lie (lie),.clk_33M (clk_33M),.reset_n (locked),.data (data)

);endmodule

(2)仿真文件:

`timescale 1ns / 1psmodule tft_colorbar_tb;reg clk ;

reg reset_n ;wire hsync ;

wire vsync ;

wire [23:0] rgb_tft ;

wire tft_bl ;

wire tft_clk ;

wire tft_DE ; initial clk = 1'd1;

always#10 clk = ~clk;initial beginreset_n <= 1'd0;#22;reset_n <= 1'd1;#20_000_000;$stop;

endtft_colorbar tft_colorbar_inst

(.clk (clk ),.reset_n (reset_n ),.hsync (hsync ),.vsync (vsync ),.rgb_tft (rgb_tft ),.tft_bl (tft_bl ),.tft_clk (tft_clk ),.tft_DE (tft_DE ));endmodule

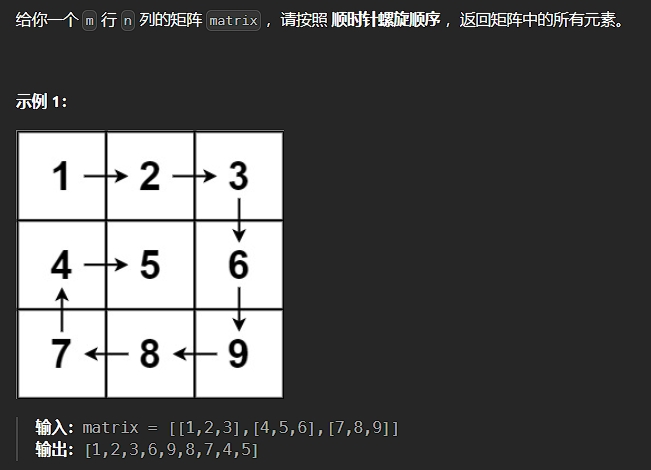

(3)RTL视图:

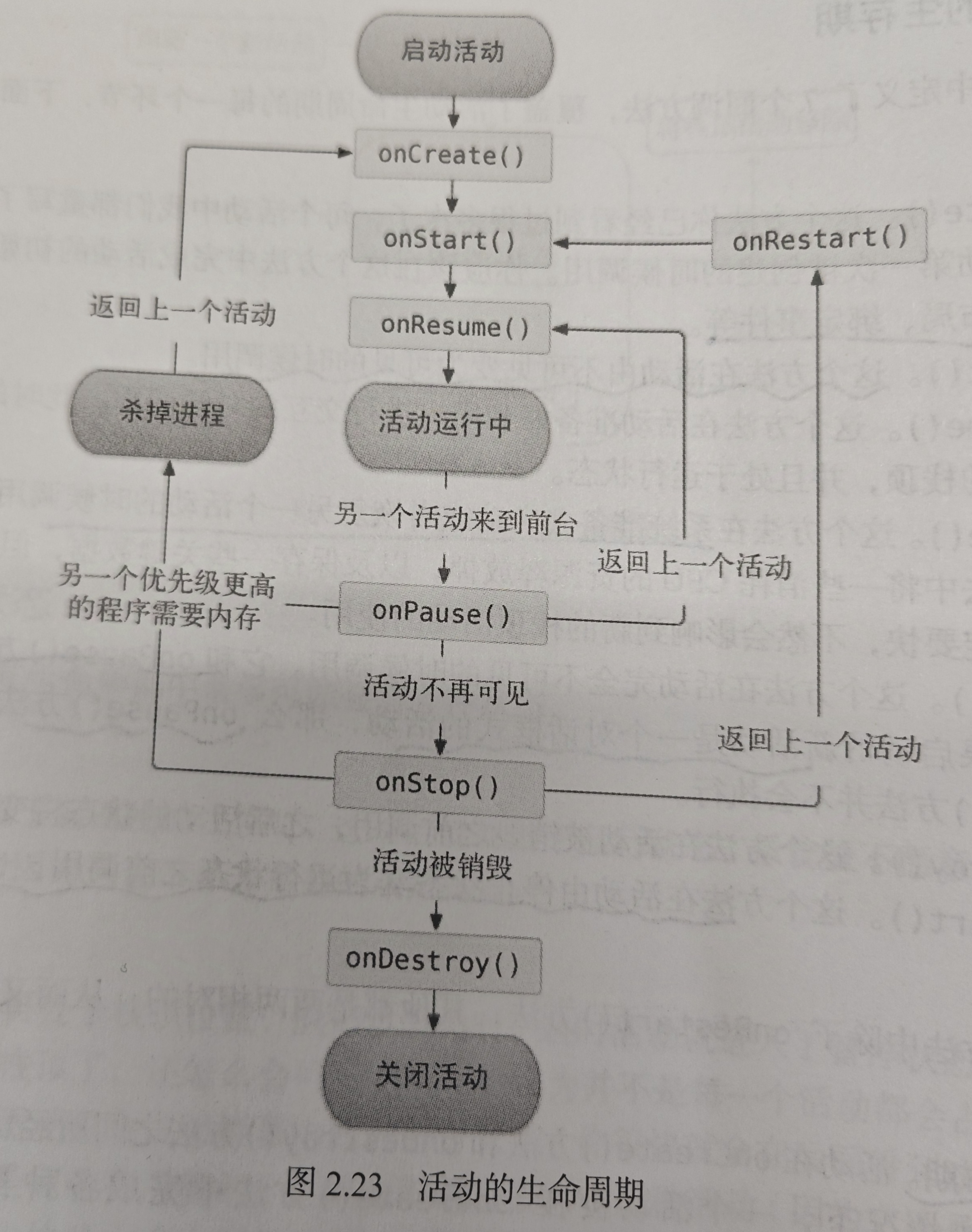

(4)仿真波形:

- 在第22秒拉高reset_n

- 在第4380ns时,locked信号拉高,在这之后测试clk_33M信号,确定它的频率为33MHz

- 在第128个像素点,行同步信号拉高

- 在每一行计数器清零后,场计数器加一

- 在场计数器计数到2时,场同步信号拉高

- 在第35行第216个像素点时,有效信号被拉高,行、列信号开始输出,而由于data生成模块采用时序逻辑的原因,data[23:0]会滞后一个时钟周期。

- 整体来看,rgb_tft[23:0]在每一行都会呈现赤橙黄绿青蓝紫黑白灰10色交替出现的现象,另外由于数据有效信号data_vaild的存在,每一行的灰色不会因为时序逻辑而蔓延到有效区域外。

(5)因为本人不小心把A7开发板fpc底座拔坏了,因此改用AC620进行实验,使用36pin的排针连接,颜色模式改为RGB565,修改代码如下:

module tft_colorbar(input clk ,input reset_n ,output hsync ,output vsync ,output [15:0] rgb_tft ,output tft_bl ,output tft_clk ,output tft_DE );wire locked ;wire clk_33M ;wire [15:0] data_in ;wire [9:0] hang ;wire [9:0] lie ;wire [15:0] data ;assign data_in = data ;PLL_33M PLL_33M_inst (.areset ( ~reset_n ),.inclk0 ( clk ),.c0 ( clk_33M ),.locked ( locked )

);tft_ctrl tft_ctrl_inst

(.clk_33M (clk_33M ),.reset_n (locked ),.data_in (data_in ),.hang (hang ),.lie (lie ),.hsync (hsync ),.vsync (vsync ),.rgb_tft (rgb_tft ),.tft_bl (tft_bl ),.tft_clk (tft_clk ),.tft_DE (tft_DE )

);data_gen data_gen_inst

(.hang (hang),.lie (lie),.clk_33M (clk_33M),.reset_n (locked),.data (data)

);endmodule

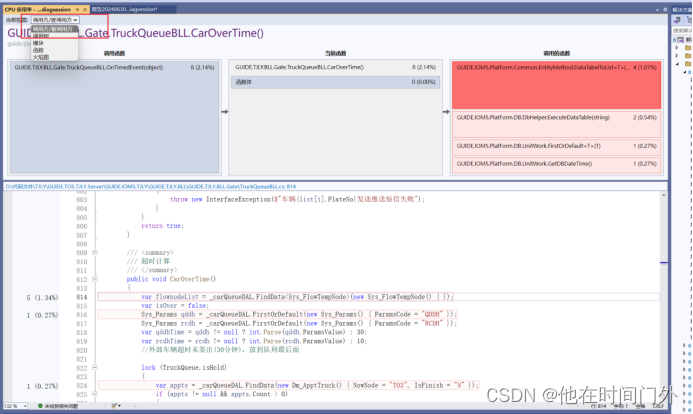

(6)引脚绑定: