目录

1.使用说明

2.实例化代码

3.参数解释

4.端口连接

1.使用说明

IBUFDS_GTE3 是Xilinx FPGA 中用于高速接口的差分时钟信号输入缓冲器。

BUFDS_GTEx,x=2/3/4(不同系列的FPGA x的值不同),其中UltraScale使IBUFDS_GTE3作为GTY bank的差分缓冲器,用于高速BANK(GTY BANK)的两路参考时钟输入。

2.实例化代码

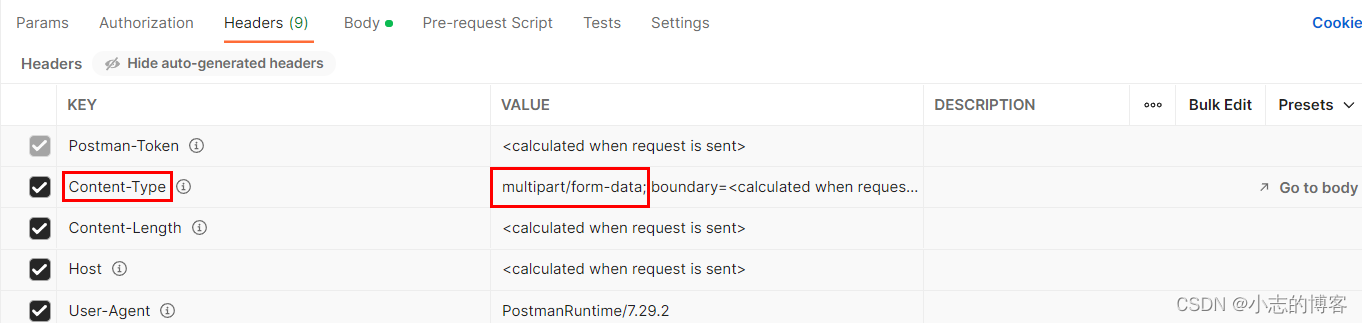

打开Vivado左侧导航栏中的"Language Templates",搜索“IBUFDS_GTE3”,找到可直接调用的原语模块实例化代码

下面是 IBUFDS_GTE3 实例化的一个例子:

//差分时钟输入缓冲

IBUFDS_GTE3 #(.REFCLK_EN_TX_PATH(1'b0), // Refer to Transceiver User Guide.REFCLK_HROW_CK_SEL(2'b00), // Refer to Transceiver User Guide.REFCLK_ICNTL_RX(2'b00) // Refer to Transceiver User Guide)

IBUFDS_GTE3_inst (.O(ref_clk), // 1-bit output: Refer to Transceiver User Guide.ODIV2(), // 1-bit output: Refer to Transceiver User Guide.CEB(1'b0), // 1-bit input: Refer to Transceiver User Guide.I(ref_clk_p), // 1-bit input: Refer to Transceiver User Guide.IB(ref_clk_n) // 1-bit input: Refer to Transceiver User Guide); 3.参数解释

.REFCLK_EN_TX_PATH(1'b0):该参数控制TX路径参考时钟的使能状态。这里设为1'b0,表示禁用TX路径参考时钟。

.REFCLK_HROW_CK_SEL(2'b00):该参数选择高性能行时钟。值2'b00通常表示默认选择,即未选择特定的替代行时钟。

.REFCLK_ICNTL_RX(2'b00):该参数配置RX时钟输入控制。值2'b00表示默认的控制设置。

4.端口连接

.O(ref_clk):输出端口,提供缓冲后的差分时钟输出。.ODIV2():输出端口,提供输入时钟的二分频版本。实例中未连接信号线。.CEB(1'b0):时钟使能输入端口。低电平有效,1'b0表示时钟使能被激活(使能)。.I(ref_clk_p):正向差分时钟输入。.IB(ref_clk_n):负向差分时钟输入。

![C语言程序设计-[1] 基础语法](https://i-blog.csdnimg.cn/direct/823d88ede568451c8b3a8f0a464ebb84.png)