在现代电子工程领域,数据传输和同步技术是确保信息准确、高效传递的关键。FPGA间的高速数据传输是实现复杂系统功能的关键技术之一。本文将基于移知公开课《FPGA之间数据传输的讨论》的内容,探讨FPGA间数据传输的技术细节和面临的挑战,帮助读者理解数据传输中的同步问题及其解决方案。

想要观看视频版公开课内容,可联系小编获得观看链接!

一、数据传输的挑战

在数据传输过程中,我们经常遇到两个主要问题:数据宽度和时钟同步。数据宽度问题涉及到数据在传输过程中的带宽限制,而时钟同步问题则关乎数据在不同设备间准确传递的时间协调。

二、同步方式

在FPGA间进行数据传输时,主要有两种同步方式:系统同步和源同步。

系统同步

系统同步通常依赖于一个统一的时钟信号来协调多个FPGA之间的数据交换。这种方式的优点是实现相对简单,但可能因为时钟传播延迟而导致数据同步问题。这种方式有两种实现形式:

多设备间同步:使用统一的时钟信号来减少施工期间。

云同步:数据和时钟信号一同从同一个应用中提取。

源同步

源同步是一种更为复杂的技术,它使用独立的时钟源,并通过特定的同步器来确保数据在不同FPGA间的准确传输。这种方式适用于对数据传输速率和同步精度要求极高的应用场景。

源同步是一种在FPGA设计中常用的数据传输同步技术。在源同步系统中,数据的采样时钟是由数据发送方(源)提供的,并且数据的时钟与数据一起传输到接收方。这种方式的优点包括:

简化接收端设计:接收方不需要复杂的时钟恢复电路。

减少时钟偏差:因为时钟和数据一同传输,减少了由于时钟在PCB板上传播引起的偏差。

源同步涉及到以下几个关键组件:

高品质时钟(High-Quality Clock):保证数据传输的稳定性。

输出和输入同步器(OSDS和ISS):用于数据的串行化和并行化。

三、数据处理

理想的数据处理流程是直接将电池输出的采样数据写入寄存器,然后进行后续处理,尽量避免中间的组合逻辑,以减少延迟。

数据传输的技术实现

采样与寄存

在技术端,使用收到的时钟信号来采集对应的数据,完成采样过程。这要求数据处理过程中,数据直接写入寄存器,避免中间逻辑。

分时传输

面对数据宽度较大的问题,可以采用分时传输技术,将宽数据分批次传输,每次只传输数据的一部分,从而解决带宽限制问题。

消除时钟偏差

为了解决时钟偏差问题,可以设计特定的电路来消除时钟之间的偏差,例如使用相位锁定环(PLL)或延迟锁定环(DLL)来调整时钟相位。

源同步方案的实现

源同步方案通过使用输出同步器(OSDS)和输入同步器(ISS),以及高频和低频时钟的配合,实现数据的高速传输。这种方法虽然复杂,但能够提供高效的数据传输速率。

时序约束的重要性

在FPGA间的数据传输中,时序约束是确保数据准确性的关键。通过设置合理的时序约束,可以保证数据在传输过程中的时钟同步,减少时钟偏差带来的影响。

四、讨论中的要点

采样时钟的设置

采样时钟通常被定义为虚拟时钟,以便在进行IO延迟设置和时序约束时能够引用。

消除时钟偏差电路

使用特定的电路设计来消除时钟偏差,例如通过反馈机制和相位调整来补偿时钟延迟。

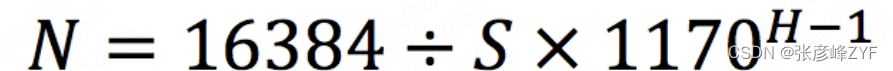

数据宽度与传输速率

在处理大宽度数据时,需要考虑分时传输和数据的串行化与并行化,以适应FPGA的IO接口。

源同步方案的约束要点

在源同步方案中,需要特别注意数据的时钟和数据的相位关系,以及如何通过IO延迟来微调数据的采样点。

FPGA间的高速数据传输是一个复杂但至关重要的技术领域。随着电子系统对数据处理能力的要求日益提高,工程师们需要不断探索新的同步技术和传输方案,以满足高速、高精度的数据传输需求。通过深入理解FPGA间数据传输的技术细节,我们可以更好地设计和优化电子系统,推动技术的进步。