计算机体系结构:冯诺伊曼 哈佛

冯·诺依曼结构

冯·诺依曼结构,也称冯·诺依曼模型或普林斯顿结构,是根据冯·诺依曼提出的存储程序概念设计的计算机体系结构。其主要特点包括:

- 存储程序:指令与数据都以二进制形式储存在存储器里,且两者在存储器中并无物理上的区分,都是由0和1组成的代码序列。计算机在运行时,能够自动地从存储器中取出指令并执行。

- 顺序执行:指令根据其存储的顺序执行,即使相关数据已经准备好,也必须逐条执行指令序列。

- 五大部件:由运算器、存储器、控制器、输入设备和输出设备五大部件组成计算机系统,并规定了这五部分的基本功能。

- 二进制表示:采用二进制形式表示数据和指令,这是计算机能够高速自动运行的基础。

冯·诺依曼结构的主要优势在于其简单性和通用性,使得计算机能够执行各种复杂的任务。然而,其也存在一些局限性,如指令和数据的串行执行限制了计算机的处理速度,以及存储器的线性编址方式可能导致高级语言与机器语言之间的语义差距较大。

哈佛结构

哈佛结构是一种将程序指令存储和数据存储分开的存储器结构,是一种并行体系结构。其主要特点包括:

- 独立存储:程序存储器和数据存储器是两个独立的存储器,每个存储器独立编址、独立访问。这种分离的程序总线和数据总线可允许在一个机器周期内同时获得指令字(来自程序存储器)和操作数(来自数据存储器),提高了执行速度和数据的吞吐率。

- 并行处理:由于程序和数据存储在两个分开的物理空间中,因此取址和执行能完全重叠,提高了系统的并行处理能力。

- 高带宽:哈佛结构提供了较大的存储器带宽,使数据的移动和交换更加方便,尤其适用于数字信号处理等需要高速运算的场合。

哈佛结构的主要优势在于其高效的并行处理能力和较高的数据吞吐率,这使得它在需要高速运算的场合中得到了广泛应用。然而,其设计也更为复杂,需要更多的硬件资源来支持。

总线:

地址总线:

数据总线:

控制总线:读写 片选

CPU(中央处理单元)

PC:程序计数器 指向正在执行的下下条指令。默认值为0,默认自加操作。

LR:连接寄存器 保存函数的返回地址。

SP:栈指针寄存器,指向栈顶。

CPSR:当前程序状态寄存器 。

进/借位,结果为 负/零,中断使能。大小端配置 ,工作模式。

SPSR:保存程序状态寄存器,使CPSR的备份。

Cache:缓存 I(指令) D (数据)

——cache替换原则 替换最早未使用的

MMU:内存管理单元 虚拟地址到物理地址的转换

二、SOC(片上系统)S3C2440

多核异构:多核异构指的是在一个处理器或系统中存在多个核心(CPU或处理单元),且这些核心在架构、指令集、时钟频率、功耗特征等方面存在差异。这种设计使得处理器能够根据不同的任务需求,灵活地分配计算资源,以达到更高的计算效率和更低的功耗。

RISC:精简指令集(用20%实现80%的功能)相对的概念、

CISC:复杂指令集

ARM9:

Cortex-A 消费类电子——低功耗

Cortex-R 实时性(类似于汽车刹车)---航空航天军工

Cortex-M 高性能(STM32) ---偏控制

指令集:ARM V4

三、半导体器件

四、流水线:

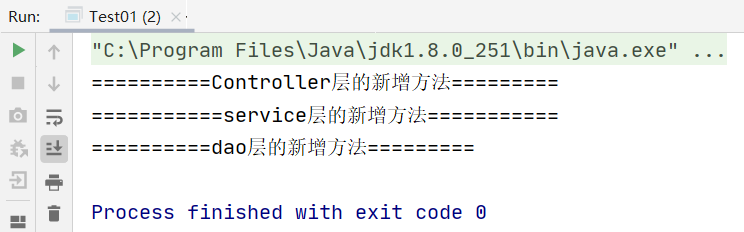

程序执行的过程:

预取 译码 执行

三级流水线

发生跳转就会导致骑不是最佳的

#+数字 是立即数

—— 一个数字(按位取反)中或将其循环右移偶数位后的所有的1都能放进低8位中

0xff00(循环右移最简单的的情况)

0xff00ffff

所以只有特别明显的立即数可以使用。

cmp之类的条件码

机器编码