- 题目:A Research Retrospective on the AMD Exascale Computing Journey

- 时间:2023

- 会议:ISCA

- 研究机构:AMD

- 题目:Realizing the AMD Exascale Heterogeneous Processor Vision

- 时间:2024

- 会议:ISCA

- 研究机构:AMD

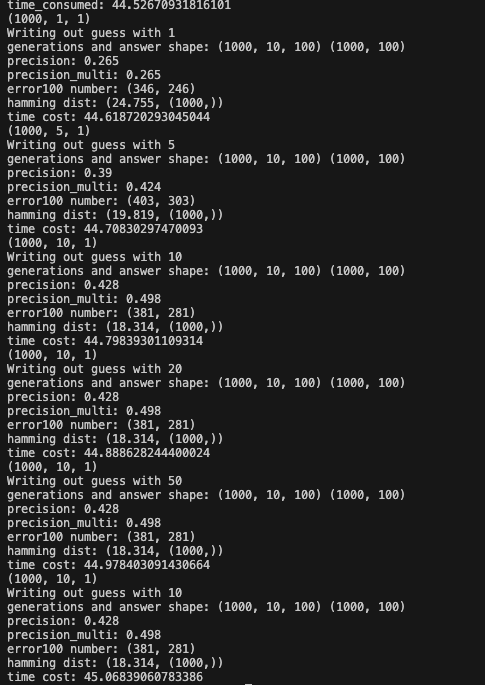

EHPv1 2012

最开始EHP,是基于DRAM堆叠+silicon interposer

EHPv2 2014

开始有chiplet的概念,4个CPU chiplet (CCD) + 1个IO Die + 16层DRAM堆叠+silicon interposer

当然CPU部分还是用的有机衬底

EHPv3 2016

DRAM stack高度从16降到8,GPU和CPU下面都使用active interposer,GPU资源翻倍

EHPv4 2018

为了降成本,使用了passive interposer,但是封装面积更大了,CPU CCD的数量从v3的8个降低到2个

问题在于IO Die的IF接口是为了CPU的DDR级别带宽设计的,对于GPU HBM级别的带宽支持有困难,而且两个GPU die离得比较远,通信开销更大,而且CPU访问HBM也很远

The overall chiplet topology creates a relatively long path from the CPU chiplets to the HBM, requiring two die-todie IF hops (plus the data fabric/network-on-chip traversals within the IOD and GPU) to get to the memory,

EHPv4的封装面积也没有得到充分利用

MI300A

- XCD:5nm工艺,GPU计算引擎,CDNA 4架构

- CCD:5nm工艺,Zen4架构,一个CCD有8核+32MB L3

- IO die:memory-side cache共256MB