UART串口接收模块

背景

在之前就有写过关于串口模块的文章——《串口RS232的学习》。工作后很多项目都会用到串口模块,又来重新理解一下FPGA串口接收的代码思路。

关于串口相关的参数,以及在文章《串口RS232的学习》中已有详细的描述,这里就不过多的赘述了。

uart_rx模块理解

一般来说,用FPGA实现串口数据的接收,其模块的输入和输出大多都会写成以下形式。

在该模块的输入端,时钟和复位信号不必多说;FPGA模块的Rx信号则是通过串口线与上位机的Tx端相连接进行数据的传输。

而在该模块的输出端,Rx_ready信号代表一帧数据(起始位+数据+校验位+停止位,校验位不一定有)的接收完成,当上位机传输了一帧数据之后,Rx_ready信号会被拉高一个时钟周期,代表接收到了一帧数据;而Rx_data一般代表一帧数据中的8位数据,当Rx_ready信号被拉高时,Rx_data=上位机发送过来的8位数据。

uart_rx接收数据后的处理

假设上位机向我们的FPGA板卡发送9 Byte的数据,这9 Byte的数据分别为8'H11、8'H22、8'H33、8'H44、8'H55、8'H66、8'H77、8'H88、8'H99。我们应该如何接收呢?

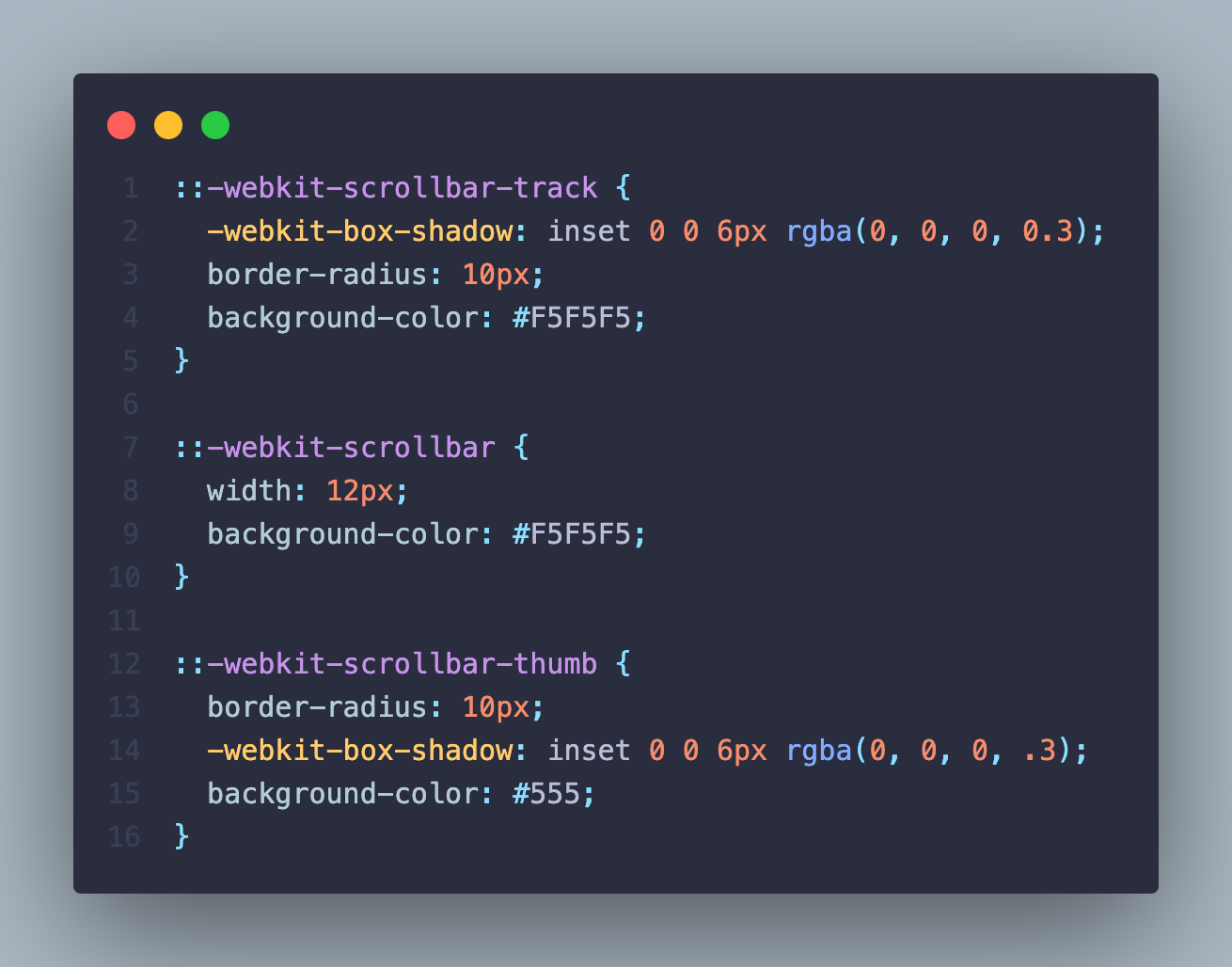

在不考虑超时处理和校验处理的情况下,可以用以下代码来接收上位机向FPGA板卡发送的数据。

parameter MAX_RX_DATA_NUM = 10;//接收最大的字节个数,假设为10reg [1:0] r_rx_ready; //缓存数据便于采集沿

reg [15:0] rx_data_length; //接收数据的长度

reg [MAX_RX_DATA_NUM*8-1:0] rx_data_sum; //每个字节为10Bit,10字节所占的Bit为10*8//当r_rx_ready=2'b01时,代表一帧数据的接收完成。

always(posedge clk or negedge rst_n)beginif(!rst_n)r_rx_ready <= 2'b00;elser_rx_ready <= {r_rx_ready[0],rx_ready}

end//当r_rx_ready=2'b01时,代表接收到了一个字节的数据,接收数据的长度+1;

//由于接收9字节的数据,则rx_data_length的最大值为8

always(posedge clk or negedge rst_n)beginif(!rst_n)rx_data_length <= 16’b0;else if(r_rx_ready==2'b01)rx_data_length <= rx_data_length + 1'b1;elserx_data_length <= rx_data_length;

end//将从上位机接收到的9字节数据,先发送的数据存入高位,按序依次放入rx_data_sum中

//此时,rx_data_sum[79:72]=8'H11;rx_data_sum[71:64]=8'H22;.....rx_data_sum[15:8]=8'H99;rx_data_sum[7:0]=8'H00;

always(posedge clk or negedge rst_n)beginif(!rst_n)rx_data_sum <= 'd0;else if(r_rx_ready==2'b01)rx_data_sum[((MAX_RX_DATA_NUM-rx_data_length)*8-1)-:8] <= rx_data;elserx_data_sum <= rx_data_sum;

end