FPGA时序分析和约束学习笔记(3、Timequest时序路径详解和优化)

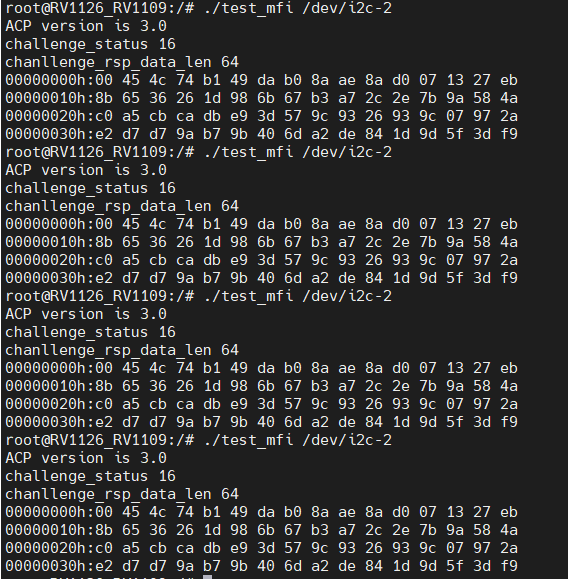

Timequest中Data Path分析

-

Data Arrival Path

-

clock path:时钟信号到达源寄存器时钟端口的时间

-

data path:数据从源寄存器Q端口出发到达目标寄存器D端口的时间

-

-

Data Reqvire Path

- clock path:时钟信号到达目标寄存器时钟端口的时间(加上了一个时钟周期时间)

data path名称解释

名称 | 解释 |

Total | 总时间 |

Incr | 时间增量 |

Type IC | 内部连线延时 |

Type Cell | LUT和DFF延时 |

Type uTco | D触发器输出延迟 |

Type uTsu | 建立时间 |

时序路径中有负的值是合理的,PLL调整相位后的值就可能是负的

Timequest时序优化

提高时钟运行频率,时序优化方法:

-

加约束、插入寄存器(插入寄存器将多个组合逻辑拆分,会引入1个时钟周期的延迟)、改为流水线结构

-

优化代码主要是优化关键路径(timequest中点击)

-

见assign改reg是错误的优化方法

基于chip planner进行时序路径分析

-

arrival clock:时钟信号到达源寄存器时钟端口的路径

-

arrival data:数据从源寄存器Q端口出发到达目标寄存器D端口的路径

-

required clock:时钟信号到达目标寄存器时钟端口的路径

located objects中字符含义

字符 | 含义 |

clk~input | ioibuf |

clkctrl | 全局时钟资源,高速的时钟线 |

-> | 从什么到什么 |

资源放大后,左侧红框为LUT,右侧红框为D触发器