一、啥是自主可控

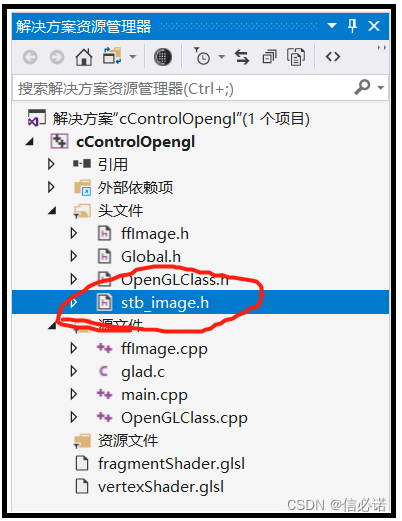

国产CPU现在厂家细算起来其实有很多,现在华为、小米也在做自己的CPU,瑞芯微、全志等的SoC现在也是广泛应用。但是真正能叫做自主可控的CPU厂商,只有6家。那啥是自主可控?首先来不严谨的讲下现在数字芯片是怎么做的设计。FPGA大家都知道,可以通过Verilog或者VHDL等硬件编程语言实现硬件功能。比如,我要实现一个SPI控制8个LED灯的功能,可能从市面上找这种功能的芯片是没有的,那么我就可以自己指定控制LED的指令,通过使用FPGA自己编成,解析SPI传下来的指令,控制LED的亮灭。如果测试验证没有问题,那么就可以把FPGA的RTL拿出来,经过处理拿去流片,流片完成给芯片起个名字,比如YKS2D8001,这就成为了市面上能够实现SPI接口控制8个LED的ASIC芯片了。同时,咱们FPGA的实现代码,也可以拿出来当成一个IP,以后谁要想使用FPGA来实现这个功能的时候,就可以拿来用而不用再单独购买咱们流片完成的ASIC芯片YKS2D8001。

那么,咱们在做复杂功能FPGA的时候,比如xilinx的,咱们会调用xilinx提供的现成的IP,比如它的DDR控制器IP、PCIe IP或者更简单些的串口IP、IIC IP。这些IP咱们在程序实现时,是可以直接调用,根据xilinx提供的操作手册把这个IP给用起来的,但是这个IP核的实现代码,咱们是看不到的,如果咱们想改IP核内的代码,那肯定是没办法的。这就是非自主可控。自主可控,就是能够掌握IP的所有代码,自己想改就改。

飞腾就是国内自主可控6家之一。也就是可以简单的理解为飞腾芯片内的每行代码,每一个功能实现,都是自己实现的。这里有人会说,飞腾不是arm64的么,那是arm的呀。是的,飞腾是arm64的,但是飞腾是购买的arm的指令集授权。指令集授权大家可以通俗的认为就是购买了函数名,但是函数实现是自己做的。所以即使是arm64,也是自主可控的。

二、基于飞腾芯片的设计

2.1 最小系统硬件设计

要想让飞腾CPU加电后跑起来,硬件设计上有几个部分是必须有的。时钟、供电、内存、调试串口、QSPI Flash接口、存储。下面就针对每个部分详细说一下。

2.1.1 时钟

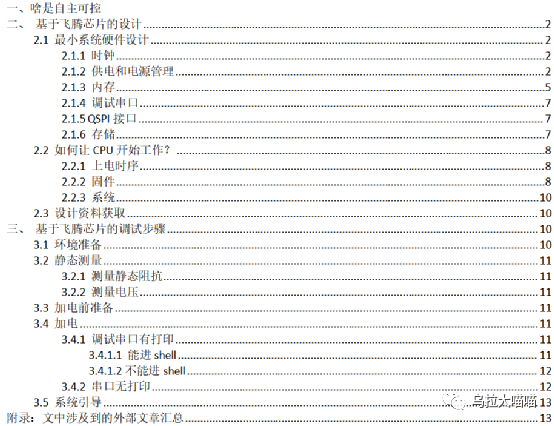

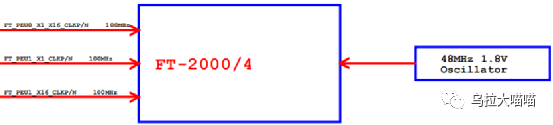

时钟不用多说,所有的芯片都需要时钟。飞腾芯片需求的时钟主要就是两种,1是芯片的主时钟48MHz,2就是芯片的PCIe控制器PEU的时钟100MHz。这个100MHz时钟要求PEU和外设同源,也就是从同一个时钟发生器产生,HSCL电平标准,AC耦合。并且设计时,即使PEU不用,PCIe时钟也是要接的。

图 CPU总的时钟框图

![]()

图 PEU0的时钟

图 PEU1的时钟

2.1.2 供电和电源管理

飞腾的电源种类并不多,需要0.8V(核电)、1.2V(VDDQ)、1.8V(IO)三种。其他电源域基本都可以直连或者通过磁珠连接到这三个电源中,这里就参考demo设计就可以了。

这里需要提示的是:

1.就近放置在芯片电源管脚下的电容为4.7uF,这里尽量不要修改。

2.CPU有一个3.3V的电源管脚,这里给供一个3.3V过来即可。

3.各个电的最大电流一定要查手册,设计电源时一定要保证满足。

4.各个电的纹波不能超5%。注意,这里说的是整个运行状态下,就是BIOS阶段、OS系统启动和运行阶段,是都不能超的。这里特别强调,非常重要!

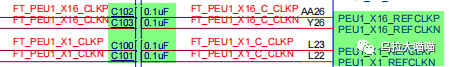

说到电源,就不得不说电源管理。借鉴x86的电源管理状态,飞腾CPU也有电源管理的几个状态。

图 飞腾CPU电源状态

S0就是正常工作的状态,S3就是类似window的睡眠,即待机状态压到内存中,所以要求内存一直带电。S4/S5就是类似window的休眠和关机,即待机状态压到硬盘,或者就是直接关机了,这个时候整板都会掉电。

那么有人问了,S4/S5是俩状态呀?一个是休眠系统状态压到硬盘,一个是关机,这俩放一起咋区分呢?其实不用区分,系统状态压到硬盘了,就已经是被固定保存了,即使掉电也不会有数据丢失,这里应该没错吧。所以对于电源管理来说,S4/S5状态时都是要掉电的。那么S4、S5的区别,主要在下一次开机时。如果去看系统下去执行休眠和关机时的log信息,可以看出,休眠和关机系统处理是不同的,他们会置不同的标志。那么在下次开机的时候,这个置的标志,就能够告知系统要从哪种状态启动。

到这里,供电和电源管理的几个状态应该就说清了,那么现在实际问题来了,供电我能明白,就是使用电源芯片供电嘛。那么这个电源管理,我咋做?

那么下面,我们就一个一个的来说。

首先,我们一个板子肯定是从未加电状态转为加电状态,让CPU跑起来。那么对应上面的状态,那就是S4/S5状态到S0状态,也就是断电关机状态到上电工作状态。这个状态的控制,其实就是对CPU各个电源域上电时序的控制。所以,做硬件不用想太多,从未加电到加电让CPU跑起来,换句话说就是从S4/S5状态到S0状态的实现,就是你想办法把你给CPU的各个电按下面时序跑完就好了。在保证电路设计的情况下哈,只要你按时序跑完,CPU肯定就启动了,也就到了S0阶段。

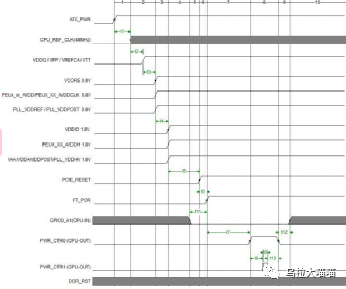

图 S4/S5到S0开机时序图

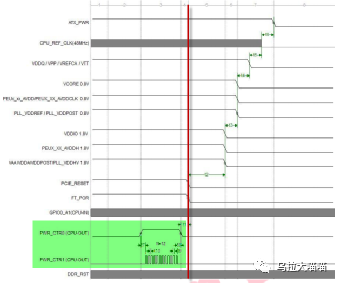

那么,你能猜到了吧,S0到S4/S5是咋弄,其实也一样,也是跑电时序。但是……硬件工程师又问了,板子系统正好好的跑着呢,我咋知道要去跑掉电时序呢?这个问题问的很好。去执行掉电时序,总是要收到信号的,那么这个信号在时序图中是能够看出来的,就是图中标绿的部分。PWR_CTR0、PWR_CTR1这两个是CPU芯片上的两个管脚,当我们在OS系统下点了休眠或者关机命令时,系统肯定是要先去保存自己的状态到硬盘,当保存完了,OS会通过PWR_CTR0、PWR_CTR1这两个管脚,发送脉冲出来(应该是4脉冲代表重启,8脉冲代表转S3状态,12脉冲代表转S4/S5状态),告诉外边可以去跑掉电时序了。外边收到这个脉冲后,自己根据掉电时序去跑就可以了。

图 S0到S4/S5关机时序图