萌新的FPGA学习之实战流水灯

实验任务

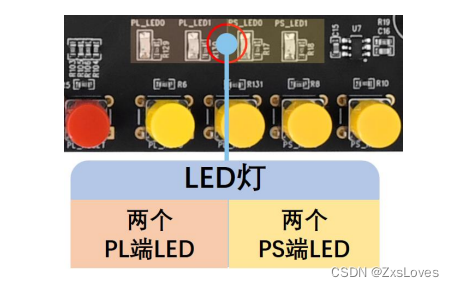

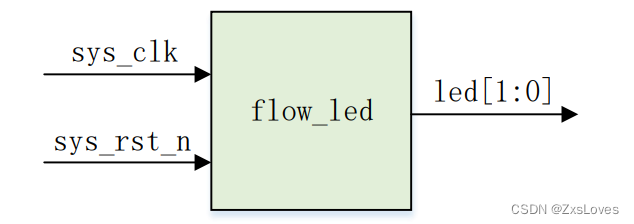

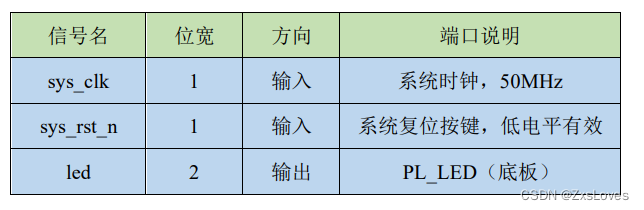

本节的实验任务是使用领航者底板上的两个 PL LED 灯顺序点亮并熄灭,循环往复产生流水灯的效

果,流水间隔时间为 0.5s。

1MHz=1000000Hz =10的6次方

1ns=10的-9次方秒

开发板晶振50Mhz 计算得到1/50M = 20ns

那么我们如果设定0.5s变换一下 那就需要 0.5/20=25000000个时钟周期 计数器滴答滴答随着时钟周期跳变 那么计数从0开始到25000000-1个时钟周期就是正好0.5s

最需要注意的是代码的问题

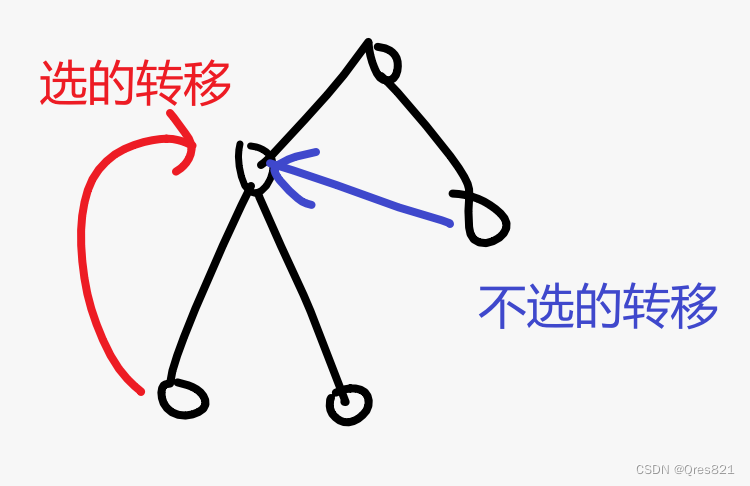

因为是流水灯我们需要在意的是把位置如何移动

因为左移右移难道不是补上0嘛

所以我们采取这个操作

led <= {led[0],led[1]};

你看{led[1],led[0]}=led={led[0],led[1]} ;

这不就是交换嘛

作为试验性质的实验 我们更多的是在实验中学会运行的方法和逻辑

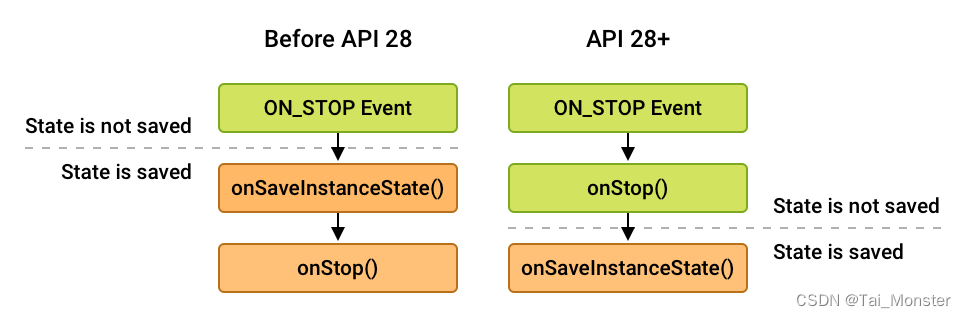

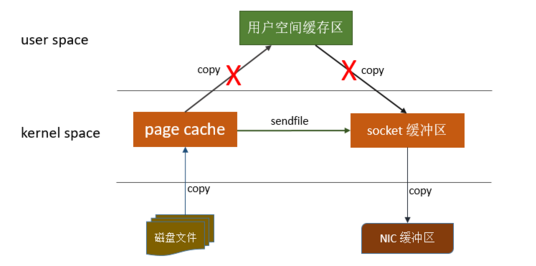

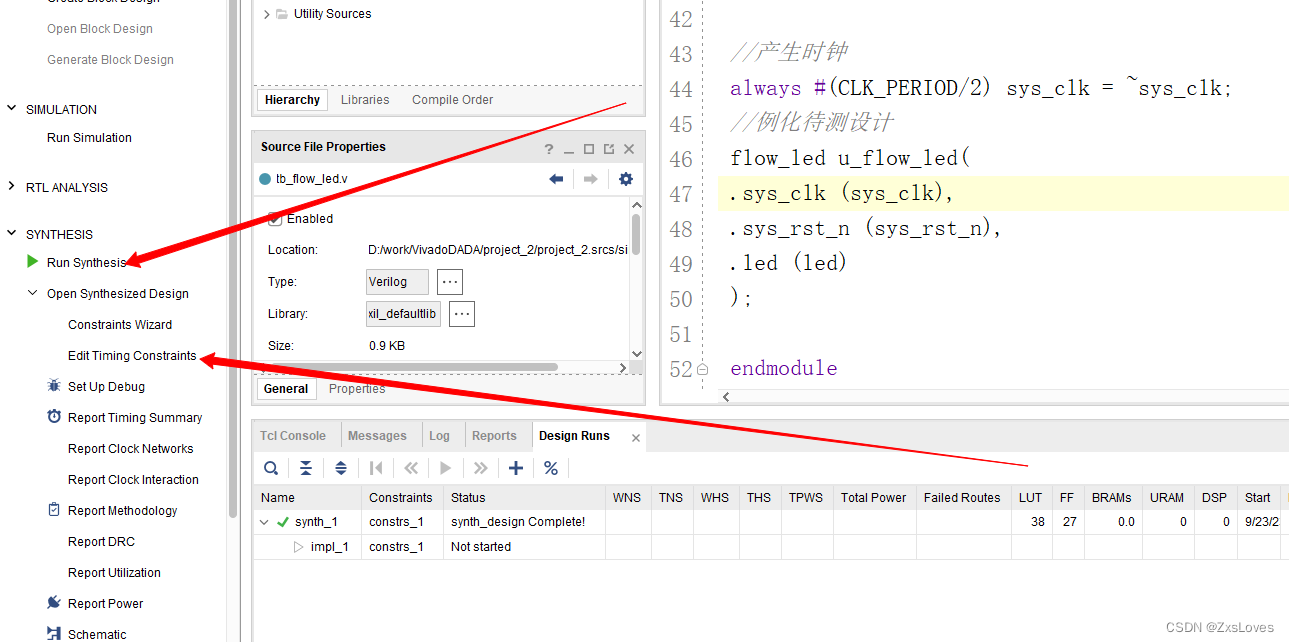

我们采取的对时间的约束是:告诉EDA工具我们进行设计所使用的时钟频率究竟是多少

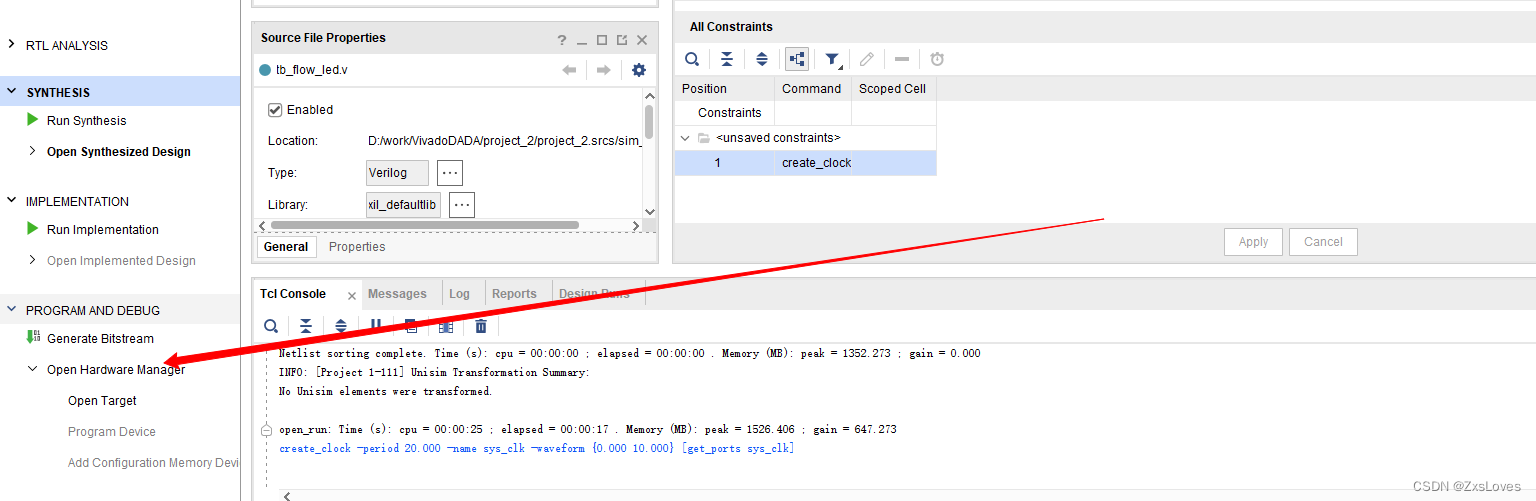

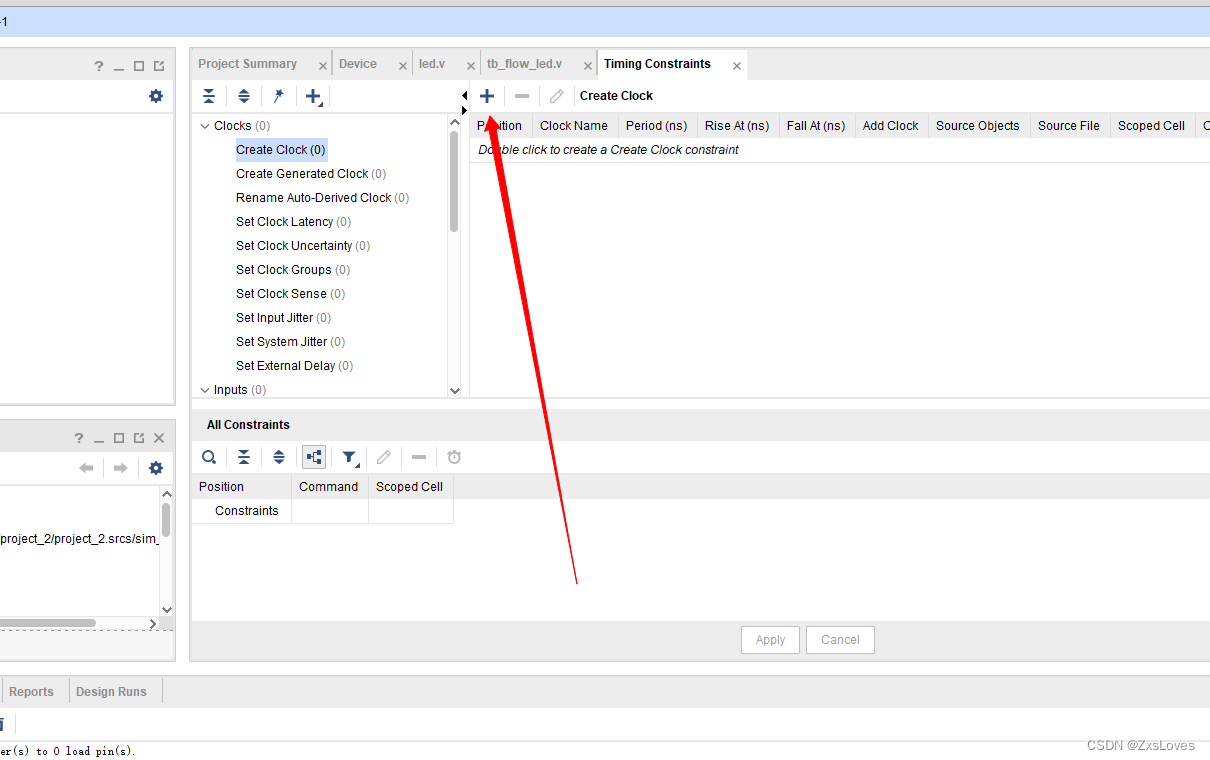

我们现在可以得到如下开始i进行时钟约束的框图

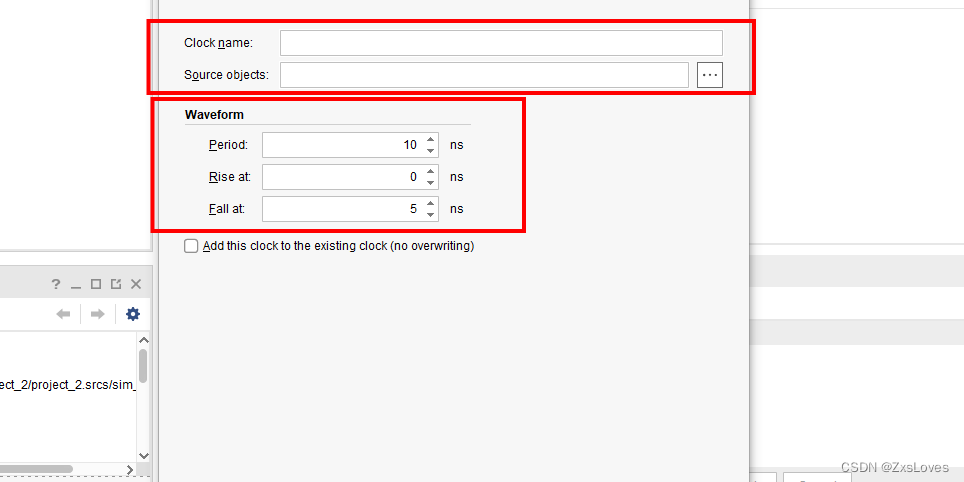

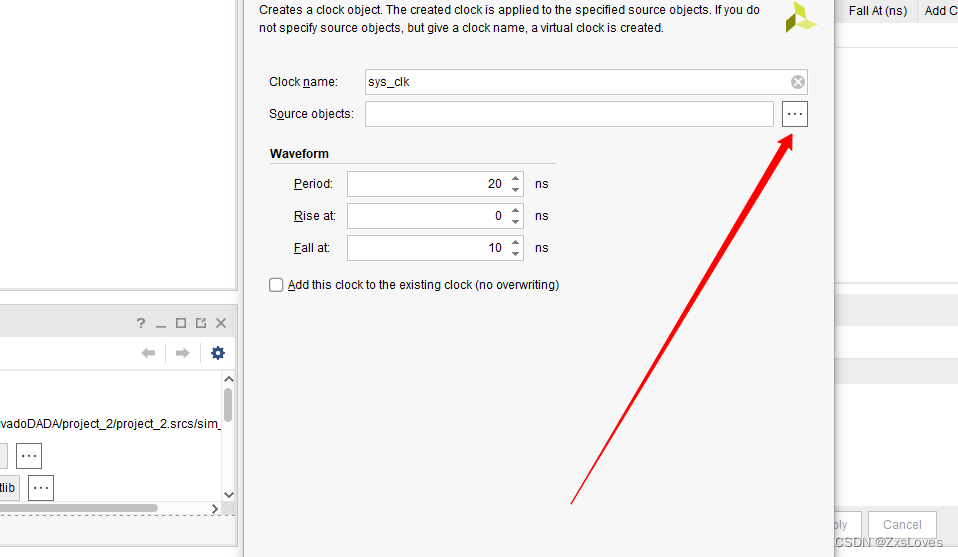

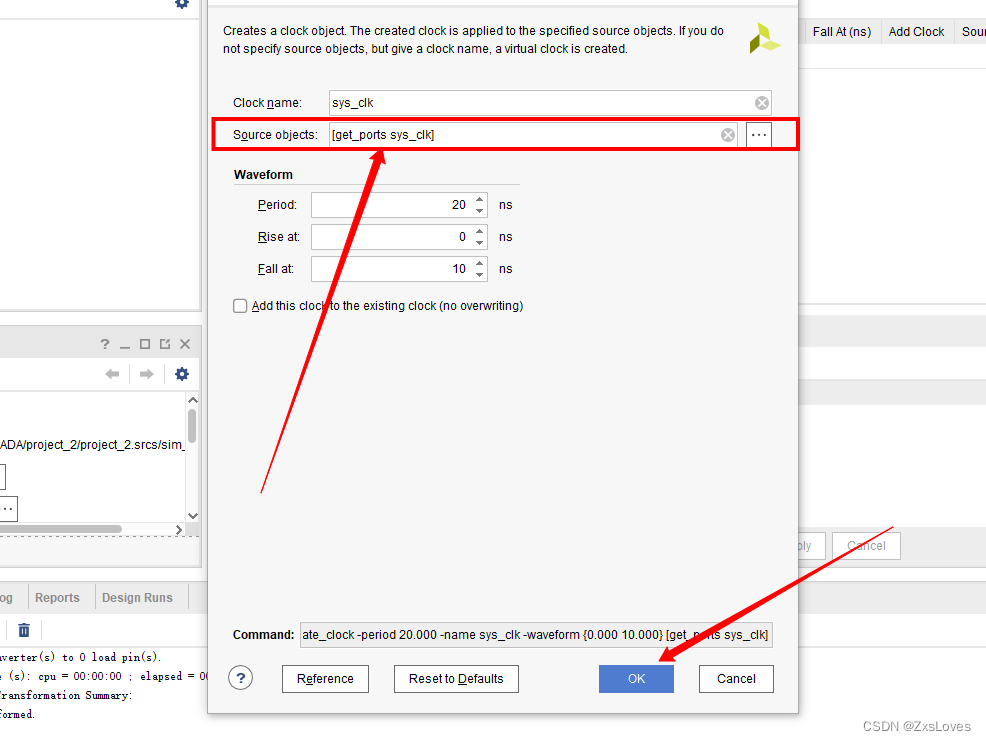

1、Clock name:时钟名称,用于为所创建的时钟约束命名。为了可以一眼看出该时钟约束的约束源,

通常情况下其命名与被约束的时钟信号名相同,因为我们要对系统时钟(sys_clk)进行约束,所以这里我们

将其命名为 sys_clk。

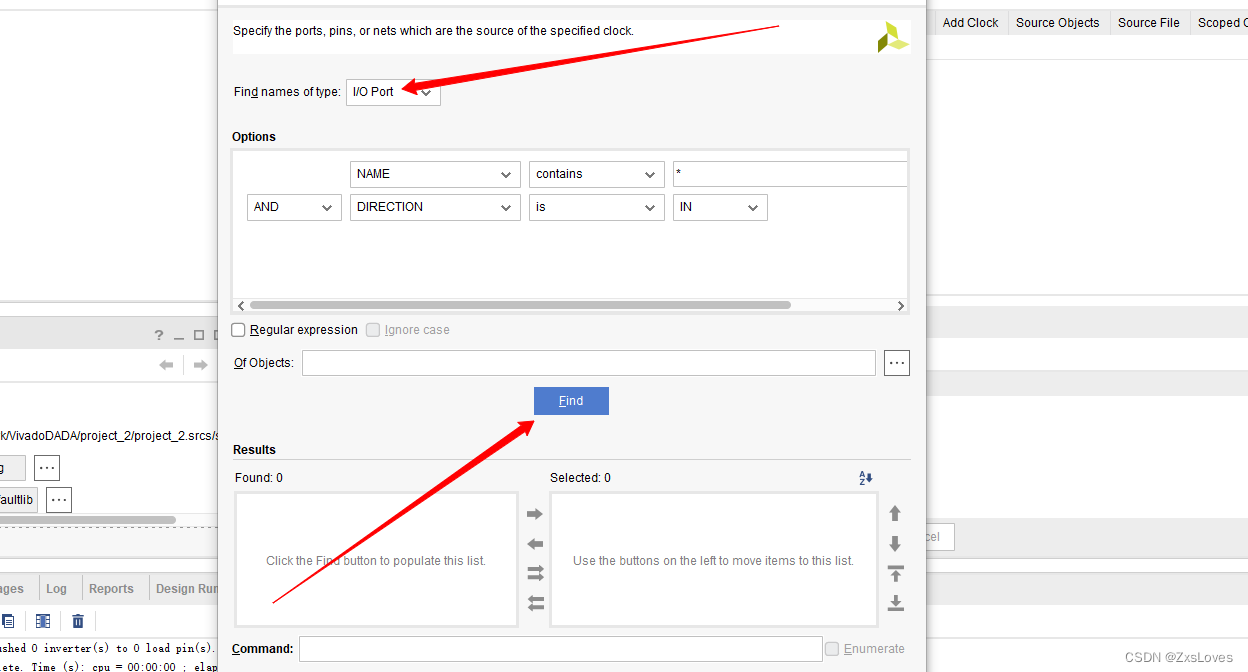

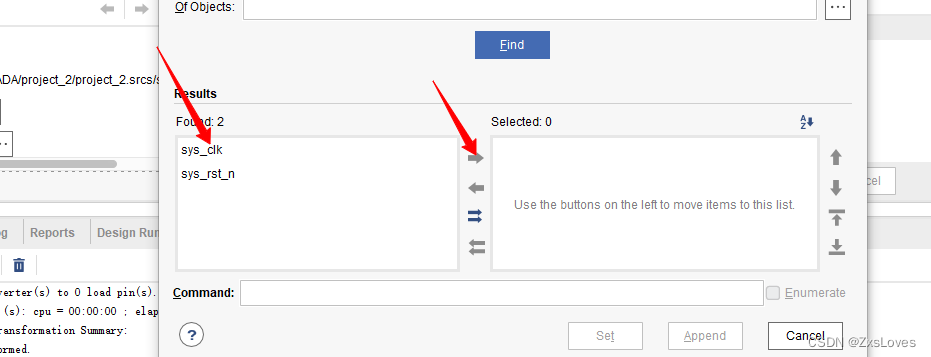

2、Source objects:源对象,用于指定被约束的时钟对象,具体操作我们稍后进行讲解。

3、Waveform:波形,用于设置时钟的周期(Period),上升沿(Rise at)、下降沿(Fall at)以及勾选

Add this clock to the existing clock(是否将该时钟添加到现有时钟中)。因为我们的系统时钟为 50MHz(即

一个时钟周期为 20ns),占空比为 50%,所以 Period 设置为 20,Rise at 设置为 0,Fall at 设置为 10。因为

Add this clock to the existing clock 选项是在同一个约束源时钟存在多个时钟频率且每个时钟频率都需要进行

约束的情况下才需要勾选的,而我们的系统时钟只有一个频率,所以无需勾选。

4、Command:命令,即通过我们上述的配置后,vivado 自动生成的约束命令,该命令是可以直接复制

粘贴到 XDC 文件中使用的。

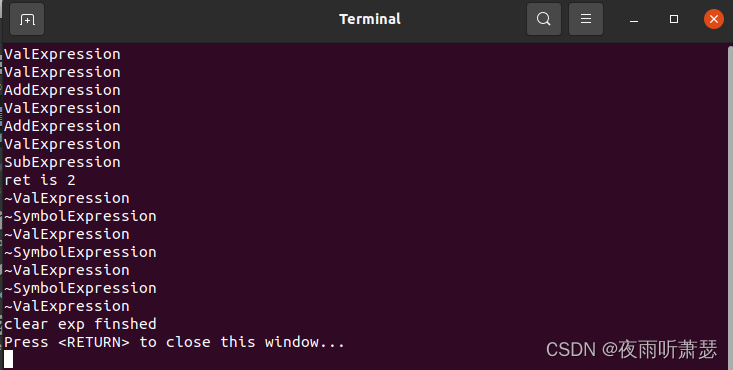

上版验证点击处