0.CSI早期只有DPHY可用

CSI-2 v1.3及之后版本提供了更高的接口带宽和更好的通道布局灵活性。从CSI-2 V1.3开始引入了C-PHY 1.0(C-PHY 1.0是MIPI联盟于2014年9月发布的新物理接口),能够兼容之前的D-PHY v1.2版本。

在CSI-2 V1.2及以前都只能用DPHY传输csi数据。

1.CPHY不需要line coding

8b/10b这些线路编码是不需要的,CPHY的三线编码本身就解决了连续0/1的情况。

2.CPHY的三线编码使用线态跳变传递信息的

有六个线态(wire state),每一个当前线态都可以跳变到另外5个线态。每一次跳变对应3bit symbol【跳变有5种可能,用3bit表示,所以3bit数有不用的】,每7个symbol对应16bit原始数据。可以理解为7个symbol需要3线共传输21bit,共传输16bit原始数据。16/21=76%.比DPHY的50%效率要高【两个差分bit传1bit原始数据】。

线态之间有5种变化,所以最多能传输log2(5)=2.3219bit数据,连续7个跳变最多能传输log2(5)×7=16.2533bit数据,所以选择用7个symbol表示16bit数据

3.CPHY也正是通过线态的电压改变完成了时钟恢复

无论何时,线上传输的相邻线态【wire state】都是不同的,而正是线态的变化对应为编码数据,同时由不停的变化可以方便的恢复时钟

当前线态由当前symbol和上一个线态共同决定。

4.CPHY基本上完全重用DPHY的低功耗模式

异步escape传输和LP mode和DPHY一样,Escape和control mode信号和DPHY PPI一致,除了没有clklane的ulps相关信号

5.无需clklane,所以正反向传输可以达到相同的速率,DPHY反向速率是正向最大1/4

6.HS mode两边都端接,LP是单端且无端接

7.LP或ESC是三线是什么状态

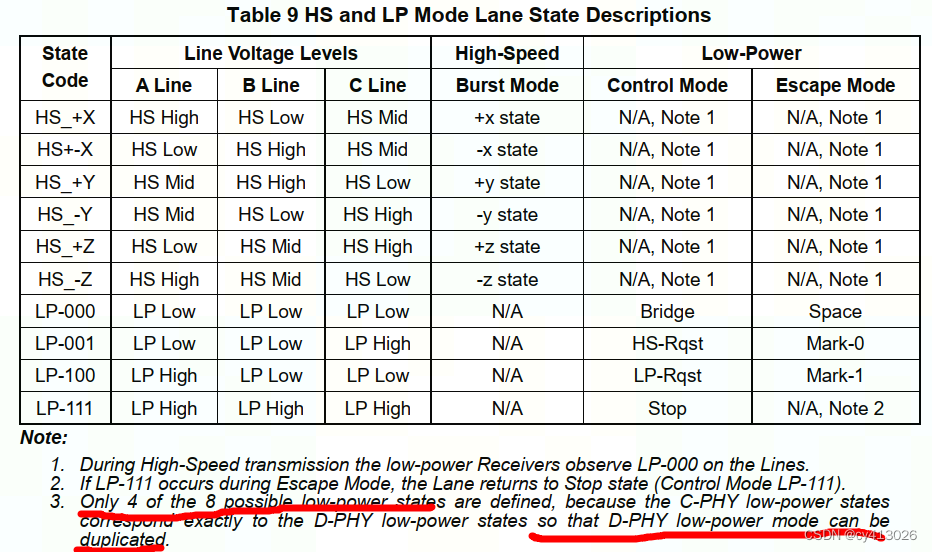

虽然有三根线,但是为了保证和DPHY一致,只有4个状态是有效的。除了LP-111外,Line-B都是0.

8.和DPHY相同的HS/LP/LPCD

9.PPI接口大部分和DPHY的PPI复用,会有一些特殊

- cphy ppi的DataHs可以支持16bit也可以支持32bit,对应wordClkHs【DPHY是ByteClkHs】symbolClkHs的1/7和1/14.

- CPHY比DPHY多了2bit的T/RxWordValidHS[1:0],0bit表示DataHs[15:0]有效,1bit表示DataHS[31:16]有效。

- CPHY可以选择只支持16bit Data或32bitdata,也可以同时支持16/32bit可配----TxDataWidthHs

- 多了发送同步及同步类型选择TxSendSyncHs[1:0], TxSyncTypeHS0[2:0]和TxSyncTypeHS1[2:0]-------Rx增加对应的信号

- Rx多了一个RxInvalidCodeHS[1:0]:用来表示收到的连续7个symbol不是有效symbol。在syncWord和ALP时无效

- 多了ALP code发送和ALP类型选择以及ALP Nibble data三组信号TxSendALPHS[1:0], TxALPCodeHS0/1[3:0]和TxALPNibble0/1[3:0]------Rx增加对应的信号

- SyncWord和ALP是32bit还是16bit和DataHS的规格一致

- Escape信号和DPHY一致

- control mode比DPHY少了clklane的ulps信号,多了一个ALPWakeState[2:0]:ALP-暂停唤醒线态,配置ALP-暂停唤醒状态时线态值。默认为+x。

10.HS的同步及同步类型

如果是32bit的dataHS,为什么会有TxSendSyncHs[1:0]两bit ?

原因在于16bit的syncword有可能在dataHS的低16bit,也有可能在高16bit。对应需要两个TxSyncTypeHS0/1[2:0]

syncWord都是16bit,会不会出现连续发送的情况?这时候2bit的SendSyncHs都会有效?

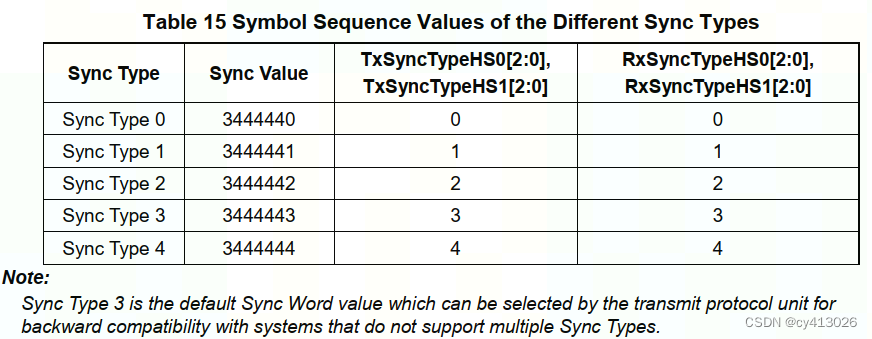

TxSyncTypeHS 如下图有5种类型的syncword。

在一次burst传输中第一个syncWord必须是"3444443",后续的syncWord可以任意配置上表中的5个值。所以一次Burst传输中可以发送不同类型的syncWord。

TxSendSyncHS[1:0]:两种情况下发送syncWord:

- 用发送的syncWord来分开packet header的副本

- 在HS data发送之前即SOT阶段发送syncWord

对应Rx也有两种情况:

- 在RxActiveHS上升沿拉高一个RxWordClkHS

- 在收到冗余packet headers之前拉高

11.ALP和FBTA,CPHY 1.2/DPHY 3.0特性

CPHY v1.2有ALP,但DPHY v1.2是没有的。在CPHY v2.0还增加了在HS mode下快速进行bus trun-around的流程,FBTA。 DPHY V3.0上开始支持ALP和FBA。

11.1 ALP

11.1.1 什么是ALP? 和LP有何区别?为什么要增加ALP? 答案如下:

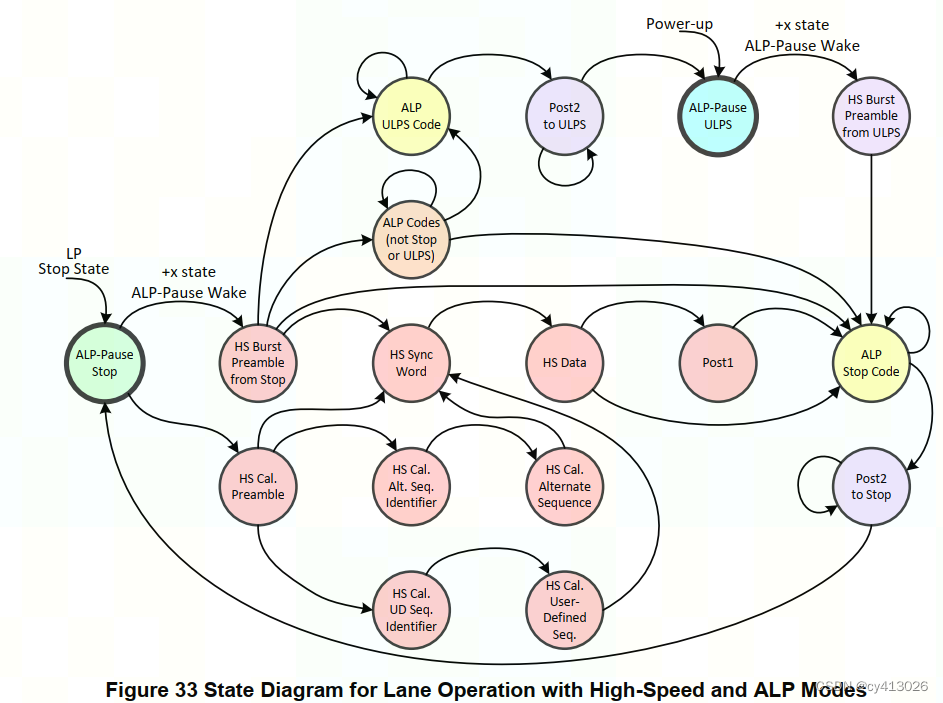

ALP:alternative low power 【备用低功耗】.ALP是HSmode下的一种低功耗,可以使Lane和PHY不用进入LP mode,而降低功耗。这么做的好处是能够快速的进行ALP和HS data bursts传输的切换。

正常情况下HS的data burst传输之间是要回到LP111 stop state这种standby状态。一个Burst传输完成要走EOT,拉起LP-111 stop state的,然后进入control mode。而ALP mode就不要走EOT,也不用拉高LP-111,而是另外一个流程快速进入ALP-PAUSE状态。

ALP-PAUSE又分为ALP-PAUSE STOP和ALP-PAUSE ULPS,这两个状态和LP mode 的stop state和ulps是类似的。

ALP-PAUSE时,线态为VA=VB=VC 且

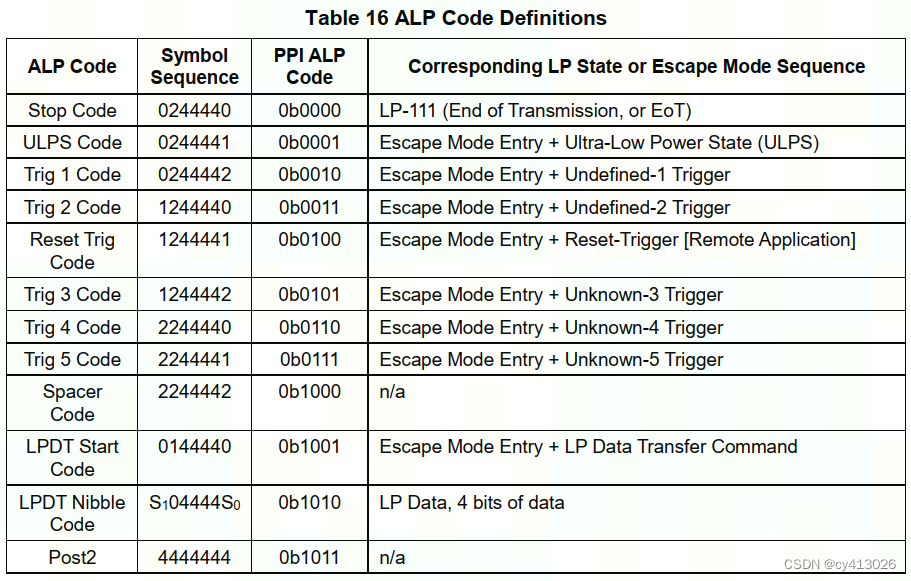

11.1.2 ALP code

上表给出了PPI ALP code及对应的seven-Symbol序列【需要注意的是和HS data不同,这里不是16mapping到seven-Symbol,而是4bit mapping】。同时给出了和LP及Escape mode相应的序列

11.1.3 在HS传输ALP的示例及状态转换

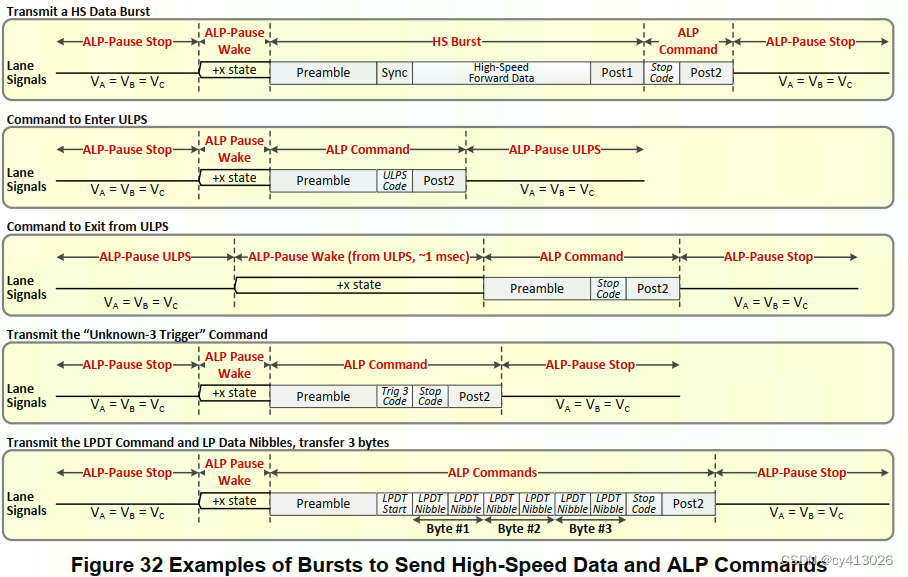

一次完整的HS到ALP在到HS的过程如下:

- HS data传输----->Post1------>ALP command---->Post2----- >ALP-Pause mode----->ALP-Pause Wake----->Preamble------>sync------>HS data

- 这个过程可以类比 HS data传输---->LP command---->Escape---->LP command ----->HS data传输的过程

一次完整的ALP到ALP command再到ALP的过程如下:

- ALP-Pause Wake----->Preamble------>ALP command---->Post2----- >ALP-Pause mode----->ALP-Pause Wake

- 这个过程可类比Escape----->LP command----->Escape----->LP command

从上面过程来看有几个结论:

- ALP-Pause Wake之后都紧跟着Preamble

- 进入ALP-Pause之前都要发送Post2

- 从ALP-Pause退出 先进入Wake状态,在该状态停留一段时间【上图Wake的线态是+x,实际可以配置为6个线态的任意一个】

- 从ALP-pause到HS data传输要重新sync

- HS data到ALP command中间要有Post1【下图也有HS直接进入ALP command的,此时因该是HS data没有发送完毕】

11.1.4 ALP相关的TX和RX端信号:

TxSendALPHS[1:0] :在HS mode,该信号拉起时,开始传输ALP code。此时会忽略DataHs上的数据,而选择TxALPCodeHS0/1[3:0]上的4bit的ALP code。

TxALPCodeHS0/1[3:0]:4bit ALP code。【ALPCode不为4'b1010时,直接发送ALPCode的seven-symbol;ALPCode=4'b1010时,发送的是由TxALPNibble0/1[3:0]确定的】

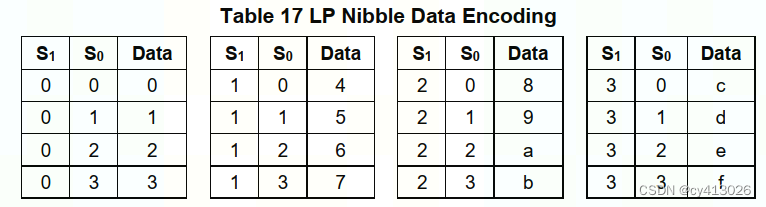

TxALPNibble0/1[3:0]:在HS发送,TxSendALPHS有效且TxALPCodeHS0/1[3:0]=4'b1010的时候用来选择Nibble code的seven-symbol的第1和第7个symbol【即11.1.2节 ALP code中 LPDT Nibble code的s0和s1】。其中S0和S1的编码如下【TxALPNibble0/1[3:0]就是下表的Data列,取值0-0xF】:

之所以有0/1的选择是为了和dataHS是一拍16bit还是一拍32bit保持一致。比如说当前是32bit的dataHS,当前的TxWordValidHS[1:0]=2'b01, TxSendALPHS[1:0]=2'b10,则此时:

- DataHS[15:0]需要被TX正确发送

- DataHs[31:16]不会被发送,而是选择TxALPCodeHS1[3:0]或LPDT Nibbie code来发送。

对应的Rx端信号为:

RxALPValidHS[1:0]:表示Rx收到了7-symbol的ALP code。一般在以下三种情况下拉高:

- 在normal HS preamble后面【由11.1.3节ALP的示例图可见,preamble后面不一定全是ALP command】

- 在Hs burst的POST1之后【由11.1.3节ALP的示例图可见】

- 在calibration preamble后面【11.1.3节ALP的示例并没有列出这种情况】

11.1.5 什么时候发起ALP?

TODO,这个应该在protocol里面描述?

11.2 FBTA

TODO,没有细看,需要在CPHY的v2.0版本查看。

12.和DPHY一样PPI TX的data支持反压,PPI RX不支持反压

13.Reserved

14.所有lane最低支持前向HS和escape

15.HS传输16bit整数倍数据,LP传输8bit整数倍数据【确切说是LPDT】

16.从16bit到7symbol的mapper和demapper以及symbol到wire state的编解码

都可以在C-PHY specification_v1.2.pdf的第六章global operation上找到,这里不在展开

17.LP也只有4个状态

和DPHY的LP一样都只有4个状态LP-000,LP-001,LP-100,LP-111,DPHY是LP00/01/10/11.如果当期是HS传输,对于LP-RX来说会把250±250/2mv的HS信号都识别为LP-000【DPHY也是类似】。

除了stop state LP-111之外,Line-B都是0,所以Escape的时钟可以XOR line-A and line-C得到

18.Post1/2,sync word, preamble

18.1 Post1

Post1:是packet Data的结尾标识,是长度可配的7-symbol,7-symbol是连续的7个"4".该post1不作为sync使用。另一个用途是为了在packet data传输完毕,继续传递时钟信息一段时间,用于Rx PHY和protocol处理完packet。

18.2 Post2

Post2:进入ALP-Pause前标识码,前面只能是ALP的stop code和ULPS code。是一个到最多64个7-symbol的"4"

用于提供足够多的时钟来让Rx处理Stop code或ULPS code,并让Rx做好进入ALP-Pause stop/ulps的准备

18.3 sync Word

sync Word:用作同步和分割冗余PH。用作同步时跟在Preamble后面。是一个7-symbol为"3-4-4-4-4-4-x"。TX发送时,最后一个symbol是确定的【最先发送】,但RX检测到5个连续的"4-4-4-4-4"后面接着一个"3"时就可以完成同步,而不关心最开始接收的"x"

x可以时0,1,2,3,4这5种取值,对应5种SyncType,可参考第10条"HS的同步及同步类型"的描述

【High-Speed data transmission occurs in bursts. To aid receiver synchronization, data bursts shall be extended on the transmitter side with a Preamble and Post sequence.】

上面一段CPHY spec原文虽然说前导码和Post seq用于sync,实际只有专用sync word用于同步

18.4 Preamble

18.4.1 data burst preamble

Preamble:前导码分别为两种,一种是带中间可编程序列的;另外一种是不带中间可编程序列。如下:

带中间可编程序列持续时间为t3-PREBEGIN+t3-PROGSEQ+t3-PREEND,其中中间可编程序列持续时间为t3-PROGSEQ,序列可配置。PREBEGIN和PREEND期间发的都是7-symbol "3"

不带中间可编程序列续时间为t3-PREBEGIN+t3-PREEND,PREBEGIN和PREEND期间发的都是7-symbol "3"

18.4.2 calibration preamble

TODO

19.bit order 字符顺序

在描述7-symbol和其他序列时都是按照MSB在左边。但LSB先发送,MSB后发送。

7-symbol:[s6s5s4s3s2s1s0],其中s0先被Tx发送,先被Rx接收。

上面的规则是通用规则,CPHY/DPHY都是遵守该规则。

500.CSI实际传输是以packet为单位

虽然CPHY单lane传输的最小单位是16bit,但是实际协议层是以packet为单位传输数据的。在协议层看到的是一次传输一个或多个Packets。对于每条lane 一次HS Transmission【或者说一次Burst传输】是以SOT开始,EOT结束。多条lane数据量可以不相等,也可以不同时开始【通常情况下同时开始,不同时结束】。

CPHY HS传输视频数据时,如果protocol把一个packet分配到多lane同时传输时,每条lane都都会传输一份该packet的header。

DPHY HS传输视频数据时,如果protocol把一个packet分配到多lane同时传输时,不需要每条lane都传输一份PH和PF,只需要将packet按顺序在lane上传输即可。

501.CSI-CPHY下的长包结构

有三点需要注意:

- Header是传输该packet的所有lane都要发送

- 每个header都是由两个3x16bit的相同header组成,这叫做copy of a packet header或者redundant header

- 两个相同的3x16bit的header在发送之间要插入syncWord,用于分割原PH和redundant PH。

对于第一点有个问题: 如果视频payload只有16bit,但是一共有4个lane在传输,此时该payload组成的packet是会分配到单lane还是4lane上传输?

所以需要确定protocl在分配数据的原则是什么

502.什么是redundant Packet headers(Copy of a packet header)

首先需要说明的CSI v1.2及以下都是对应的PHY只有DPHY,没有CPHY。redundant PH只在CPHY的packet中才有。

503.SOT和redundant Packet headers之前都会发syncWord

在SOT流程中会发送SOT

在redundant Packet headers之前也会发送syncWord----这个syncWord由phy的controller插入第一个3x16bit的packet Header和第二个3x16bit的packet header【即redundant packet Header和第一份完全一致】之间。该syncWord仅仅是用来分割两份PH的。

注意无论DSI还是CSI的packet中都没有包含为同步而添加的syncWord。Transmission的同步都有靠SOT的syncWord

504.CPHY protocol多lane传输,分配和合并

TODO