萌新的SOC学习之小水文系列

SD卡读写TXT文本实验

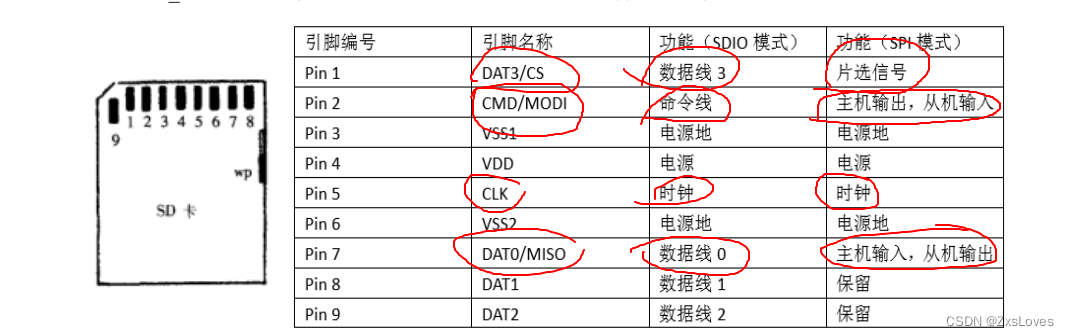

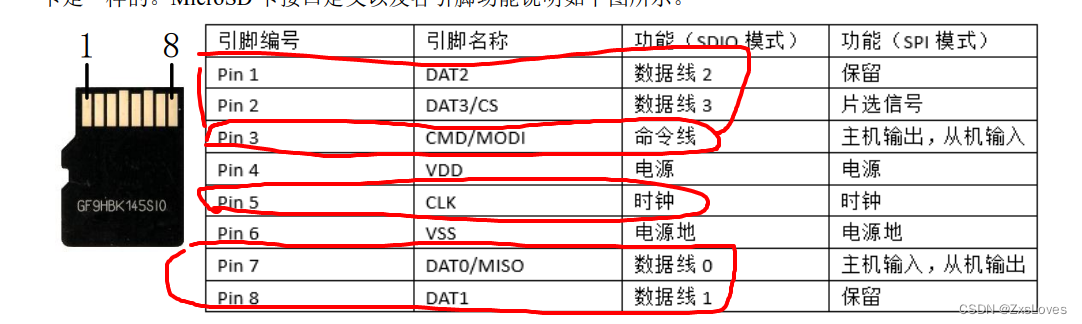

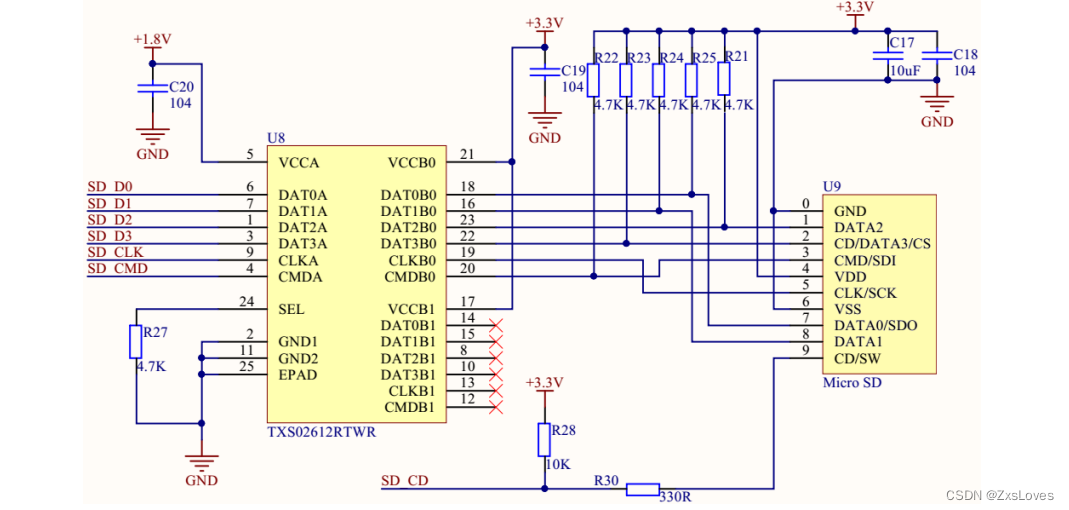

SD 卡共有 9 个引脚线,可工作在 SDIO 模式或者 SPI 模式。在 SDIO 模式下,共用到 CLK、CMD、DAT[3:0]六根信号线;在 SPI 模式下,共用到 CS(SDIO_DAT[3])、CLK(SDIO_CLK)、MISO(SDIO_DAT[0])、MOSI(SDIO_CMD)四根信号线。

SDIO模式下 实现的功能

SPI功能模式下

标准 SD 卡 2.0 版本中,工作时钟频率可以达到 50Mhz,在 SDIO 模式下采用 4 位数据位宽,理论上可以达到 200Mbps(50M x 4bit)的传输速率;在 SPI 模式下采用 1 位数据位宽,理论上可以达到 50Mbps 的传输速率。因此 SD 卡在 SDIO 模式下的传输速率更快,同时其操作时序也更复杂。值得一提的是,ZYNQ内部集成了两个 SD 卡控制器,并且 Xilinx Vitis 的 standalone 已经移植好了 FATFS 文件系统(Vitis 软件中叫做 xilffs),因此在 Vitis 中添加 xilffs 库后,就可以在程序中使用 FATFS 中的 API 函数来操作 SD 卡。

ZYNQ 中的 SD 卡控制器符合 SD2.0 协议规范,接口兼容 eMMC、MMC3.31、SDIO2.0、SD2.0、SPI,支持 SDHC、SDHS 器件。SD 卡控制器支持 SDMA(单操作 DMA)、ADMA1(4K 边界限制 DMA)和ADMA2(在 32 位系统中允许任何位置和任意大小)。

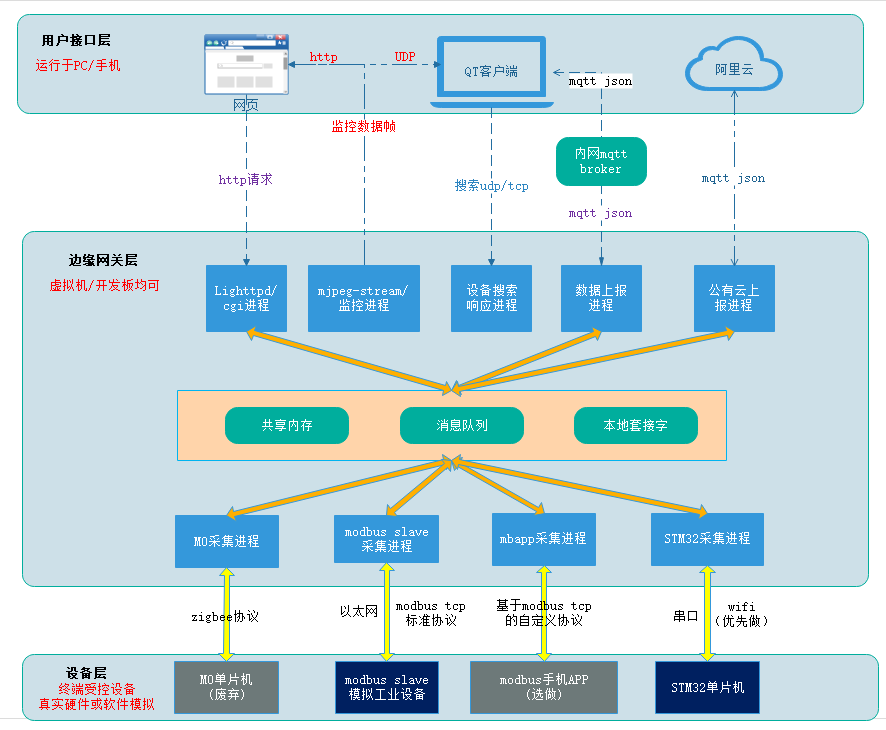

ARM 处理器通过 AHB 总线访问 SD 卡控制器,SD控制器采用读和写通道各自双缓冲 FIFO 的机制提高吞吐带宽。

内部框图

SD 控制器读写通道采用独立的 512 字节深度的双缓冲 FIFO 执行读和写操作。在写操作时,处理器向其中一个 FIFO 写数据,将另一个 FIFO 的数据写到 SD 总线;在读操作时,SD 总线上的数据向其中一个FIFO 写数据,处理器将数据从另一个 FIFO 读出数据。SD 卡控制器通过双缓冲机制以保证最大带宽。

FIFO 先入先出

FATFS 是一个完全开源免费的 FAT 文件系统模块,专门为小型的嵌入式系统而设计。它完全用标准 C语言编写,所以具有良好的硬件平台独立性,可以很方便的移植到各种嵌入式处理器中。Xilinx Vitis 的standalone 已经移植好了 FATFS 文件系统,因此在 Vitis 中添加 xilffs 库后,就可以在程序中使用 FATFS 中的 API 函数来操作 SD 卡。

FATFS 的特点如下:1、 结构清晰,代码量少,文件系统和 IO 底层分开,特别适合新手入门学习;

2、 支持最多 10 个逻辑盘符和两级文件夹;

3、 支持 FAT12/FAT16 和 FAT32 文件系统;

4、 支持长文件名称。

最上面的顶层是应用层 最顶层是应用层,使用者无需理会 FATFS 的内部结构和复杂的 FAT 协议,只需要调用 FATFS 模块提供给用户的一系列应用接口函数,如 f_open,f_read,f_write 和 f_close 等,就可以像在 PC 上读/写文件那样简单。

中间层 FATFS 模块,实现了 FAT 文件读/写协议。FATFS 模块提供的是 ff.c 和 ff.h。除非有必要,使用者一般不用修改,使用时将头文件直接包含进去即可。

FATFS 模块提供的底层接口,它包括存储媒介读/写接口(disk I/O)和供给文件创建修改时间的实时时钟。

实验任务

本章的实验任务是通过 Xilinx Vitis 自带的 FATFS 库,完成对 TF 卡中 TXT 文本读写的功能,并将读写测试结果通过串口打印出来。

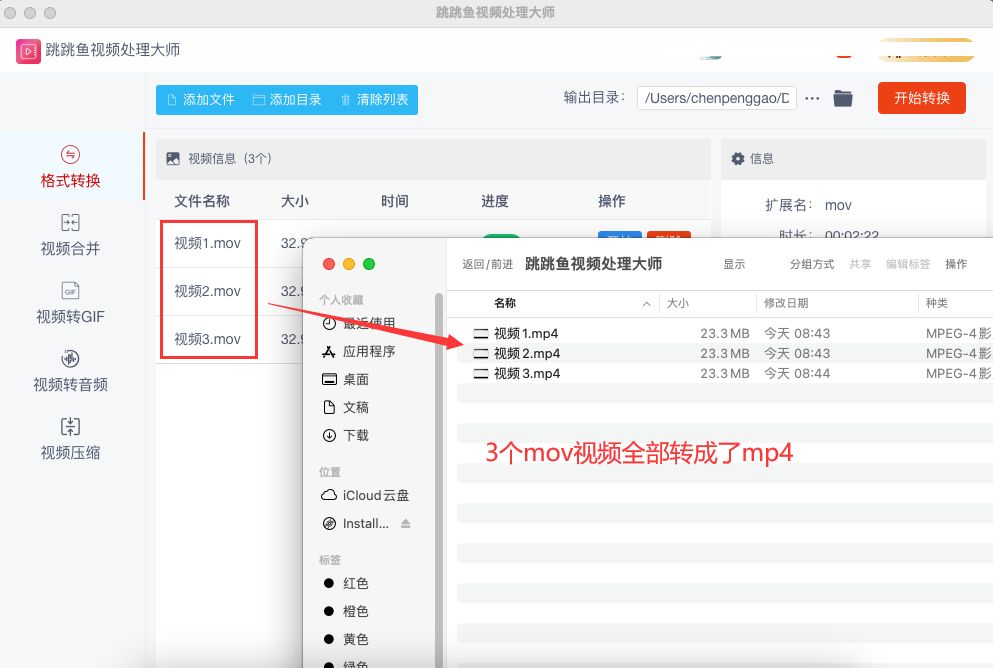

因为本节用的是TF卡的读写

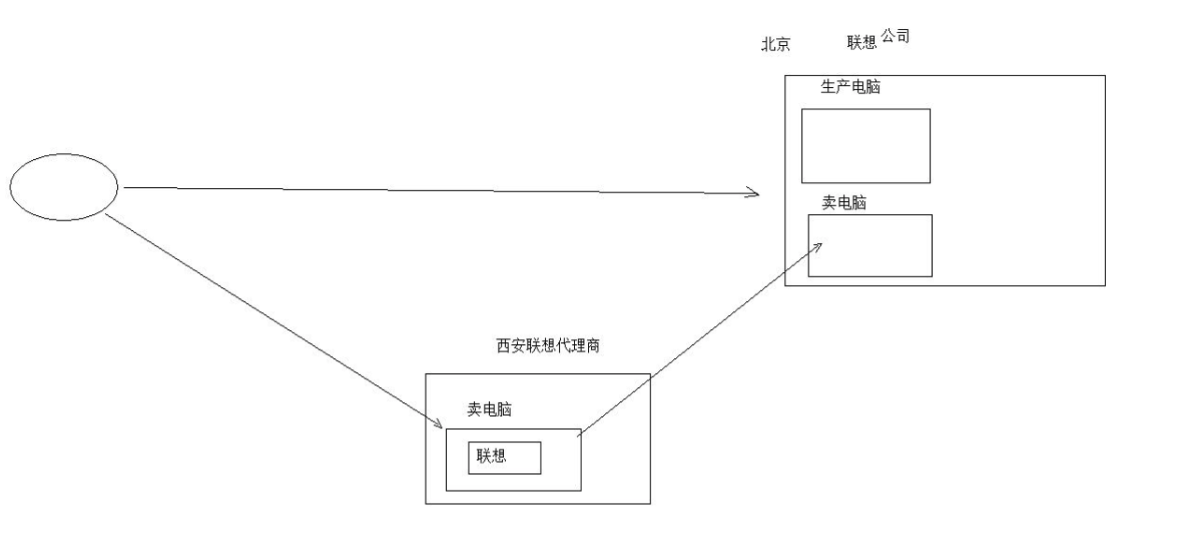

SDIO模式

SPI模式

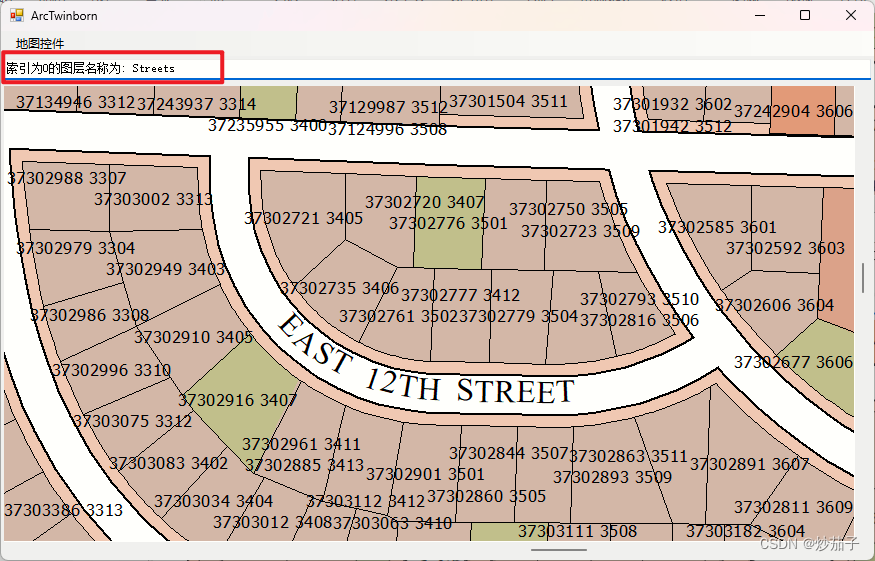

下面是结构框图

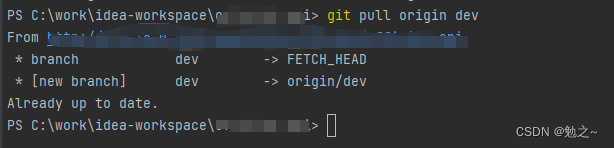

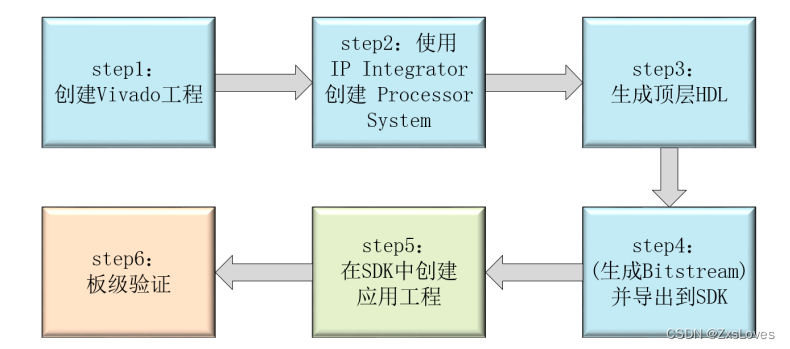

其中 step1 至 step4 为硬件设计部分,在 Vivado 软件中实现;step5 为软件设计部分,在 SDK 软件中实现;step6 为功能的验证。

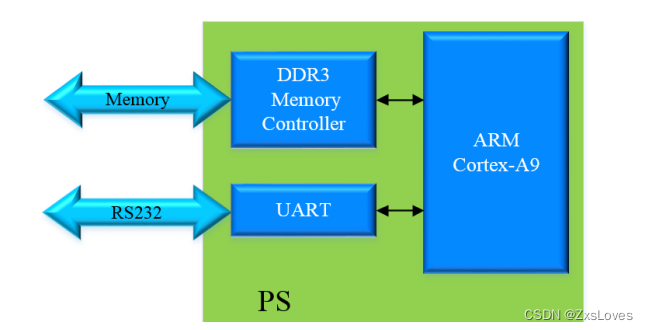

PS 最小系统

以 ARM Cortex-A9 为核心、DDR3 为内存,加上传输信息使用的 UART 串口就构成了 ZYNQ 嵌入式最小系统。可以看到,这个最小系统只包括了 ZYNQ 中的 PS 部分。

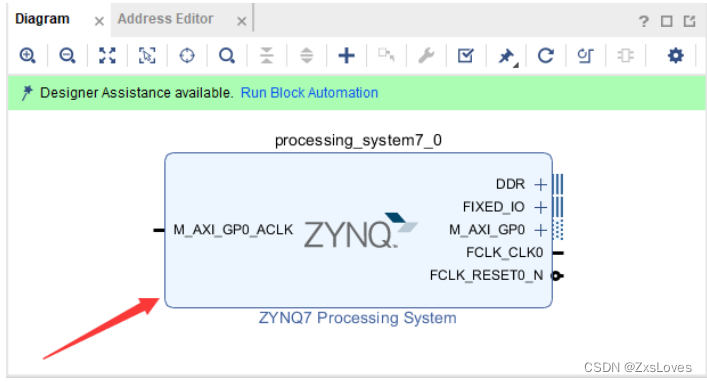

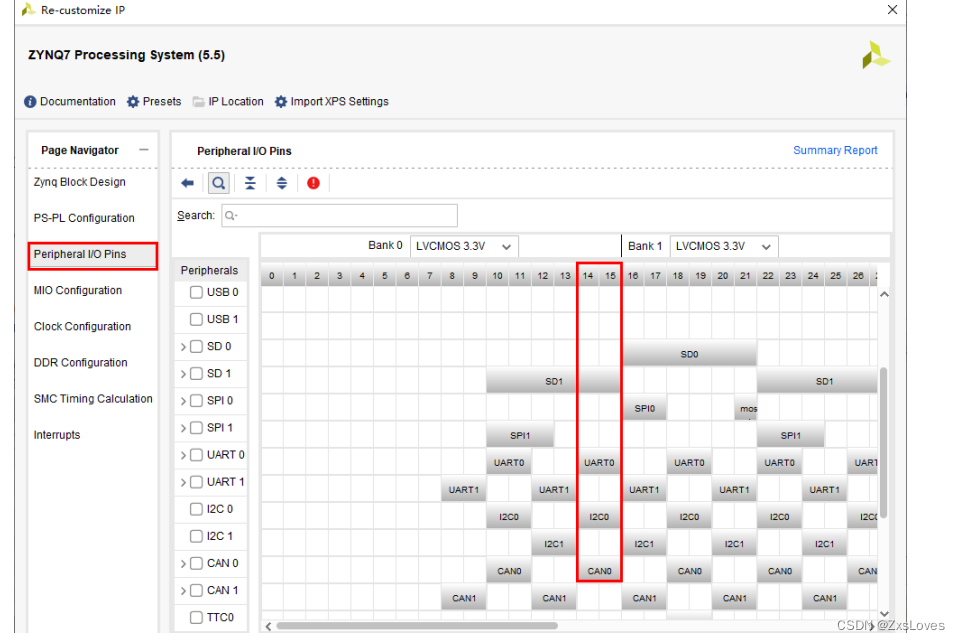

创建IP核之后得到

PS 和外部设备之间的连接主要是通过复用的输入/输出(Multiplexed Input/Output,MIO)来实现的。PS的54个MIO引脚可以用于连接不同的外设接口,如图 1.3.13中的MIO14和MIO15,既可以配置成UART0的引脚接口,也可以配置成 I2C0 或 CAN0 的引脚接口。

![[PyTorch][chapter 57][WGAN-GP 代码实现]](https://img-blog.csdnimg.cn/1a227a6496cf4e3fb077aa12551839c9.png)