数字IC/FPGA面试题目合集解析(一)

- 题目概述

- 题目

- 1,计算题

- 2,计算题

- 3,选择题

- 答案与解析

- 1,计算题

- 2,计算题

- 3,选择题

题目概述

1,计算题:计算该触发器等效的建立保持时间(西安某Fabless面试笔试题)

2,计算题:计算组合逻辑的延时时间范围

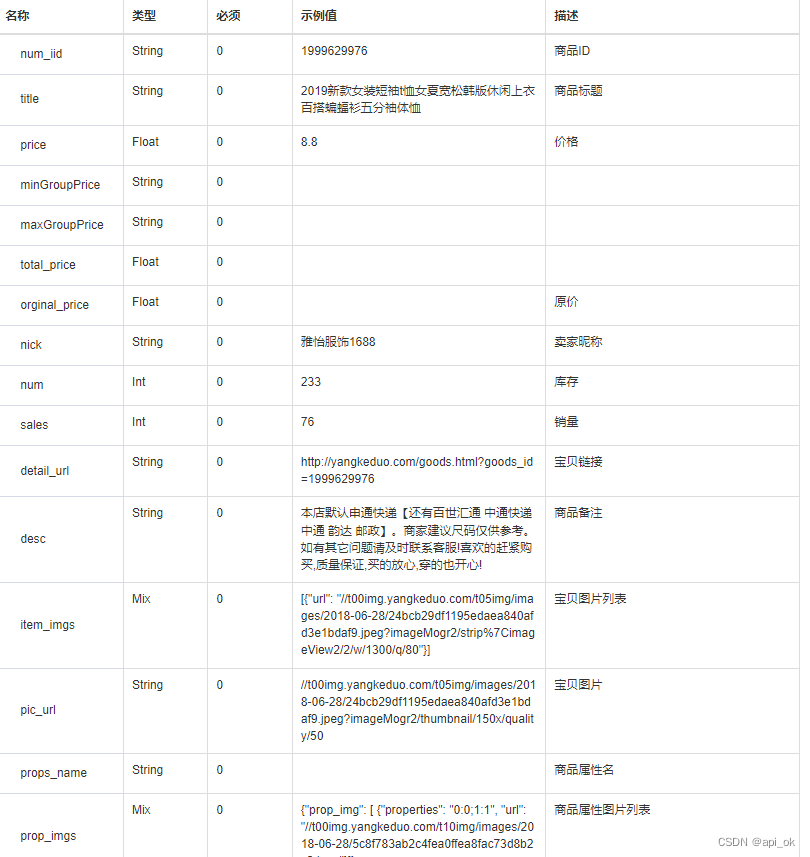

3,选择题:Which of following ways cannot be used to improve timing of a hold violation path

题目

1,计算题

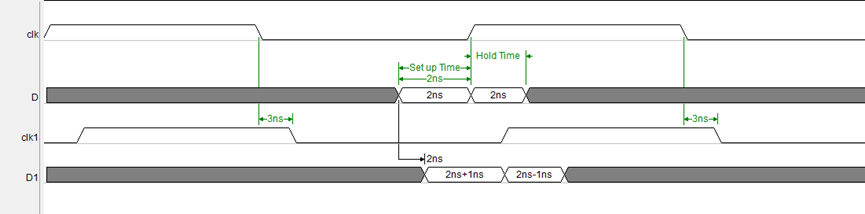

问题:原触发器,即对于D点的建立时间,保持时间均为2ns,先由于存在线延时,对应延时信息如图所示,请问从D1,CLK1看,该触发器的建立时间和保持时间是多少?

2,计算题

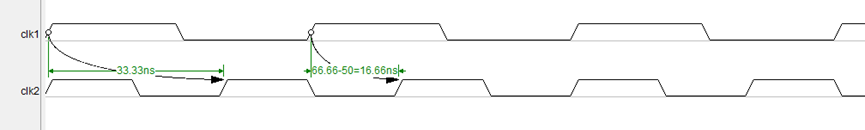

问题:CLK1=20M,CLK2=30M,两个时钟的第一个上升沿在同一时刻,请计算X组合逻辑的延时范围(不考虑器件的建立保持时间)。

3,选择题

Which of following ways cannot be used to improve timing of a hold violation path?

A reduce the net noise

B increase cell drive strength on the data path

C use higher voltage threshold cell on the data path

D reduce the clock skew

答案与解析

1,计算题

答案:Tset_up=3ns,Thold=1ns。

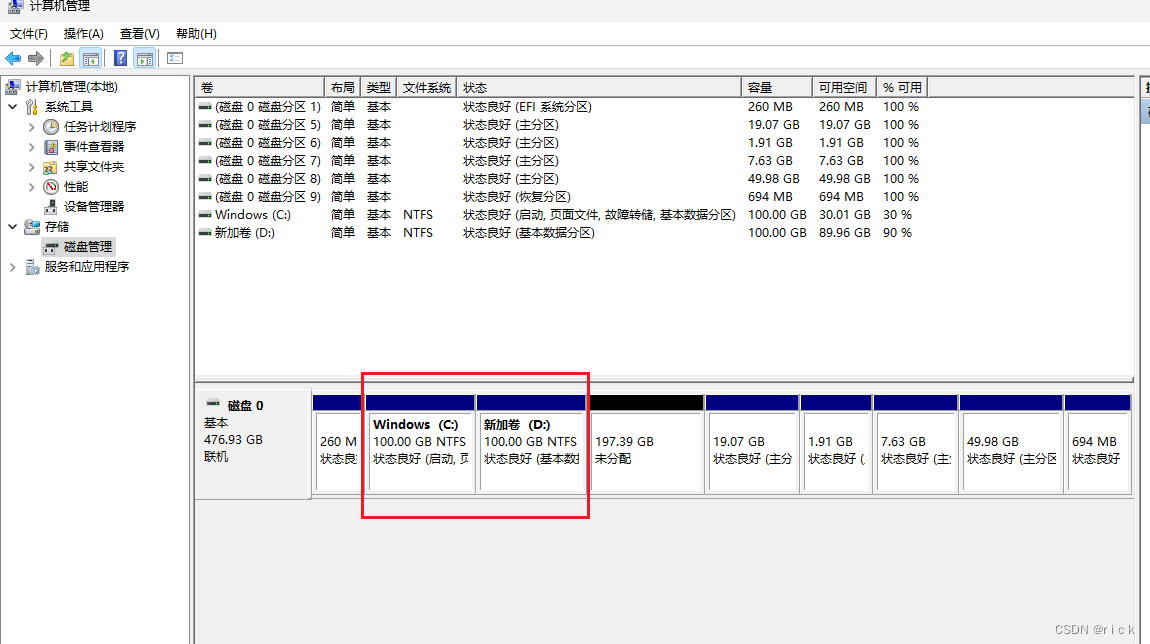

解析:建立保持时间是器件本身的工艺参数,简单解释就是采样时钟到来前后数据应该保持稳定的时间。现由于时钟与数据有不同的线网延时,且时钟相较于数据晚1ns,即时钟向后延时了1ns。故此,建立时间需要更长,保持时间可以缩短,如下图所示:

或者提供另一种思路,时钟数据相差1ns,时钟慢,故此数据需要等时钟,故从新的点看,建立时间需要增加,增加的时间就是等时钟到来的时间。反之,保持时间的约束可以放松1ns。

2,计算题

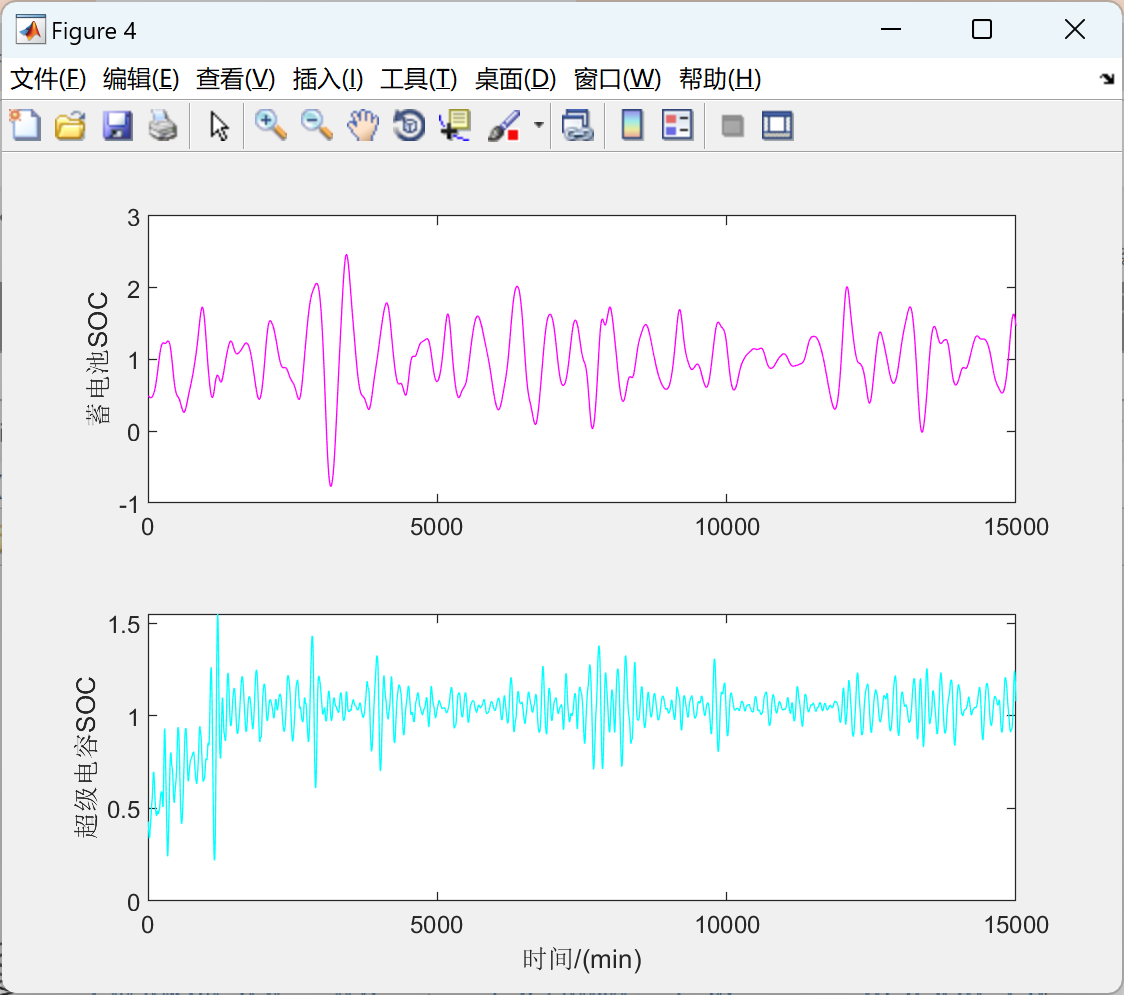

答案: 0≤Tx_delay≤16.66ns

解析:首先根据题目描述,绘制两个时钟的关系,上升沿时刻相同,即相位关系确定。根据两个时钟的上升沿关系,检查建立时间的点两个,分别如下图所示,选择较小的一个,为16.66ns,即X组合逻辑的时间不能大于该时间。保持时间只要大于0即可。

更规范的建立时间余量计算方式为 要求数据到达时间-实际数据达到时间,计算公式及其更详尽的解释见STA部分的总结。

3,选择题

答案:选 A

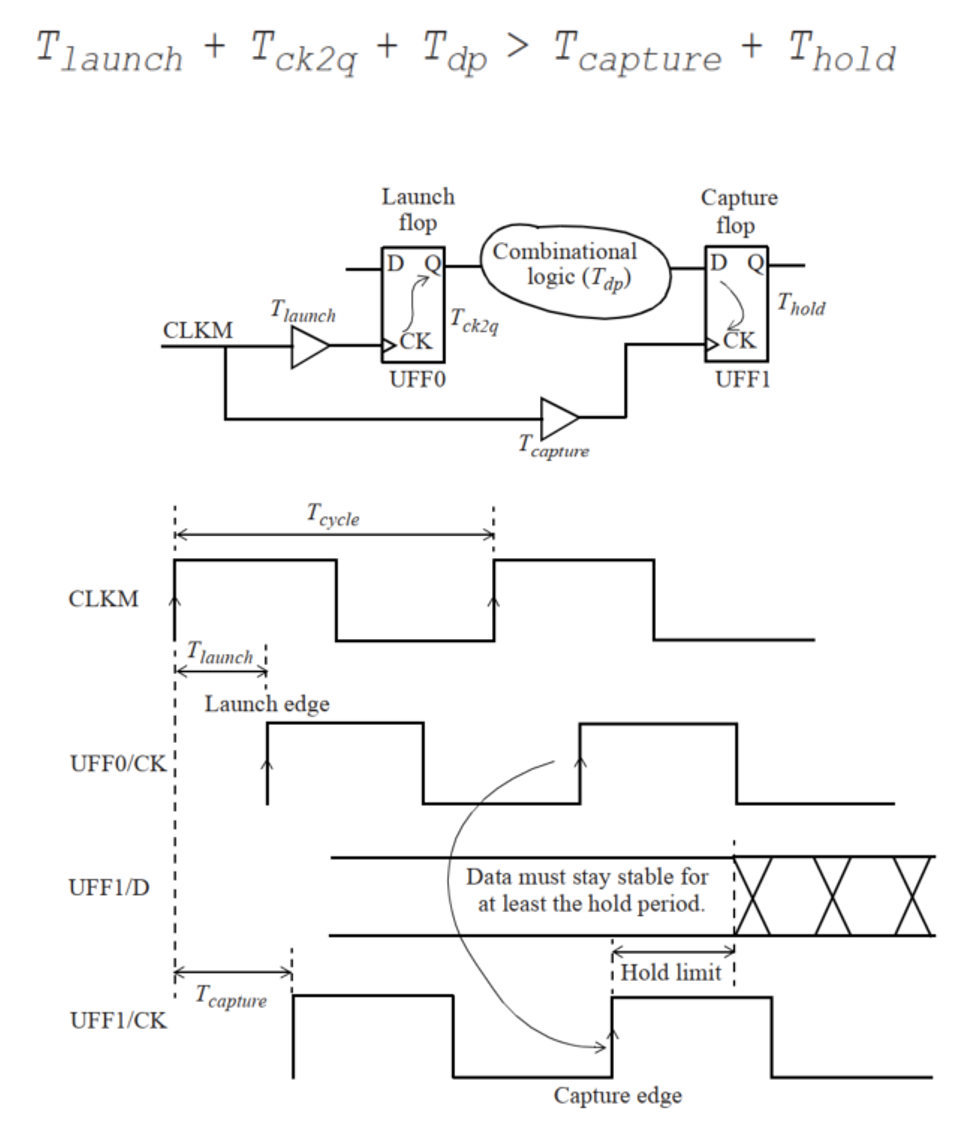

解析:题目说是hold不满足,哪些动作不能帮助我们解决hold的问题。

分析上述的公式,增加Hold,要么增加Tdp的时间,也就是延时时间,要么减少两个时钟的skew(其中Tlaunch和Tcapture的差值即为这两个寄存器的clock skew)。其余没有其他的方式了。

A 减少网络噪声的作用是提高信号的质量和可靠性,对Hold没啥作用。选A,答题就直接选了。

B 增加驱动能力会增加器件Cell的延时时间。可以帮助我们修hold问题。该说法合理,B正确。

C选择阈值电压更高的cell可以增加cell延时时间,帮助解决hold 的violation。

代工厂会提供多种电压阈值的单元库,大致可以分为三类,分别为HVT,SVT,LVT。这里的H/S/L分别为 high/standard/low阈值电压。

HVT cell: 阈值电压高,但是功耗低,速度慢

LVT cell: 阈值电压低,但是功耗高,速度快

SVT cell: 介于两者之间

D 减少时钟偏斜(clock skew),是有利于修保持违例的。

![[sqoop]hive导入mysql,其中mysql的列存在默认值列](https://img-blog.csdnimg.cn/7b88c454df43430999a49c43984ea63e.png)