uart协议:

通用异步收发器 UART(Universal Asynchronous Receiver/Transmitter),是一种串行、异步、全双工的通信协议,将所需传输的数据一位接一位地传输,在UART通讯协议中信号线上的状态位高电平代表’1’,低电平代表’0’。其特点是通信线路简单,只要一对传输线就可以实现双向通信,大大降低了成本,但传送速度较慢。

数据帧格式:

起始位+8bit数据+结束位。(还可以加上1bit的奇偶校验位)

常用波特率9600,115200.

rs232(是一种串行、异步、全双工的通信协议)

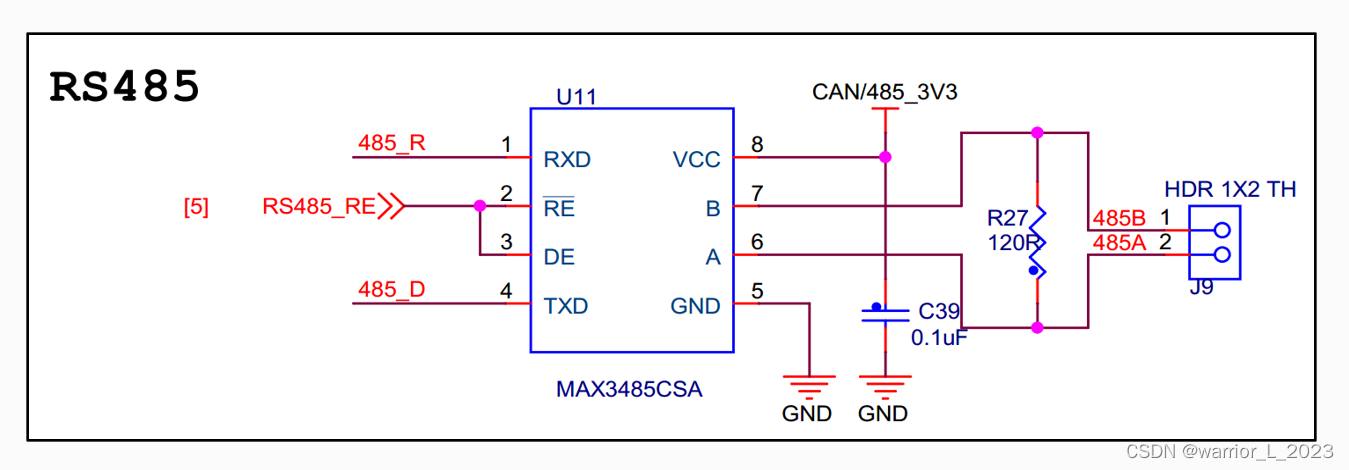

rs485(是一种串行、异步、半双工通信协议,信号采用差分传输方式,允许多个驱动器和接收器挂接在总线上,其中每个驱动器都能够脱离总线。)

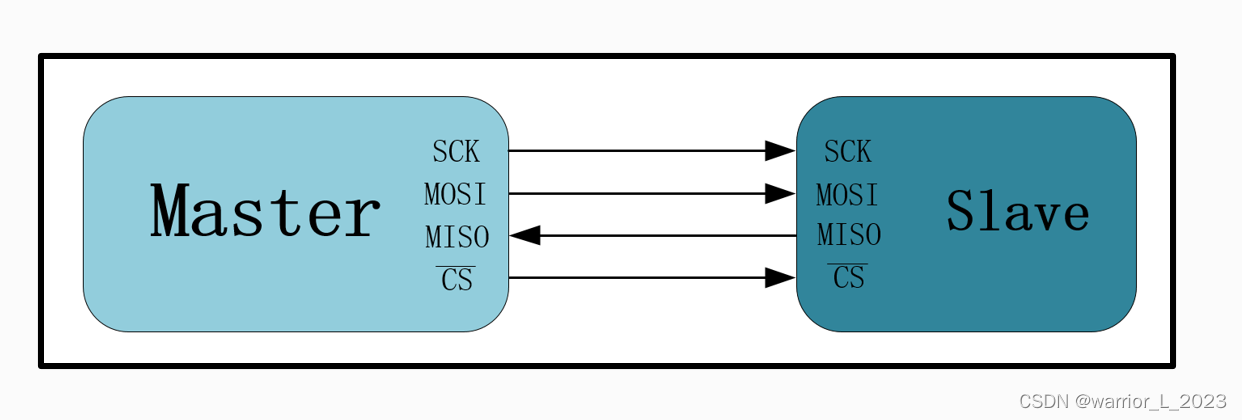

SPI协议:

(是Motorola公司提出的一种同步串行接口技术)

是一种高速、全双工、同步通信总线,在芯片中只占用四根管脚用来控制及数据传输。

应用:EEPROM、Flash、RTC、ADC、DSP等。

优缺点:全双工通信,通讯方式较为简单,相对数据传输速率较快;没有应答机制确认数据是否接收,在数据可靠性上有一定缺陷(与I2C相比)。

物理层:

SCK (Serial Clock):时钟信号线,用于同步通讯数据;

MOSI (Master Output, Slave Input):主设备输出/从设备输入引脚;

MISO (Master Input,Slave Output):主设备输入/从设备输出引脚;

𝐶𝑆(CS) ̅ (Chip Select):片选信号线,也称为CS_N。

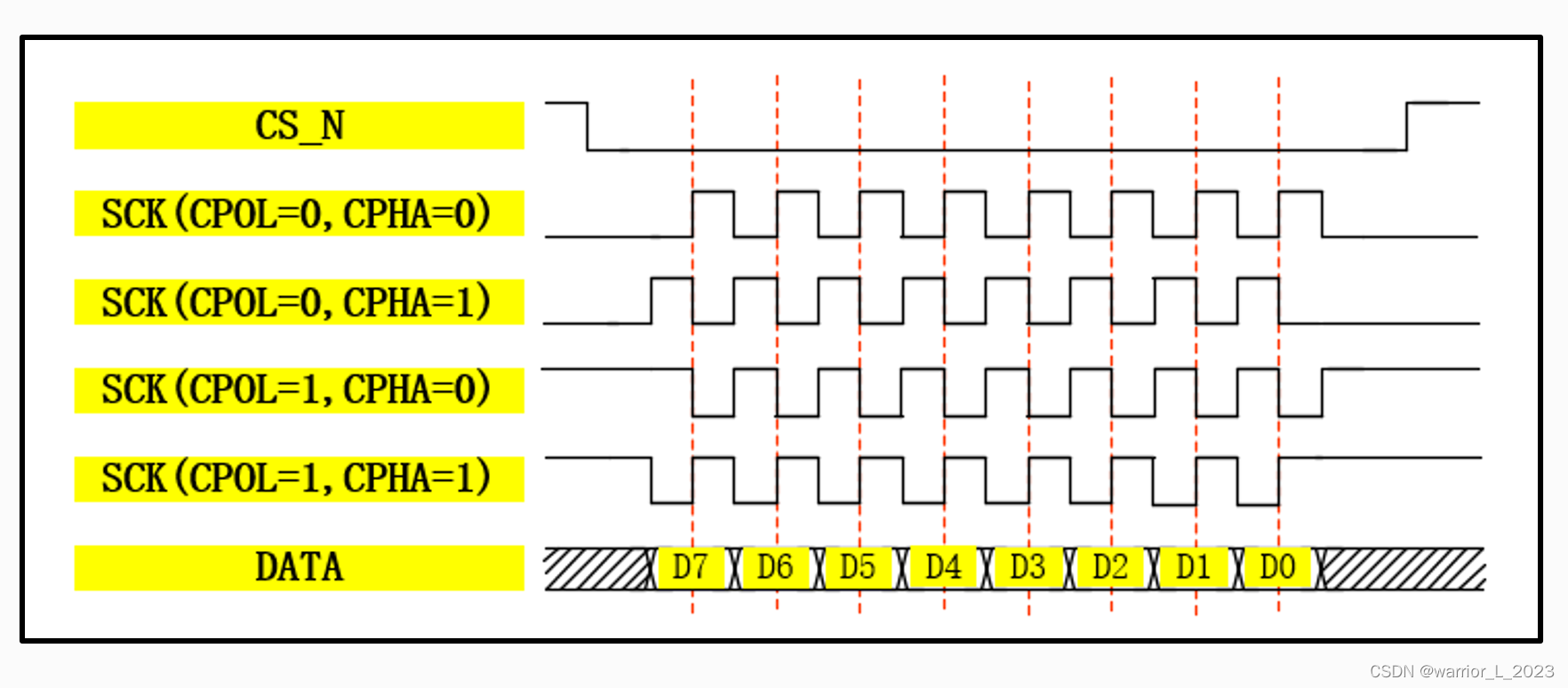

四种模式:

根据SCK的极性(cs_n==1时,sck==1orsck==0).

根据SCK的相位(sc_n==0)时(传输数据时),是奇数or偶数沿采样。

常用模式0和模式3,因为都是上升沿采样。(从机)。

重中之重:多学英语。

模块划分:

分为两种情况:

1,顶层+子模块;

2,顶层+子模块的顶层+子模块。

与fpga交互的外设(fpga要驱动的外设):

驱动外设主要需要两个部分,一个驱动时序,一般称驱动接口模块;一个工作流程控制,数据控制和命令的发送。

一般来讲一个外设,划分一个子模块的顶层+相应若干个子模块。

输入信号是否需要处理:可以划分一个子模块来处理输入信号(比如按键消抖模块,uart的rx模块)。

子模块应该怎么划分:

1,根据输出信号的产生:也就是与外设交互时序的产生。划分为1个子模块。

2,数据存储,划分1个子模块。

3,复杂工程的控制信号,划分1个子模块。

4,算法,数据处理,划分1个子模块。

5,时钟生成模块。pll模块,一般要有的。

看手册,主要看时序图,流程图,指令介绍。等。

学习的时候一定不能急,慢慢看,慢慢学。

慢一点没关系,最重要的是理解清楚,清晰的认识硬件,认识时序。

画好时序图是沉浸式编程的前提。

还差45个视频。

先定个小目标,在保质保量的前提下完成剩下的实验,争取在月末学完。

![[MQ]Win平台RocketMQ安装启动](https://img-blog.csdnimg.cn/5283b373baef44b8b00542ddcc27a348.png)