以Xilinx 公司Virtex-II 系列FPGA 为例,其基本结构由下图所示。它是主要由两大部分组成:可编程输入/输出(Programmable I/Os)部分和内部可配置(Configurable Logic)部分。

可编程输入/输出(I/Os)部分主要提供芯片与外界电路的交互接口,完成不同电气特性下对输入输出信号驱动与匹配的要求。

它被设计成可编程模式,即可以用软件灵活设置,从而调整输出驱动电流的大小以及匹配阻抗特性。同时,它能够支持多种前沿的I/O 标准。

目前,I/O 口的工作频率也日益增加,有些FPGA可以支持高达2Gbps 的数据速率。

内部可配置部分则是功能实现的主体,其主要由以下五大单元组成:

1.配置逻辑单元(Configurable Logic Block,CLB)

主要用于实现组合逻辑或者时序逻辑,包括作为基本的存储单元。每个CLB 由四个Slice 和两个三态缓冲(TBUF)组成,并通过开关矩阵与布线矩阵进行连接,如下图 所示。

四个Slice 可以组成一个移位链,分成上下两组后,每组又都有其各自独立的进位链。Slice 的内部结构是上下对称的,其上半部分结构如下图所示。它是由两个四输入的函数发生器(F 函数和G 函数)、进位逻辑、算数逻辑、多路选择器和两个存储单元构成。

其中,函数发生器本质上而言,就是根据函数表达式去查找已存的数据表。所以,它可以被配置成四输入的查找表(Look Up Table,LUT)、分布式RAM/ROM 或者是16bit 的移位寄存器。

2.块存储单元(Block SelectRAM,BRAM)

FPGA 内嵌了可编程的BRAM,扩大了其应用领域,增加灵活性。BRAM 可以配置成单端口RAM(如下图 所示),

或者是双端口RAM(如下图所示)。以XC2V3000 FPGA 为例,它的大小为18Kb,每个端口都是同步且独立的。根据深度和宽度的不同,BRAM 的大小可以在16Kx1bit 到512x36bit 范围内进行配置。另外,当需要实现更大的存储空间时,则可以通过级联多个BRAM。

3.乘法器单元(Multiplier)

FPGA 内嵌单元除了BRAM 外,还包括乘法器。与用Slice 实现乘法功能相比,内嵌乘法器运算速度更高,且功耗更低。以XC2V3000 为例,乘法器单元最大可以实现18bit x 18bit,如下图所示。

在实际应用中,比如在有限脉冲响应(Finite Impulse Response,FIR)滤波器或者无限脉冲响应(Infinite Impulse Response,IIR)滤波器中用到的数字信号处理器(Digital Signal Processor,DSP)和乘法累加器(Multiplier Accumulator,MAC)功能,通常是将乘法器单元与BRAM 配合使用,从而能够充分利用两者的优点。

4.数字时钟管理(Digital Clock Manager,DCM)

提供一个具有自我校准、时延补偿、分频倍频和移相功能的时钟管理单元。在FPGA 设计中,结合全局时钟选择缓冲和DCM,让从DCM 输出的时钟通过FPGA 内部全局时钟树到达每一个触发器,且延时基本上是相同的,这大大提高FPGA 设计的工作频率。

5.布线资源

它使FPGA 内部的所有单元互联互通,而不同的布线类型、策略决定了信号的传输速度和延时。

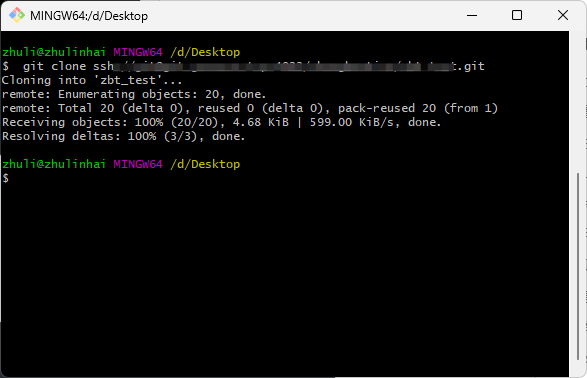

学习例程

我给小白们准备了一份礼物,下面是我精心整理的n多verilog代码。帮助小白们由浅至深的“模仿”。在模仿的过程中能够进一步的巩固之前了解的语法知识。

这些Verilog例程基本涵盖了以后可能遇到的所有用法,参考这些代码,可以做出你想要的任何设计。

当你想要用Verilog编写一段代码实现某个功能时,如果你能够想到参考哪段代码能够实现你的设计,那么恭喜你,你已经入门了!!!

所有示例代码,点击链接获取。

01-锁存器、触发器、寄存器、移位寄存器等

【免费】VerilogHDL示例代码之01-锁存器、触发器、寄存器、移位寄存器等资源-CSDN文库

02-逻辑门、三态门、mux等

【免费】VerilogHDL示例代码之02-逻辑门、三态门、mux等资源-CSDN文库

03-各种计数器

【免费】VerilogHDL示例代码之03-各种计数器资源-CSDN文库

04-各类加法器

【免费】VerilogHDL示例代码之04-各类加法器资源-CSDN文库

05-乘法器

【免费】VerilogHDL示例代码之05-乘法器资源-CSDN文库

06-异步复位同步释放

【免费】VerilogHDL示例代码之06-异步复位同步释放资源-CSDN文库

07-分频

【免费】VerilogHDL示例代码之07-分频资源-CSDN文库

08-语法语句

【免费】VerilogHDL示例代码之08-语法语句资源-CSDN文库

09-串并转换

【免费】VerilogHDL示例代码之09-串并转换资源-CSDN文库

10-状态机设计

【免费】VerilogHDL示例代码之10-状态机设计资源-CSDN文库

11-编解码应用

【免费】VerilogHDL示例代码之11-编解码应用资源-CSDN文库

12-仿真语法举例

【免费】VerilogHDL示例代码之12-仿真语法举例资源-CSDN文库

13-进阶设计

【免费】VerilogHDL示例代码之13-进阶设计资源-CSDN文库

我将Verilog的语法进行了总结,写了13篇文章,让小白“快速见识猪如何跑”,每一篇讲解一类语法,结合正确的示例代码和错误的示例代码,有的章节对个别语法进行了归纳总结,帮助初学者加深理解。详情点击

小白如何快速入门Verilog?-CSDN博客

Verilog语法之〇:Verilog HDL简介/Verilog语法介绍-CSDN博客

Verilog语法之一:简单的Verilog HDL模块-CSDN博客

Verilog语法之二:常量-CSDN博客

Verilog语法之三:变量-CSDN博客

Verilog语法之四:运算符-CSDN博客

。。。。。。

更多课程,敬请期待