文章目录

- 一、问题描述

- 二、verilog源码

- 三、仿真结果

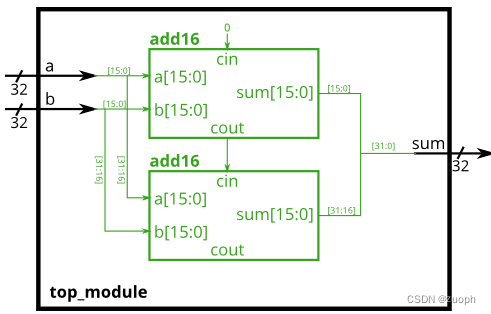

一、问题描述

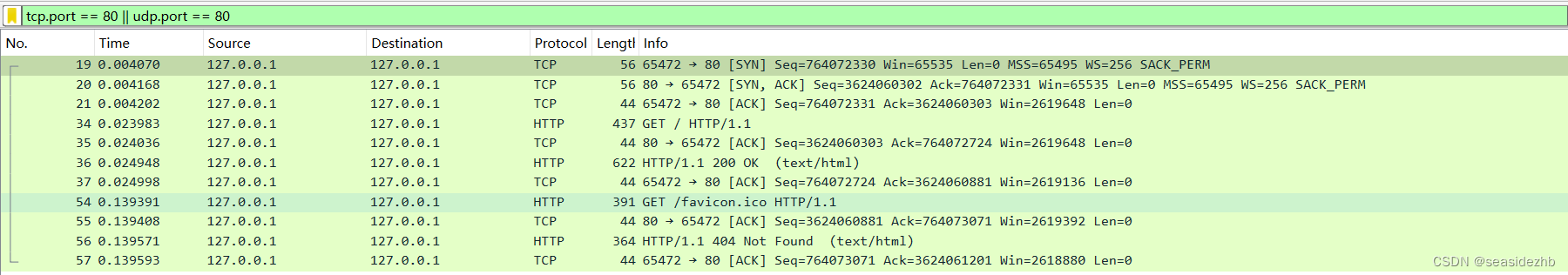

您将获得一个执行 16 位加法的模块 add16 。实例化其中两个以创建一个 32 位加法器。一个 add16 模块在接收到第一个加法器的进位结果后,计算加法结果的低 16 位,而第二个 add16 模块计算结果的高16 位。 32 位加法器不需要处理进出(假设为 0)或进出(忽略),但内部模块需要处理才能正常运行。(换句话说,模块 add16 执行 16 位 a + b + cin,而您的模块执行 32 位 a + b)。

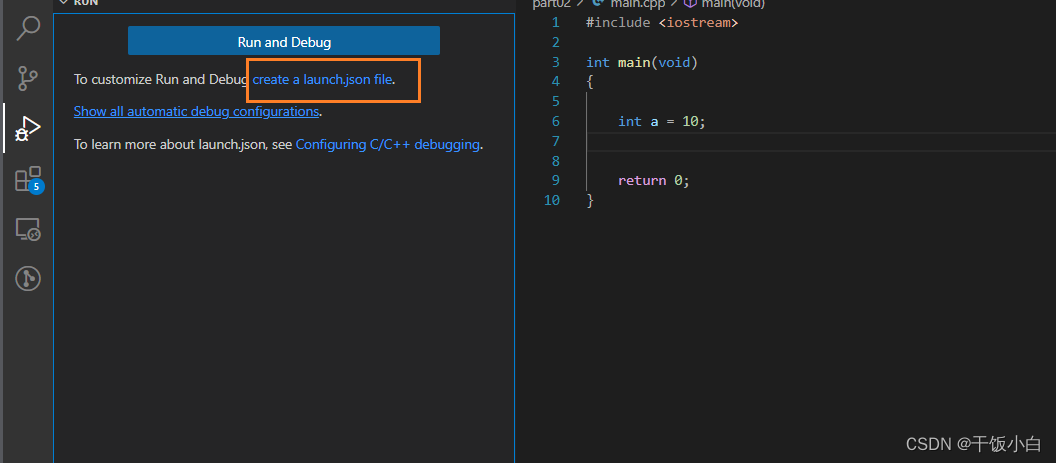

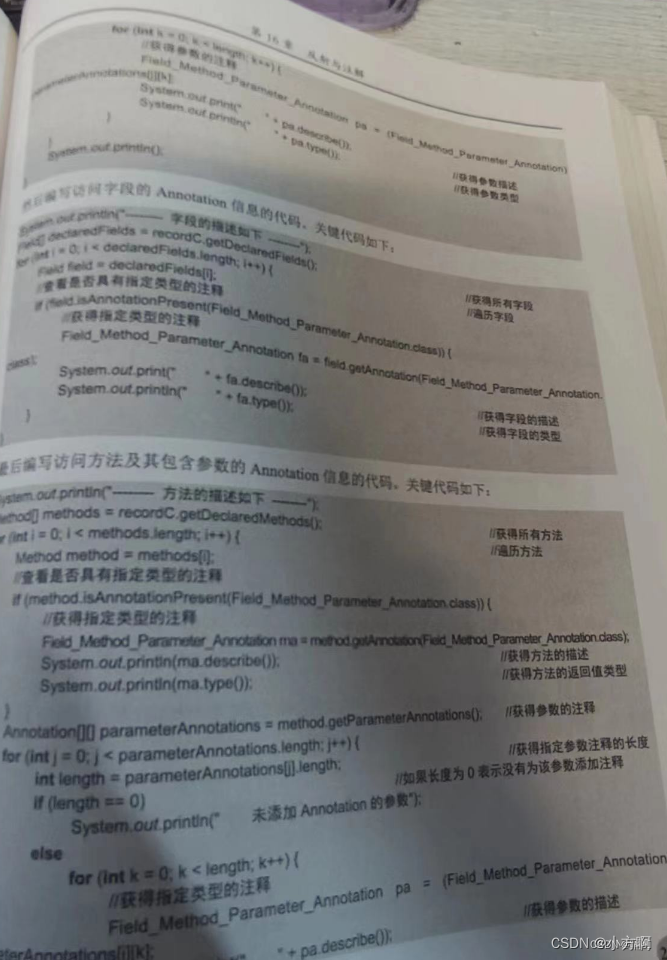

如下图所示将模块连接在一起。提供的模块 add16 具有以下声明:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

二、verilog源码

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire c1, c2;

add16 u1 (a[15:0], b[15:0], 1'b0, sum[15:0], c1);

add16 u2 (a[31:16], b[31:16], c1, sum[31:16], c2);

endmodule

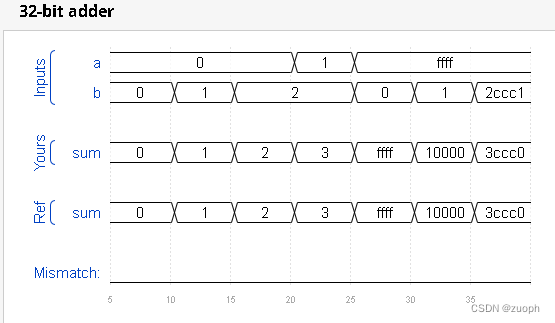

三、仿真结果

转载请注明出处!