目录

Ⅰ. 实践说明

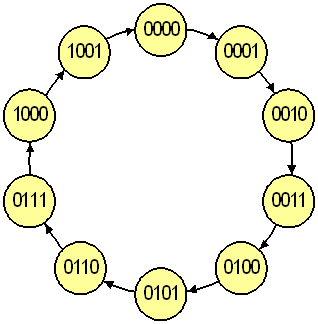

0x00 十进制计数器

0x01 有限状态机(FSM)

Ⅱ. 实践部分

0x00 4-bit 2421 十进制计数器

Ⅰ. 实践说明

0x00 十进制计数器

十进制计数器是一种以十进制运算的计数器,从 0 数到 9,然后返回 0 状态。由于它需要显示 0 到 9 的数字,因此它使用一个可处理 4 位以上的 flip-flop,并使用 码输出计数值。

| Up/Down Counter |

|

|

|

|

0x01 有限状态机(FSM)

有限状态机 (FSM) 是一种用于设计计算机程序和电路的数学模型。

FSM 由三个集合 以及两个函数

组成:

| I | 输入集合,有限状态机接受的输入符号的集合 |

| O | 输出集合,有限状态机产生的输出符号的集合。 |

| S | 状态集合,有限状态机可能处于的状态的集合。 |

| f | 下一个状态函数 F(I,S) |

| G | 输出函数: Moore model -> G(S) / Mealy model -> G(I,S) |

Ⅱ. 实践部分

0x00 4-bit 2421 十进制计数器

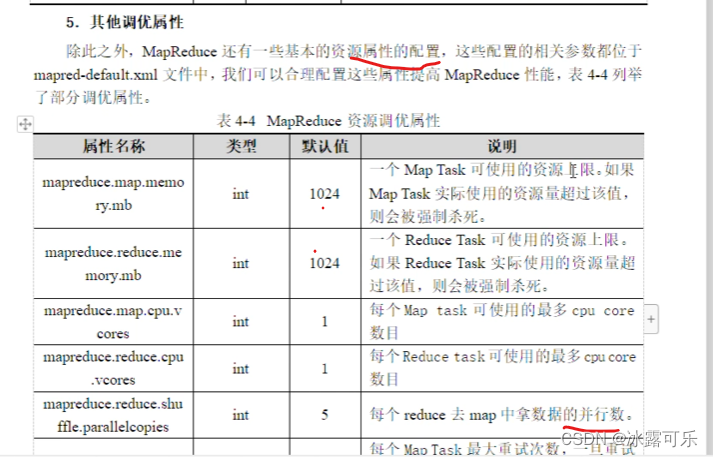

| 当前状态 Q | 后续状态 Q* | |

| input x=0 | input x=1 | |

| 0000 | 0000 | 0001 |

| 0001 | 0001 | 0010 |

| 0010 | 0010 | 0011 |

| 0011 | 0011 | 0100 |

| 0100 | 0100 | 1011 |

| 1011 | 1011 | 1100 |

| 1100 | 1100 | 1101 |

| 1101 | 1101 | 1110 |

| 1110 | 1110 | 1111 |

| 1111 | 1111 | 0000 |

💬 Design source:

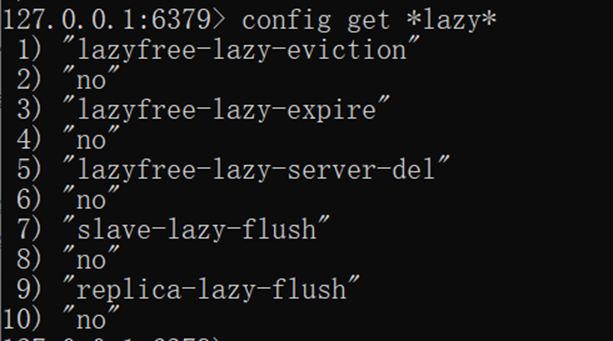

`timescale 1ns / 1psmodule DC_2(input reset,input clk,input x,output z,output [3:0]out

);reg [3:0]out;

reg z;always @(posedge !clk) beginif(reset) beginout[3] = 1'b0;out[2] = 1'b0;out[1] = 1'b0;out[0] = 1'b0;z = 1'b0;endelse beginif((x == 1'b1)) beginout[3] <= (out[2]&(~out[1])&(~out[0])) | (out[3]&out[2]&(~out[1])&out[0]) | (out[3]&(~out[2])&out[1]&out[0]) | (out[3]&out[2]&out[1]&(~out[0]));out[2] <= (out[3]&out[2]&(~out[1])) | ((~out[2])&out[1]&out[0]) | (out[3]&out[2]&out[1]&(~out[0]));out[1] <= ((~out[3])&out[2]&(~out[1])&(~out[0])) | ((~out[3])&(~out[2])&(~out[1])&out[0]) | ((~out[3])&(~out[2])&out[1]&(~out[0])) | (out[3]&out[2]&(~out[1])&out[0]) | (out[3]&out[2]&out[1]&(~out[0]));out[0] <= ((~out[3])&(~out[1])&(~out[0])) | (out[3]&out[2]&(~out[1])&(~out[0])) | (out[3]&out[2]&out[1]&(~out[0])) | ((~out[3])&(~out[2])&out[1]&(~out[0]));if (out[3] && out[2] && out[1] && out[0]) z <= 1'b1;endend

endendmodule💬 Testbench:

`timescale 1ns / 1psmodule DC_2_tb;reg clk,reset,x;

wire [3:0]out,z;DC_2 u_DC_2(.clk(clk ),.reset(reset ),.x(x ),.out(out ),.z(z )

);initial clk = 1'b0;

initial reset = 1'b1;

initial x = 1'b0;always clk = #20 ~clk;always@(reset) beginreset = #50 ~reset;

endalways@(x) beginx = #110 ~x;x = #20 ~x;x = #60 ~x;x = #20 ~x;x = #60 ~x;x = #20 ~x;x = #60 ~x;x = #20 ~x;x = #60 ~x;x = #20 ~x;x = #60 ~x;x = #20 ~x;x = #60 ~x;x = #20 ~x;x = #60 ~x;x = #20 ~x;x = #60 ~x;x = #20 ~x;x = #60 ~x;x = #20 ~x;

endinitial begin#860$finish;

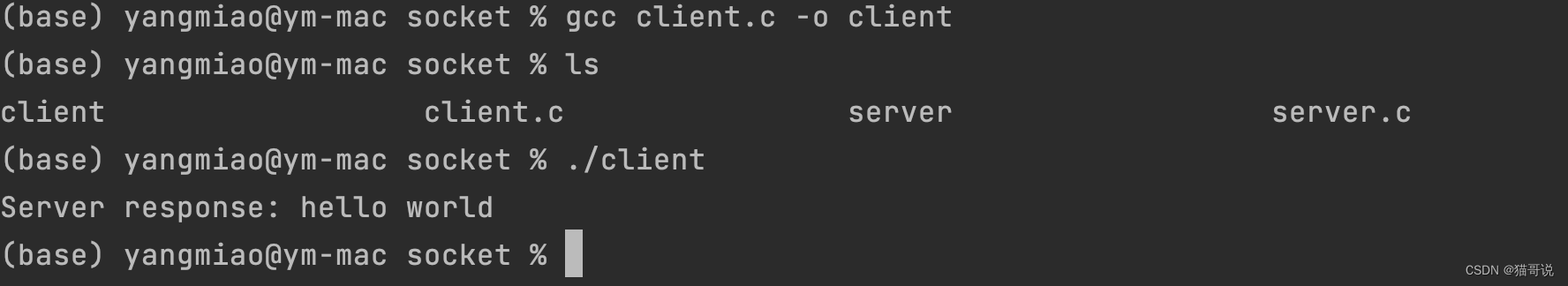

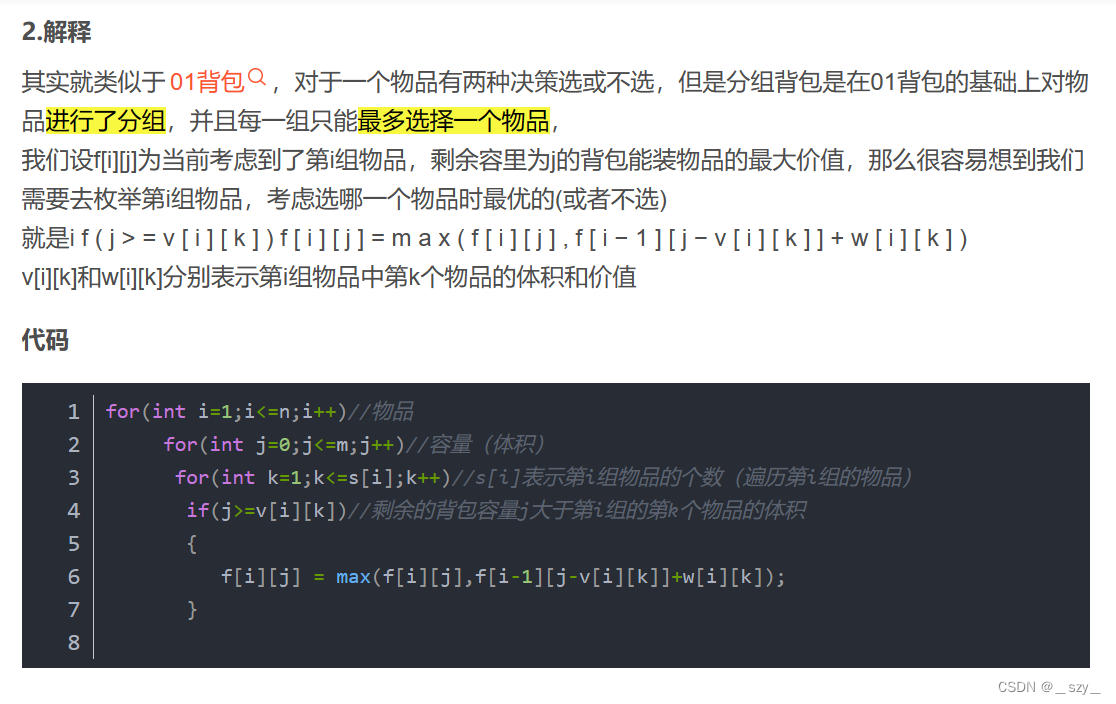

endendmodule🚩 运行结果如下:

4 位 2421 十进制计数器是一个重复 0 至 9 的计数器,可以用 4 位来表示,但不同的是,0 至 4 与一般的十进制计数器相同,而 5 至 9 则用一般十进制计数器中的 11 至 15 表示。

当输入值 x 为 0 时保持当前状态,当输入值 x 为 1 时进入下一个数字。

在数到 9(1111)后,我们需要处理返回 0(0000)的问题。我们将其编写为下降沿触发器,模拟结果表明,每当时钟值从 1 下降到 0 时,x 的输入值就会反映在输出中。

📌 [ 笔者 ] floyd

📃 [ 更新 ] 2023.11.13

❌ [ 勘误 ] /* 暂无 */

📜 [ 声明 ] 由于作者水平有限,本文有错误和不准确之处在所难免,本人也很想知道这些错误,恳望读者批评指正!| 📜 参考资料 Introduction to Logic and Computer Design, Alan Marcovitz, McGrawHill, 2008 Microsoft. MSDN(Microsoft Developer Network)[EB/OL]. []. . 百度百科[EB/OL]. []. https://baike.baidu.com/. |