导读:在基于FPGA的网络设备中,精确的时间同步至关重要。IEEE 1588标准定义的精确时间协议(PTP)为网络中的设备提供了纳秒级的时间同步。本文将介绍虹科提供的适用于基于FPGA的网络设备的IEEE 1588透明时钟(TC)架构,帮助您实现精确时间同步和高效通信。

在分布式系统中,传感器/执行器的事件和操作需要进行精确的时间协调,因为时钟差异可能导致操作失败。为了确保时间同步,每个组件都需要具备与其对等组件一致的实时时钟,这需要时间同步的常识。

随着电信网络从传统的时分复用 (TDM) 发展到基于分组的网络,额外的同步协议已成为必要。因此,近几十年来开发了多种同步技术,如 IRIG-B、LORAN-C、NTP、基于GPS的同步和SyncE。然而,它们不适合需要精确时间且成本较低的应用领域。

通过精确时间协议 (PTP),能够以最少的网络、计算和硬件资源需求达到亚微秒精度。鉴于此,IEEE 1588标准中定义的PTP正在成为许多需要精确时间同步的应用的最可行的解决方案。虹科推出用于可重新配置设备的IEEE 1588透明时钟 (TC) 可扩展架构,该逻辑解决了PTP实现的主要缺点之一,即级联拓扑中的错误累积。

PTP操作过程

1、PTP操作类型

PTP操作可分为两个过程:时间同步和频率同步;

时间同步(或偏移调整):偏移量计算为主从时间之差;

频率同步(或频率调整):频率漂移为在两个N间隔的同步消息之间传递的从机时间差和主机时间差之间的比率。

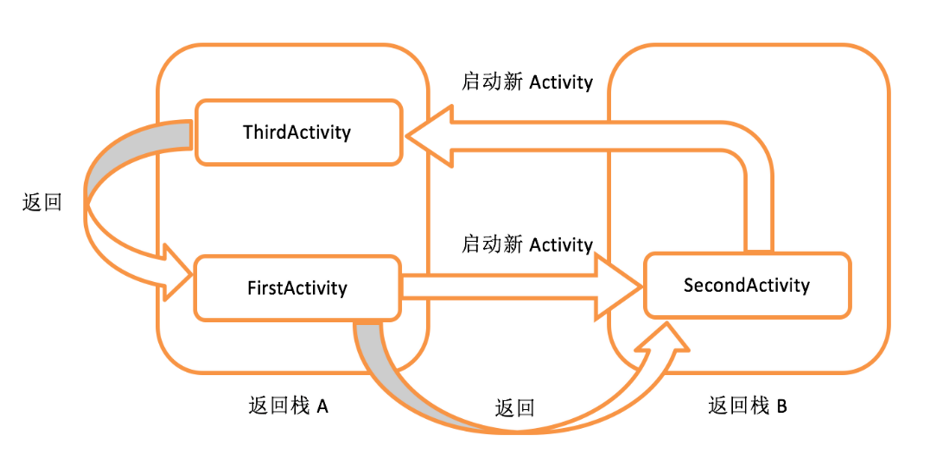

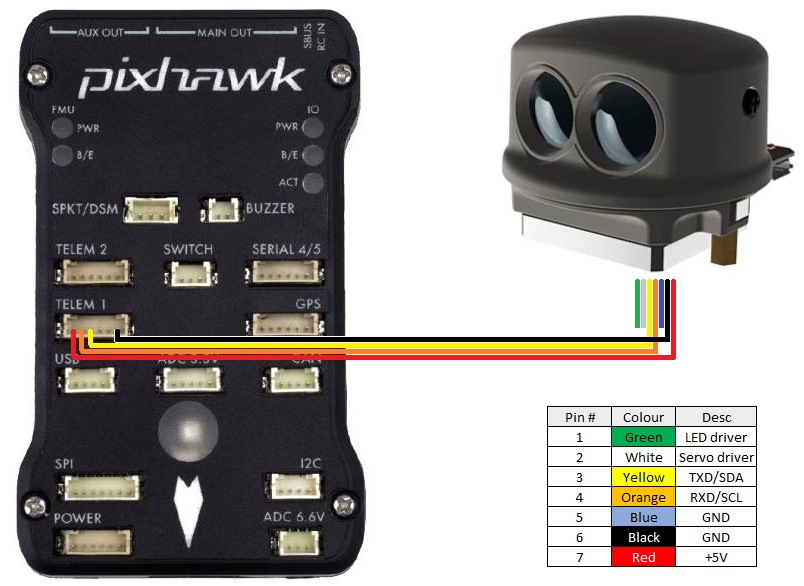

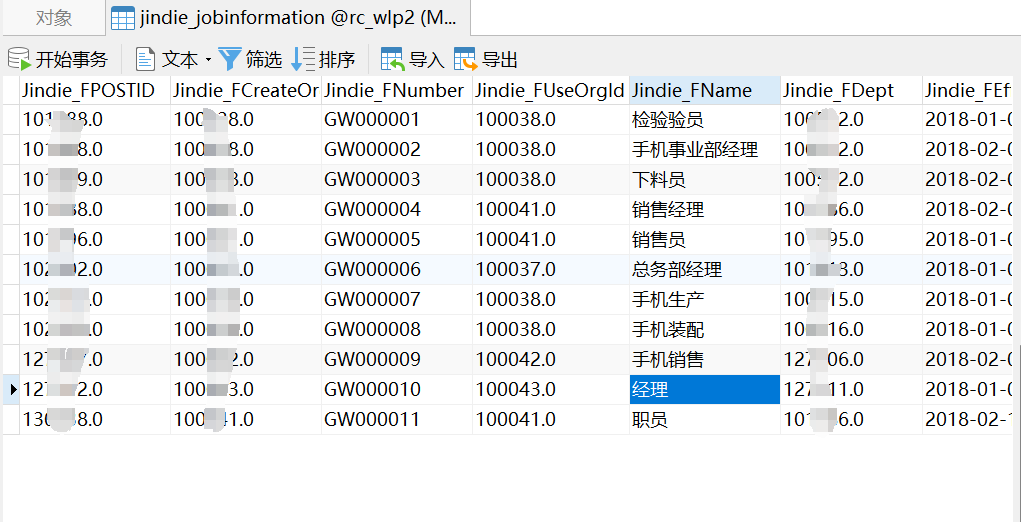

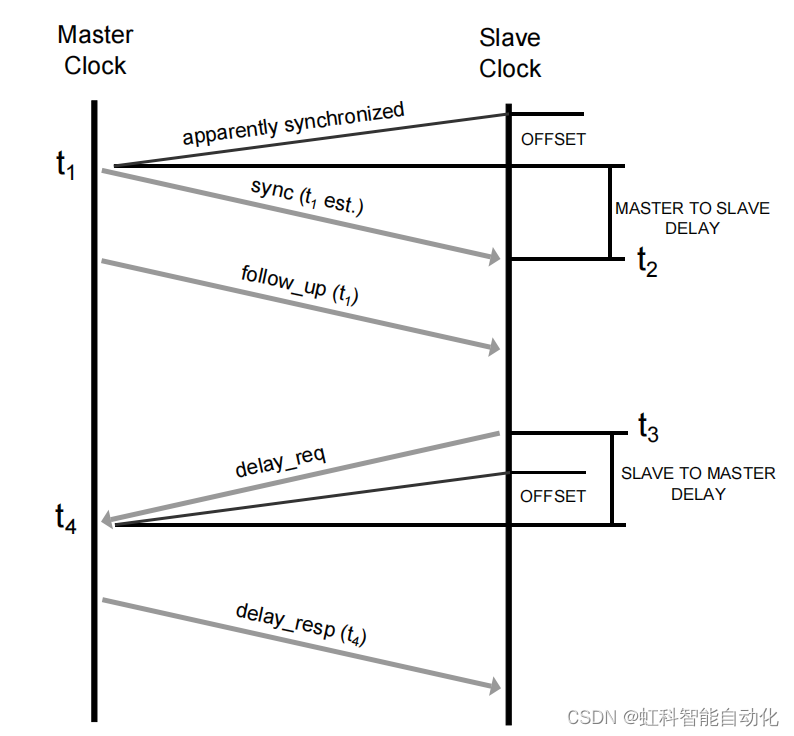

图1. 延迟请求响应机制

2、延迟测量

PTP消息中发送的时间戳必须通过传播延迟进行纠正,传播延迟可以使用标准中定义的两种机制之一进行测量:延迟请求响应机制或对等延迟机制。

3、PTP时钟设备

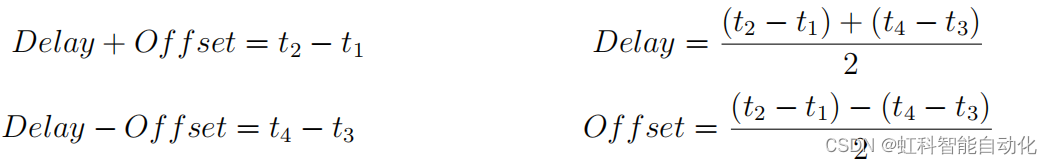

PTP系统由PTP和非PTP设备的组合组成。PTP设备分为普通时钟(OC)、边界时钟(BC)、透明时钟(TC)和管理节点(MN)。

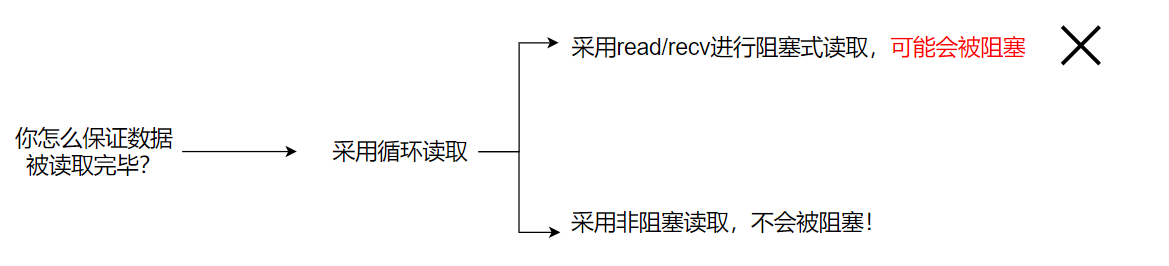

图2. PTP网络示意图

图2展示了一个简单PTP网络:OC是包含PTP时钟和单个物理网络连接的系统终端设备,而BC是具有多个物理端口的网络设备,它们不转发PTP接收到的消息,而是与主站同步并生成新的PTP消息以与其余从站共享其自己的定时参考。

TC有两种类型:端到端(E2E)TC和点对点(P2P)TC,它们也是网络设备。一方面,E2E TC像正常网络节点一样转发所有PTP和非PTP消息,此外,它们测量消息穿越TC所需的时间,称为驻留时间,并将其累积在PTP 中称为 CorrectionField的特殊字段。另一方面,P2P TC使用对等延迟机制来测量两个直接连接的端口(链路对等点)之间的链路延迟,并使用与Sync消息的入口传输路径相关的驻留时间和链路延迟来更新CorrectionField ,允许在网络拓扑更改后更快地重新配置。

此外,每个PTP设备可以作为一步或两步模式工作:一步时钟根据同步和延迟请求事件消息实时生成时间戳,而两步时钟则根据Follow Up和Delay Resp一般消息。

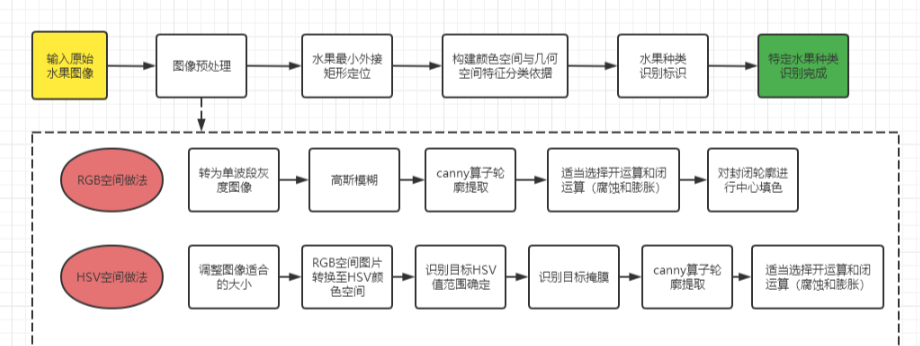

4、PTP执行

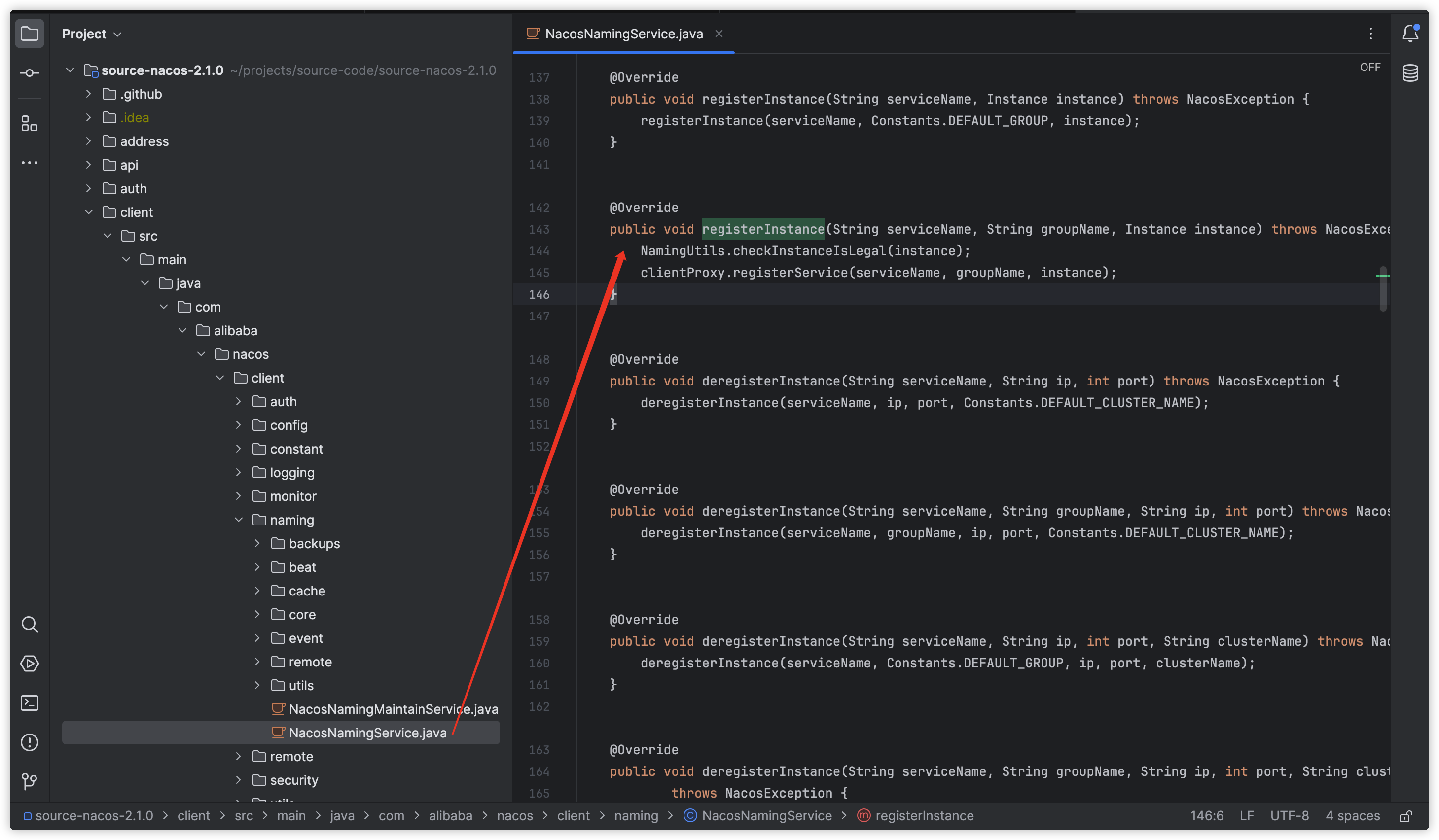

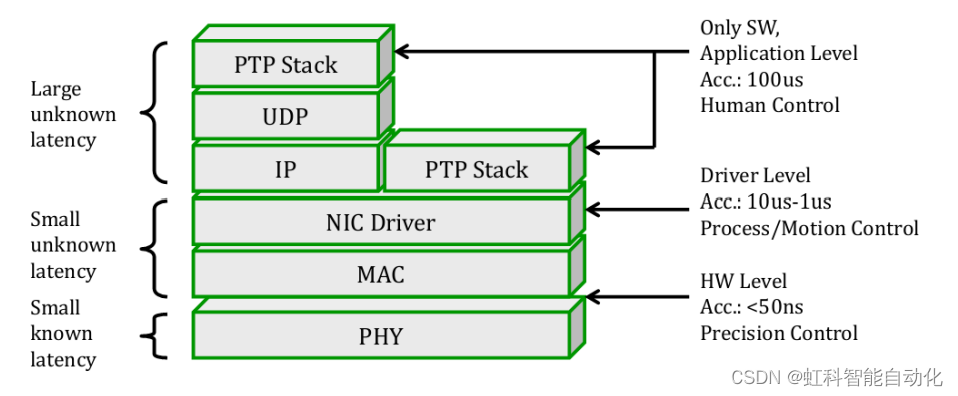

硬件与软件实现:PTP环境提供不同的可能时间戳点,如图3所示。结果的精度取决于时间戳的精度 。一方面,在网络接口卡 (NIC) 驱动程序或应用程序层中获取时间戳的纯软件解决方案具有平台独立性的优势,但会经历通过协议栈的消息传输延迟的巨大变化(也称为抖动)。驱动程序级别的时间戳是最佳软件解决方案,但需要修改网络驱动程序。

图3. 可能的时间戳点

另一方面,在硬件辅助方法中,时间戳是在介质独立接口(MII)处获取的。带有时间戳的消息越接近物理层,所达到的准确性就越好。由于硬件的帮助,使用IP内核和现场可编程门阵列 (FPGA) 已成为最精确和准确的时间戳方法。

其他实现方面:不同供应商的PTP IP核往往具有相似的架构。他们通常使用软CPU,例如Xilinx FPGA 中的Microblaze,包含用户应用程序和PTP堆栈软件,并在同一FPGA中构建完整的SoC解决方案。这些IP核通常由至少两个称为实时时钟 (RTC) 和时间戳单元 (TSU) 的硬件模块组成。RTC通常是一个64位计数器,表示秒和纳秒,并且可以通过更改内核的某些配置寄存器的值进行调整。TSU负责存储有关帧的信息,例如序列 ID、消息类型或时钟标识,以及时间戳信息。

基于FPGA的TC架构

1、实时时钟(RTC)

名为RTC的块代表可选的同步时钟源,例如,它可以是 IEEE 1588或GPS时钟。RTC 可以由一个计数器形成,该计数器在每个时钟周期按系统时钟周期递增。

2、循环冗余校验 (CRC) 检查器/发生器

CRC检查器模块检查接收到的以太网帧的帧校验序列(FCS)字段,以便检测传输过程中损坏的数据(由 于数据丢失或更改而导致的错误)。另一方面,CRC生成器模块重新生成新的FCS字段并将其附加在帧末尾,如IEEE 802.3标准中所定义。

3、On-The-Fly (OTF) 更正

OTF Correction的模块负责将相应的驻留时间动态添加到PTPv2事件数据包的CorrectionField字段中,如IEEE 1588-2008中针对单步TC的定义。也就是说,它不会等到接收到整个PTP消息才计算停留时间并将其添加到CorrectionField中。相反,一旦知道传入消息的CorrectionField,就会尽快将停留时间添加到其中。

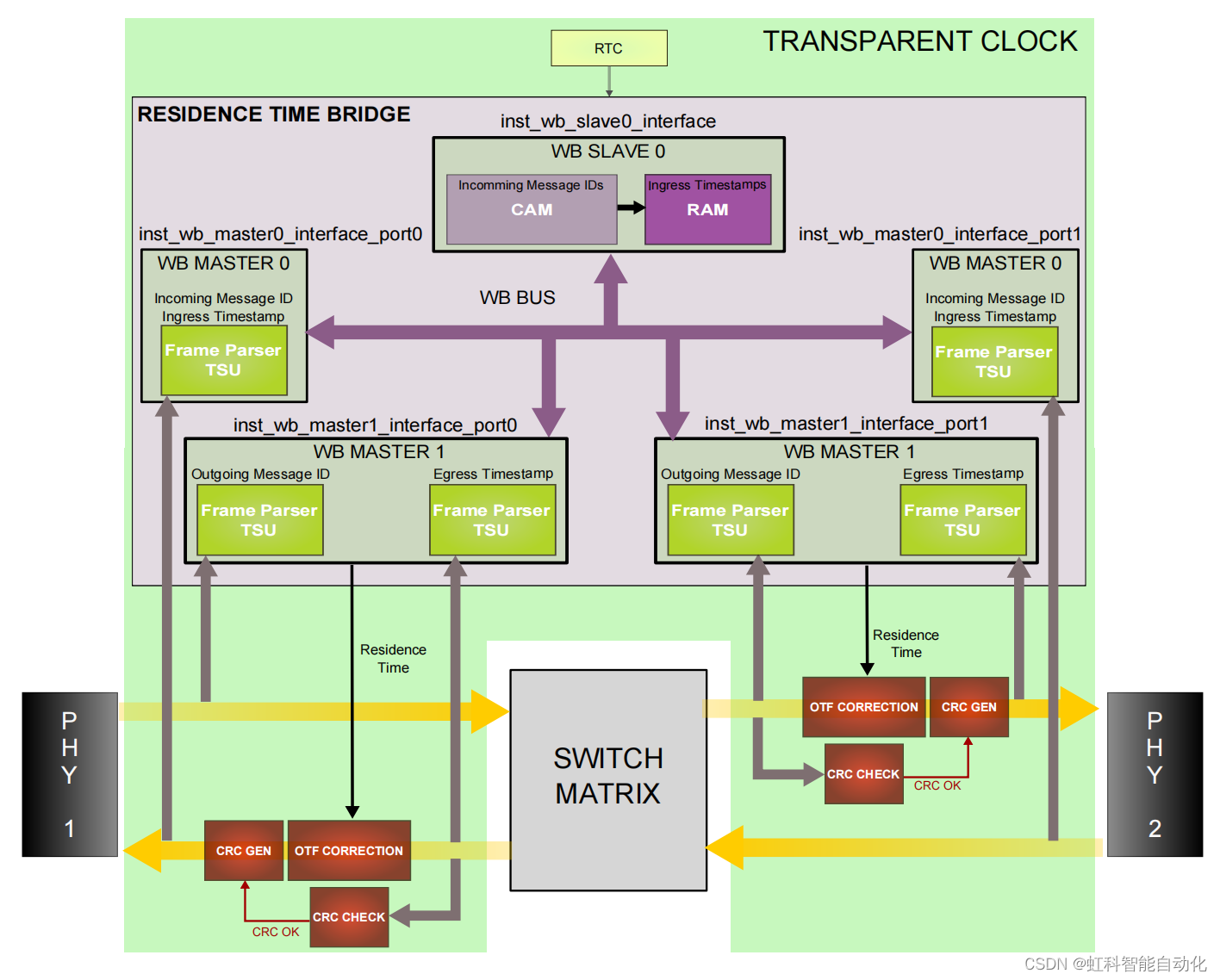

4、驻留时间桥

该模块计算自PTP帧进入和离开TC以来经过的时间。每个消息的停留时间值被向下传递到OTF校正模块。由于入口时间戳临时存储在存储器中,并且计算的停留时间被传递到负责更新CorrectionField的模块。

图4. 驻留时间桥框图

5、实验结果

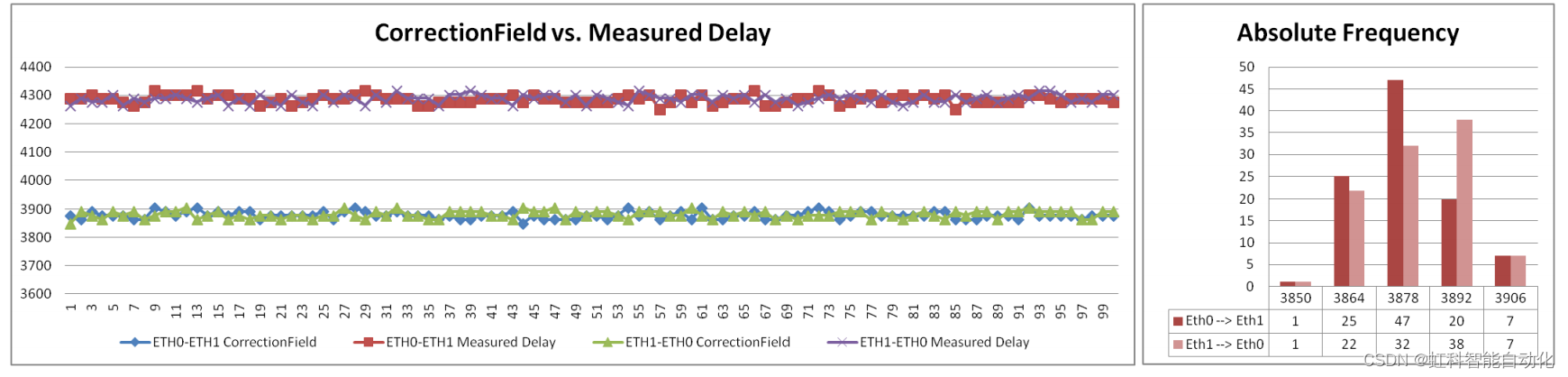

图5. 左侧为CorrectionField和测量延迟样本之间的比较;右侧为停留时间出现的频率

通过复制必要的模块,该设计可以轻松扩展到两个以上的端口:除了新的OTF校正器之外,每个新端口还应将两个额外的WB Master 0和WB Master 1子模块集成到驻留时间桥中,CRC检查器和CRC生成器连接到每个新的出口端口。在资源利用方面,每个额外端口的空间需求比较少数的Slices Registers和LUTs。不需要复制WB Slave 0,但必须调整CAM/RAM存储器的大小以应对PTP流量并在拥塞条件下正确执行。

虹科 IEEE 1588 IP 核方案

虹科IEEE1588v2兼容时钟同步IP内核,它能够准确地为IEEE 1588报文打上时间戳,并提供兼容的计时器,广泛应用于汽车、工业、广播和航空航天等行业。其能够提供许多应用所需的精确时间同步,而不需要任何新的基础设施。

TC应在级联拓扑中使用,其中网络设备拥塞状况导致的延迟可能会影响协议性能。所提出的TC架构是以简单的方式开发具有TC功能的以太网交换机的可行解决方案,具有完全的可扩展性和最小的资源利用率。由于块RAM是利用率最高的资源,并且它们直接取决于CAM和RAM大小,因此应在实现过程中优化这两个元素。如需进一步了解虹科IEEE 1588 PTP IP核解决方案,欢迎随时联系我们。

了解虹科工业通讯更多资讯,欢迎前往【虹科智能互联】官方网站:https://www.hoautom.com/precisetimebasic-ieee-1588-2008-v2-ptp-ip-core/?from=industrynews