(原创声明:该文是作者的原创,面向对象是FPGA入门者,后续会有进阶的高级教程。宗旨是让每个想做FPGA的人轻松入门,作者不光让大家知其然,还要让大家知其所以然!每个工程作者都搭建了全自动化的仿真环境,只需要双击top_tb.bat文件就可以完成整个的仿真(前提是安装了modelsim),降低了初学者的门槛。如需整个工程请留言(WX:Blue23Light),不收任何费用,但是仅供参考,不建议大家获得资料后从事一些商业活动!)

前面的计数器加法的时候讲解过计数器的第0位是计数时钟的2分频,第1位是计数时钟的4分频,第2位是计数时钟的8分频......还有就是计数分频,每计数n次信号反转一次,就是高低电平都是n次,那就是计数时钟的2n次分频,这个2n一定是偶数。

但是在实际的应用中,如果需要计数时钟的奇数次分频,需要如何实现呢?比如实现计数时钟的5分频,而且要求占空比是50%,就是高电平2.5时钟周期,低电平2.5时钟周期。

前期的时序逻辑我们一般都是用的系统时钟的上升沿做为触发条件,对于计数时钟的5分频,用系统时钟的上升沿计数只能得到高电平3个时钟周期,低电平2个时钟周期,或者高电平2个时钟周期,低电平3个时钟周期,不满足占空比50%的条件。

这时候就要考虑用系统时钟的下降沿做为触发条件,对于计数时钟的5分频,用系统时钟的下升沿计数也只能得到高电平3个时钟周期,低电平2个时钟周期,或者高电平2个时钟周期,低电平3个时钟周期,也不满足占空比50%的条件。

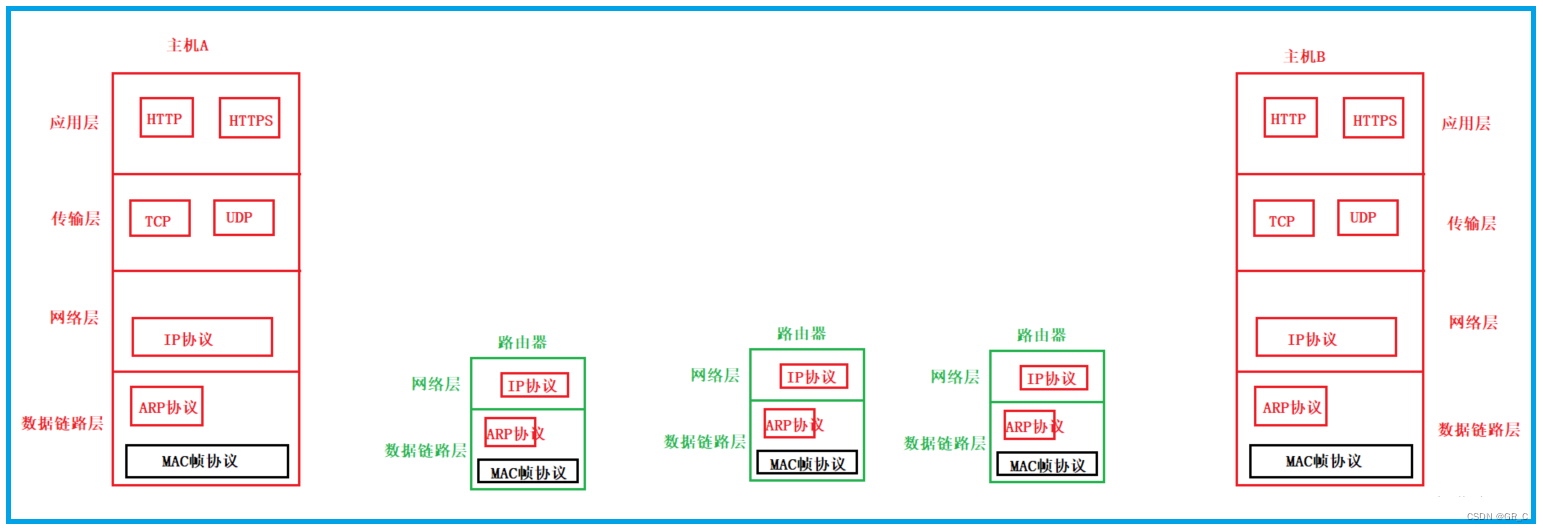

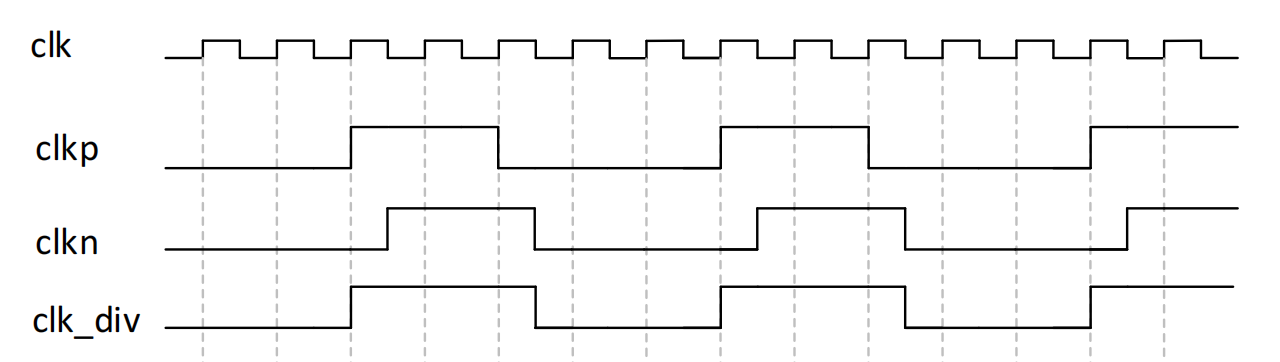

但是用系统时钟的上升沿和用系统时钟的下降沿分别触发,得到的分频信号会有半个时钟的相位差,这个相位差太关键了,为了直观,绘制了如下的时序图,clk是系统时钟,cklp是时钟上升沿触发的分频信号,ckln是时钟下升沿触发的分频信号,我们仔细观察一下,如果把clkp和clkn取或运算,就可以实现系统时钟clk的5分频,其中高电平是2.5个系统时钟,低电平也是2.5个系统时钟。

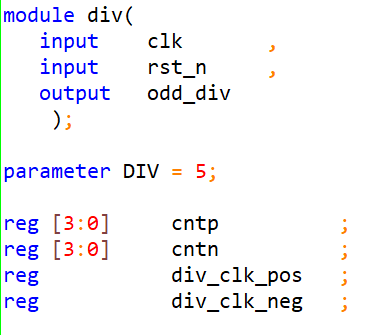

理解了设计的思路,FPGA的设计就非常的简单了,只需要两个计数器就可以实现任意计数时钟的奇数次分频。如下所示,可以通过定义DIV完成不同奇数次的分频。

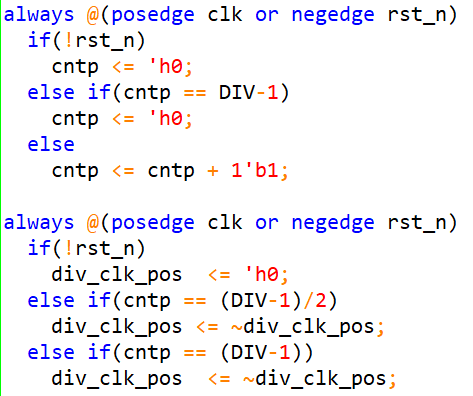

用计数时钟的上升沿实现计数器cntp和分频信号div_clk_pos。

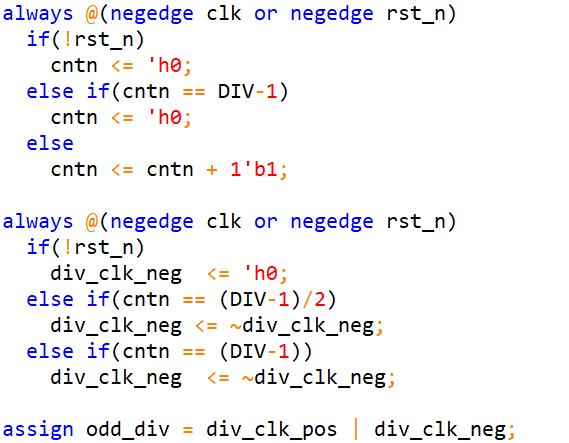

用计数时钟的下升沿实现计数器cntn和分频信号div_clk_neg。最后将div_clk_pos和div_clk_neg取或既可得到最终的分频信号。

双击sim目录下的top_tb.bat文件,完成自动化仿真。

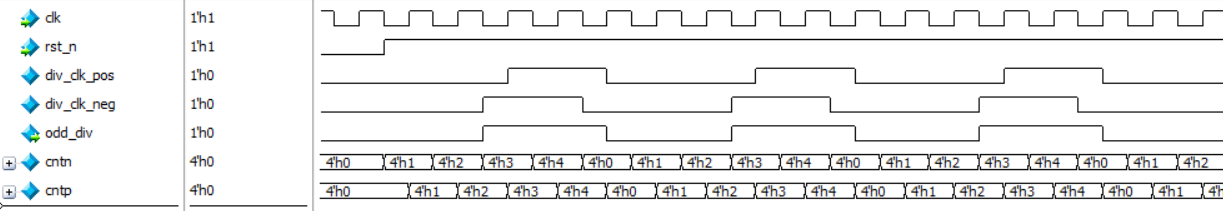

modelsim的仿真波形如下所示,和我们上面的分析是一致的,fpga设计功能正常。

计数时钟的奇数次分频是一个非常经典的面试题,看似只涉及非常简单的计数器,其实也考察了对时钟触发条件的理解,我们平常一般用的是时钟的上升沿,很少用时钟的下降沿,因为如果同时使用时钟的上升沿和下降沿会让时序分析变得非常复杂。但是合理的使用时钟的下降沿,能让一些设计非常的简单,这需要读者慢慢的体会。

![[架构之路-254]:目标系统 - 设计方法 - 软件工程 - 软件设计 - 架构设计 - 全程概述](https://img-blog.csdnimg.cn/direct/8bb61a84b2f44a59a408b09402a8bdaf.png)