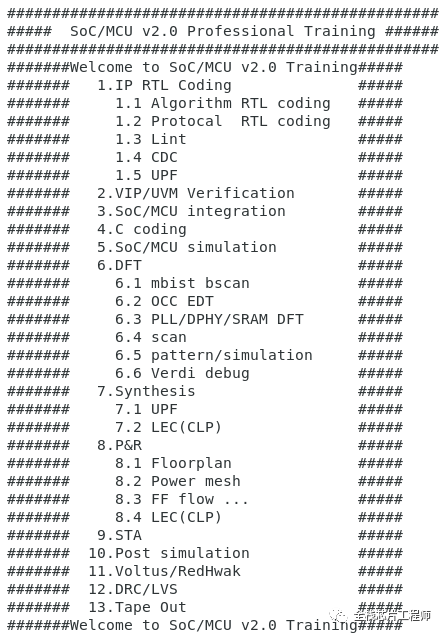

芯片培训(真实项目)介绍:

-

低功耗景芯SoC前端、中端、后端全流程实战培训(火爆订购中)

-

DDR4/3项目实战培训

-

ARM Cortex-A72处理器12nm PR实战培训

-

ARM Cortex-A72处理器12nm DFT实战培训

-

ARM Cortex-A7处理器28nm PR实战培训(火爆价格战)

-

RISC-V MCU 40nm全芯片PR实战培训

-

跨时钟域RTL设计与CDC实战

-

UPF设计与低功耗仿真实战

芯片Design Service设计服务介绍:

-

提供SoC、MCU、ISP、CIS等芯片设计、验证、DFT设计服务

-

提供DDR/PCIE/MIPI/CAN/USB/ETH/QSPI/UART/I2C等IP设计

-

提供7nm、12nm、28nm、40nm、55nm、65nm、90nm等后端设计

-

提供高校、企业定制化芯片设计服务、设计培训业务

景芯SoC芯片全流程设计训练营的宗旨:

【让每个学员都能设计一款SoC/MCU芯片】

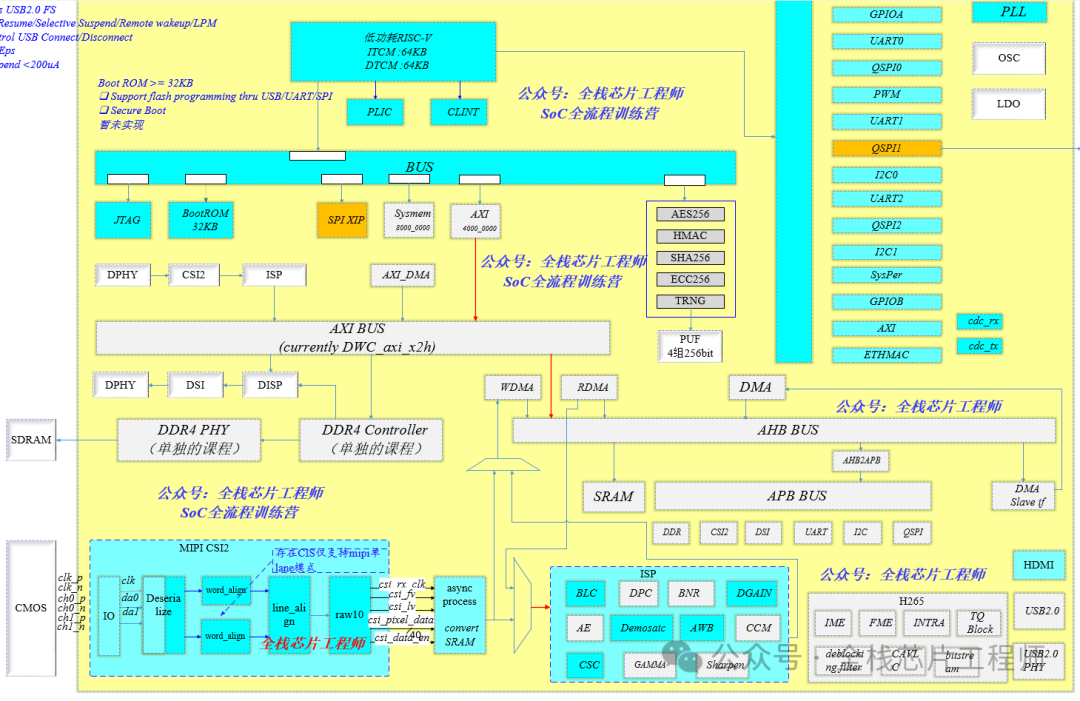

【全网唯一】景芯SoC是一款用于【芯片全流程设计培训】的低功耗ISP图像处理SoC,采用低功耗RISC-V处理器,内置ITCM SRAM、DTCM SRAM,集成包括MIPI、ISP、USB、QSPI、UART、I2C、GPIO、以太网MAC控制器等IP,采用SMIC40工艺设计流片。

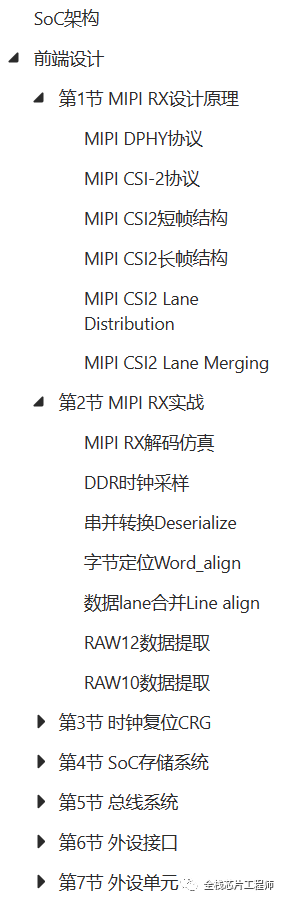

(一)SoC前端课程,您将学会

-

高速接口的Verilog设计实现

-

从图像算法到RTL设计实现

-

MIPI、ISP的Verilog实现与仿真

-

Lint、CDC检查及UVM验证

-

后仿真

仅前端一门课程内容就抵得上其他培训机构的5-6门课程。

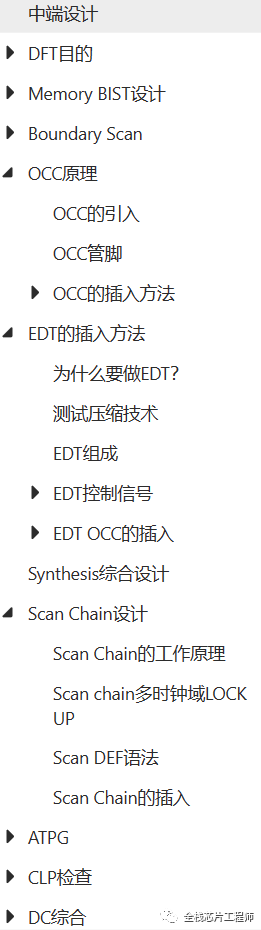

(二)SoC中端课程,您将学会

-

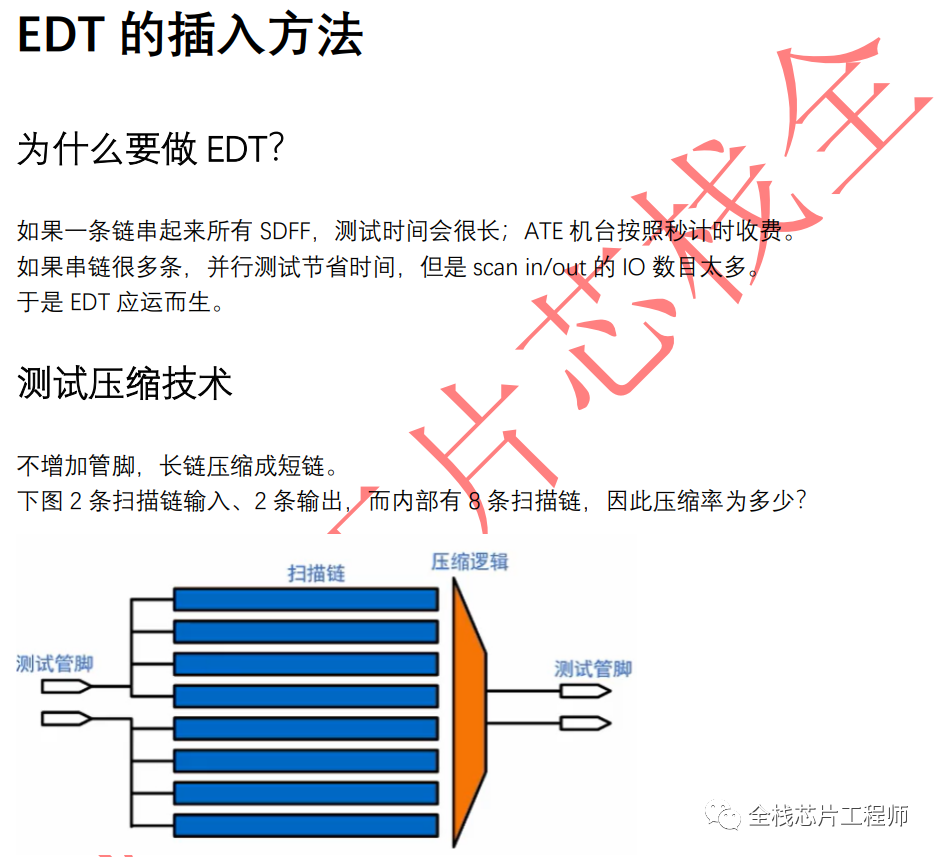

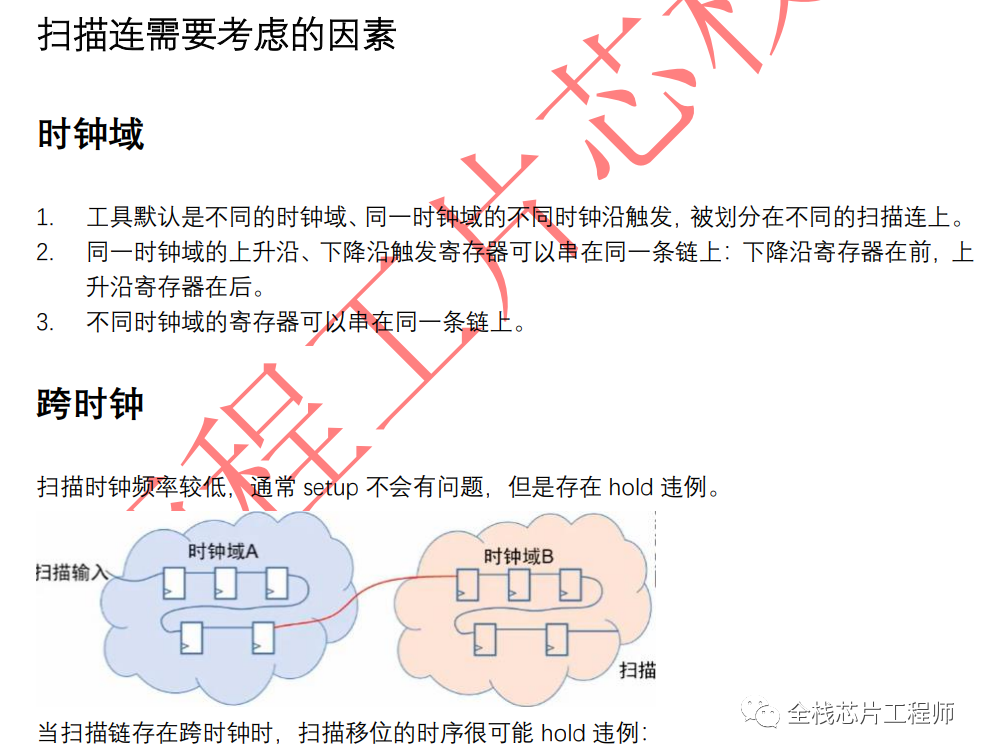

DFT设计(芯片级)

-

Synthesis逻辑综合(芯片级)

-

低功耗UPF设计、CLP技术

-

formal验证等技术

仅中端一门课程内容就抵得上其他培训机构的4-5门课程。

(三)SoC后端课程,您将学会

-

低功耗设计

-

布局布线(低功耗FF flow)

-

StarRC/QRC

-

STA/Tempus

-

功耗分析

-

DRC/LVS设计

仅后端一门课程内容就抵得上其他培训机构的3-4门课程。

加入知识星球,加入芯片设计知识宝库!

SoC培训营的知识星球

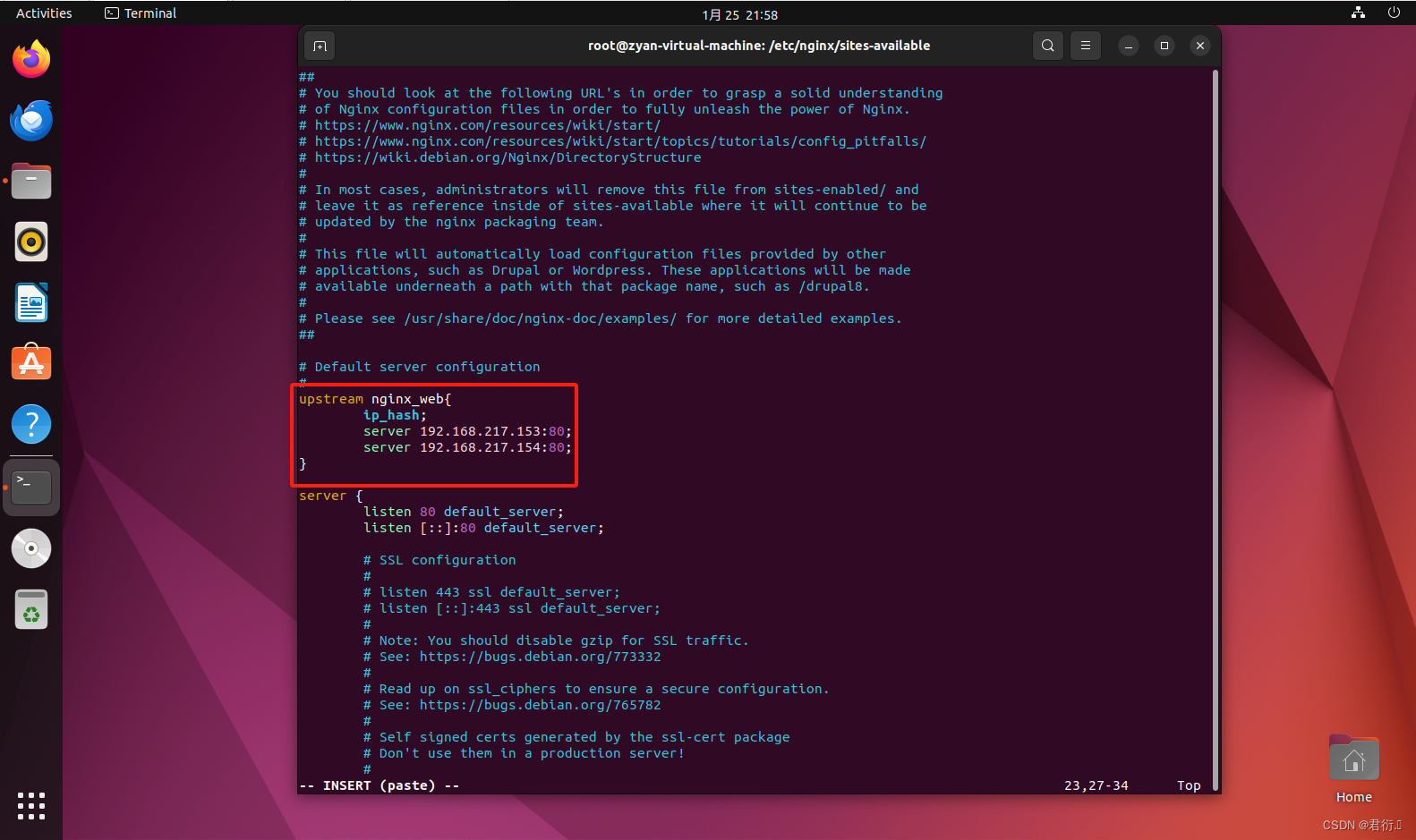

接着上文章芯片跨时钟域设计(一)继续聊。

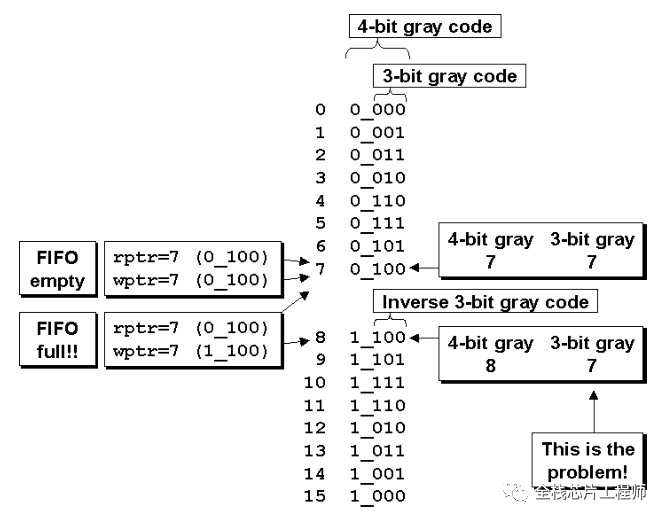

下面接着介绍Gray码转换。格雷码的特点就是任意两个相邻码只有一比特不同。

我们接下来介绍二进制码、格雷码的转换原理、不同代码实现风格比较。

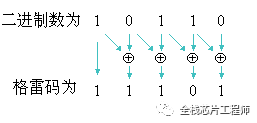

(一)二进制码 -> 格雷码

二进制码的最高位作为格雷码的最高位;二进制码的高位、次高位相异或得到次高位格雷码;格雷码其余位依此类推;

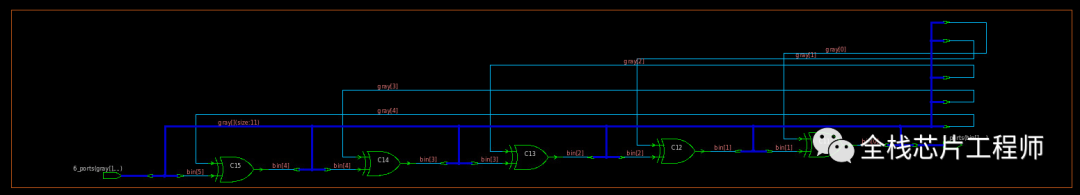

直接上图,简单明了:

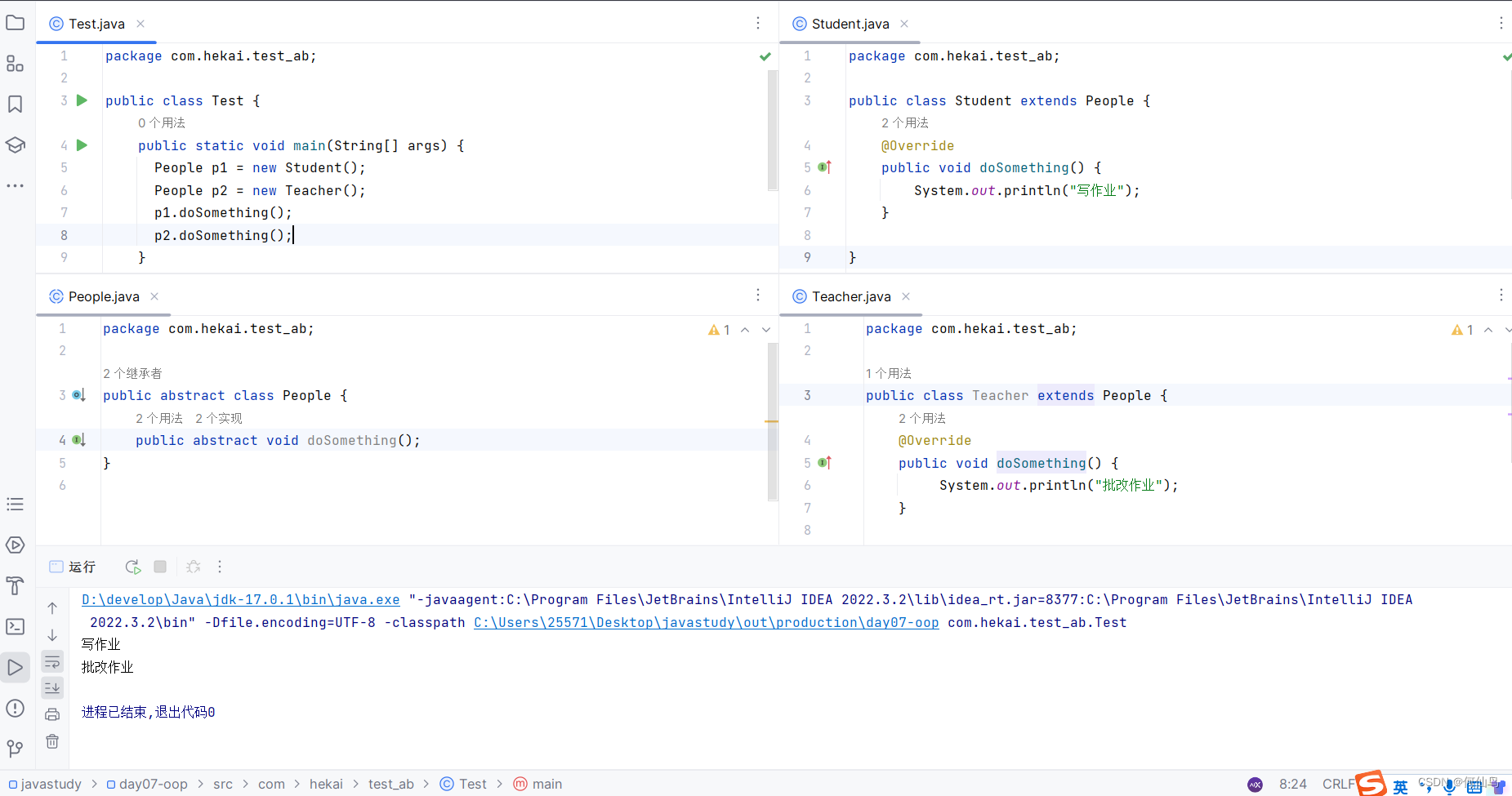

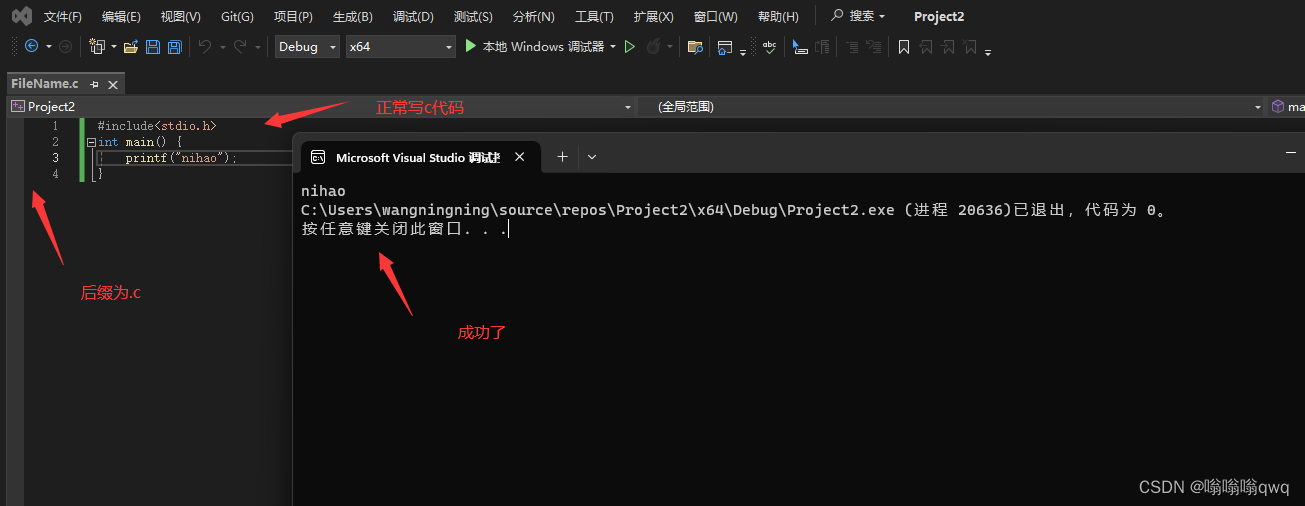

编码风格1://code style 1:

integer i;always @(*)begingray[PTR-1]=bin[PTR-1];for(i=0; i<PTR-1; i=i+1)gray[i]=bin[i]^bin[i+1];end

编码风格2://code style 2:

assign gray = (bin >> 1) ^ bin;两种RTL编码对比:代码推崇:大道至简!

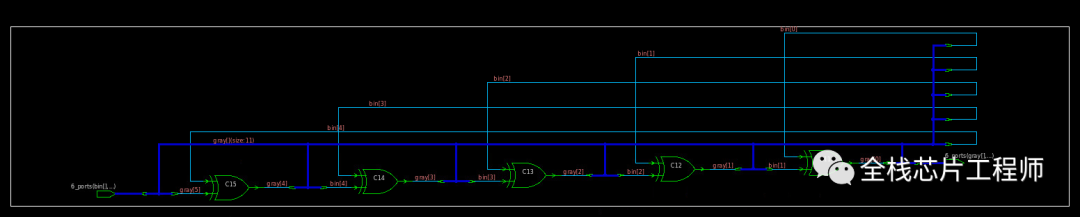

编码风格1:

编码风格2:

资源对比:其实一样,都5个异或门;

时序对比:关键路径是多长?有意思的是,可以和下文格雷码转二进制码的关键路径PK下。

(二)格雷码 -> 二进制码

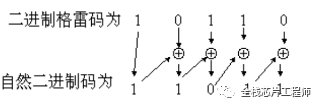

格雷码最高位作为二进制码的最高位,二进制码的高位与格雷码次高位相异或,得到次高位的二进制码,其余位依此类推;

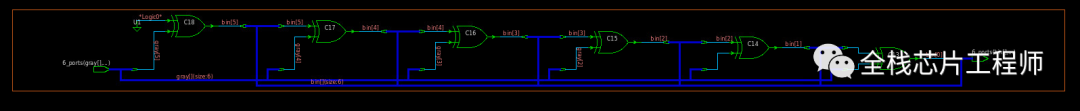

直接上图,简单明了:

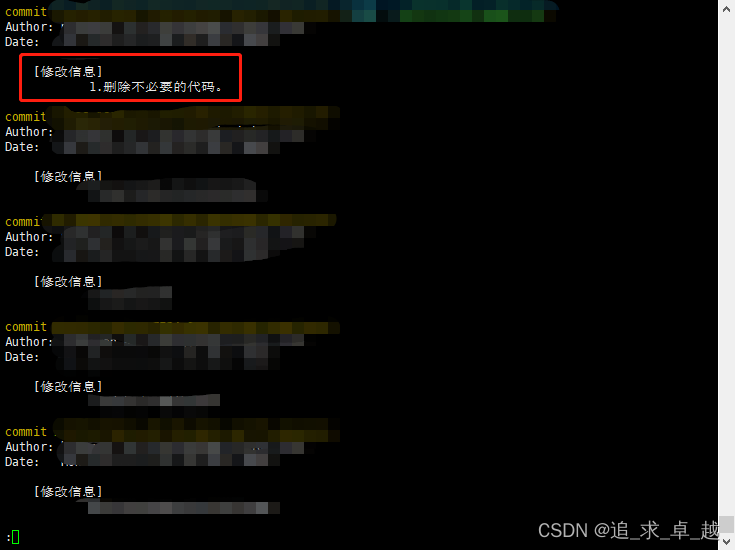

编码风格1://code style 1:

integer i;always @(*)beginbin[PTR-1]= gray[PTR-1];for(i=PTR-2; i>=0; i=i-1)bin[i]=bin[i+1]^gray[i];end

编码风格2://code style 2:

generategenvar i0;for(i0=0; i0<PTR; i0=i0+1)assign bin[i0] = bin[i0+1] ^ gray[i0];endgenerate

代码我们尝试用generate来实现,效果和编码风格1本质是相同的,都是复制硬件电路;

细品一下,就会发现我们省略了下面一行:

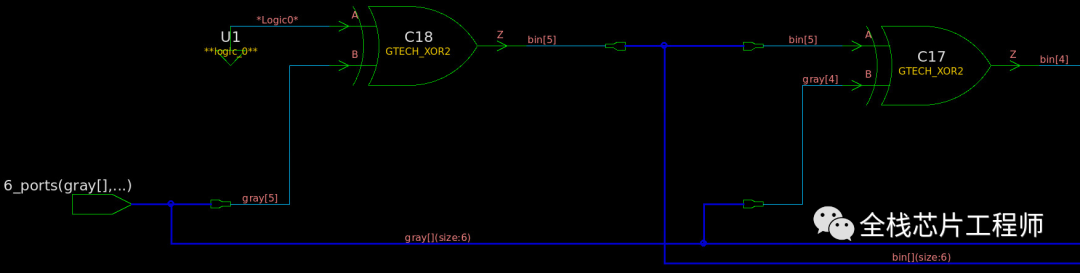

bin[PTR-1]= gray[PTR-1];那么当编码风格2的i0=PTR-1时,不存bin[PTR],代码如何编译呢?

综合电路告诉了我们答案:

两种RTL编码对比:代码推崇:大道至简!不过,值得细品的东西来了。

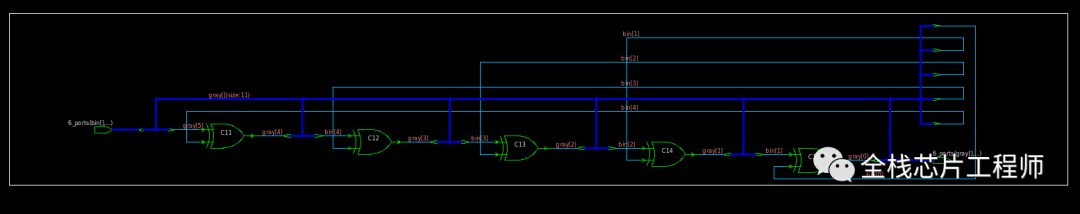

编码风格1:

编码风格2:

资源对比:风格1有5个异或门,风格2有6个异或门;

时序对比:细品!两种电路critical path都是谁?几级combo path?只有心中有电路,RTL才最优,这就需要经验的积攒和反复打磨了。

今天先介绍到这里,然后SoC课程提供服务器供大家实践!带你从算法、前端、DFT到后端全流程参与SoC项目设计。请联系号主报名!联系微信:135-4139-0811

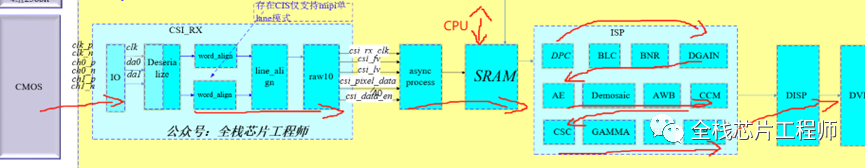

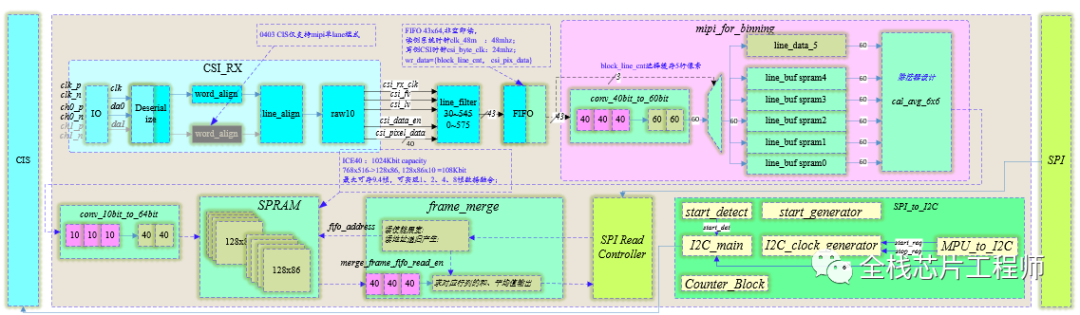

景芯SoC训练营图像处理的数据通路:

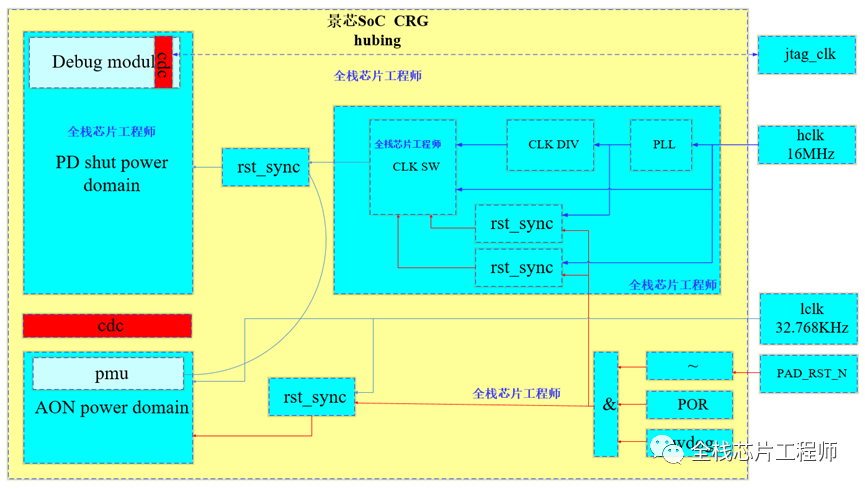

景芯SoC的CRG设计:

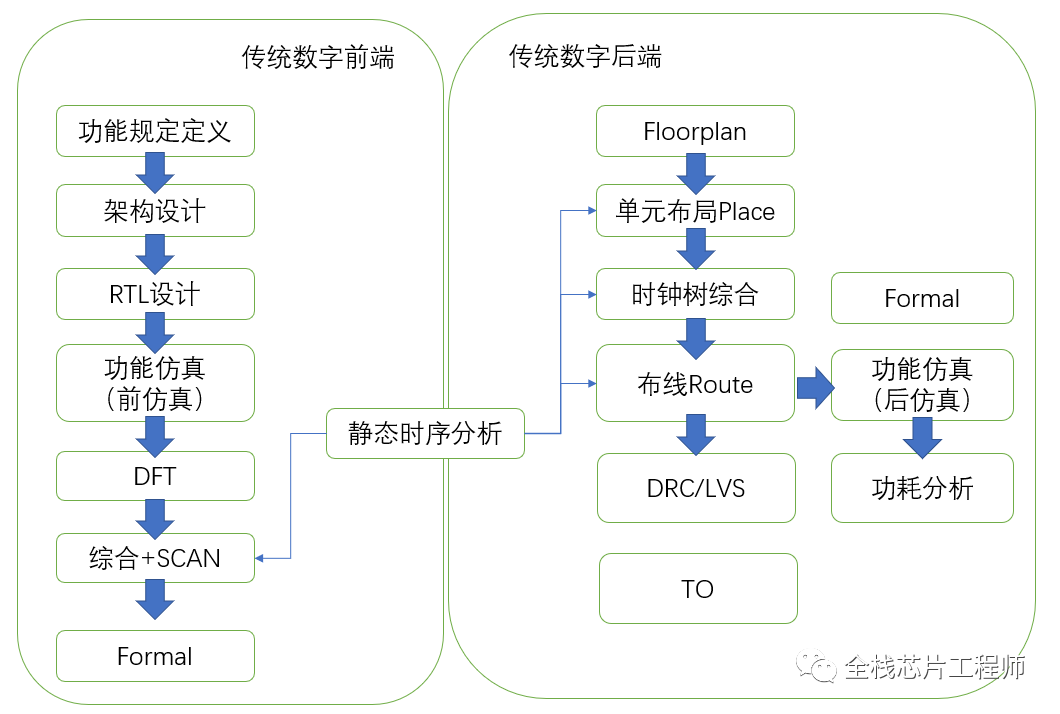

一键式完成C代码编译、仿真、综合、DFT插入、形式验证、布局布线、寄生参数抽取、STA分析、DRC/LVS、后仿真、形式验证、功耗分析等全流程。升级后的芯片设计工程V2.0 flow如下:

SoC一键式执行flow

MIPI DPHY+CSI2解码

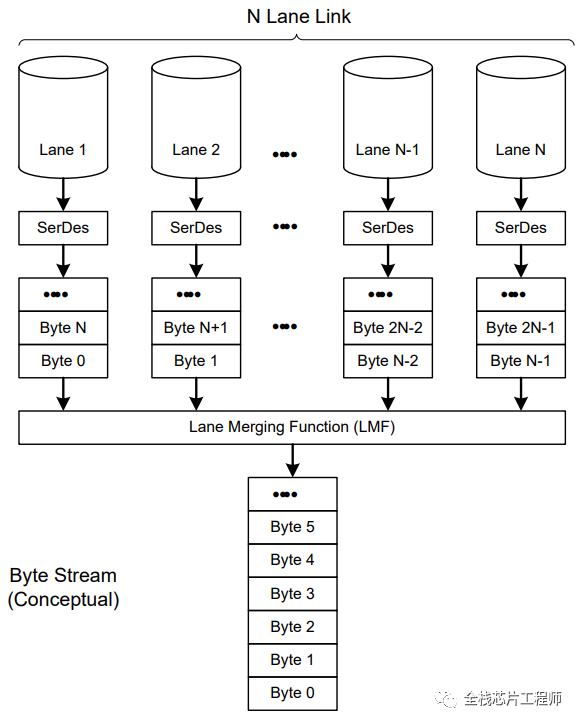

数字电路中经典设计:多条通信数据Lane Merging设计实现

数字电路中经典设计:多条通信数据Lane Distribution实现

UPF低功耗设计

全芯片UPF低功耗设计(含DFT设计)

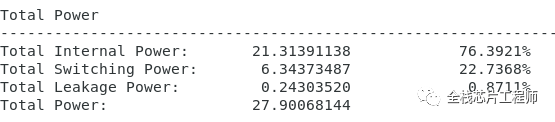

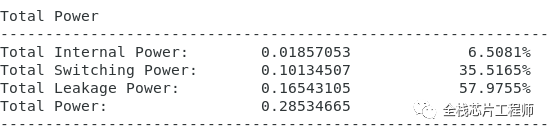

景芯SoC训练营培训项目,低功耗设计前,功耗为27.9mW。

低功耗设计后,功耗为0.285mW,功耗降低98.9%!

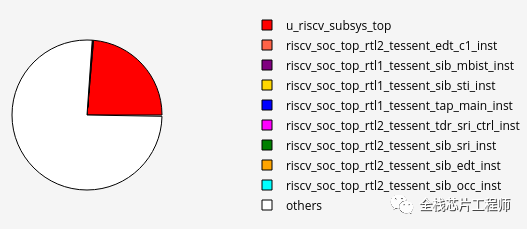

电压降检查:

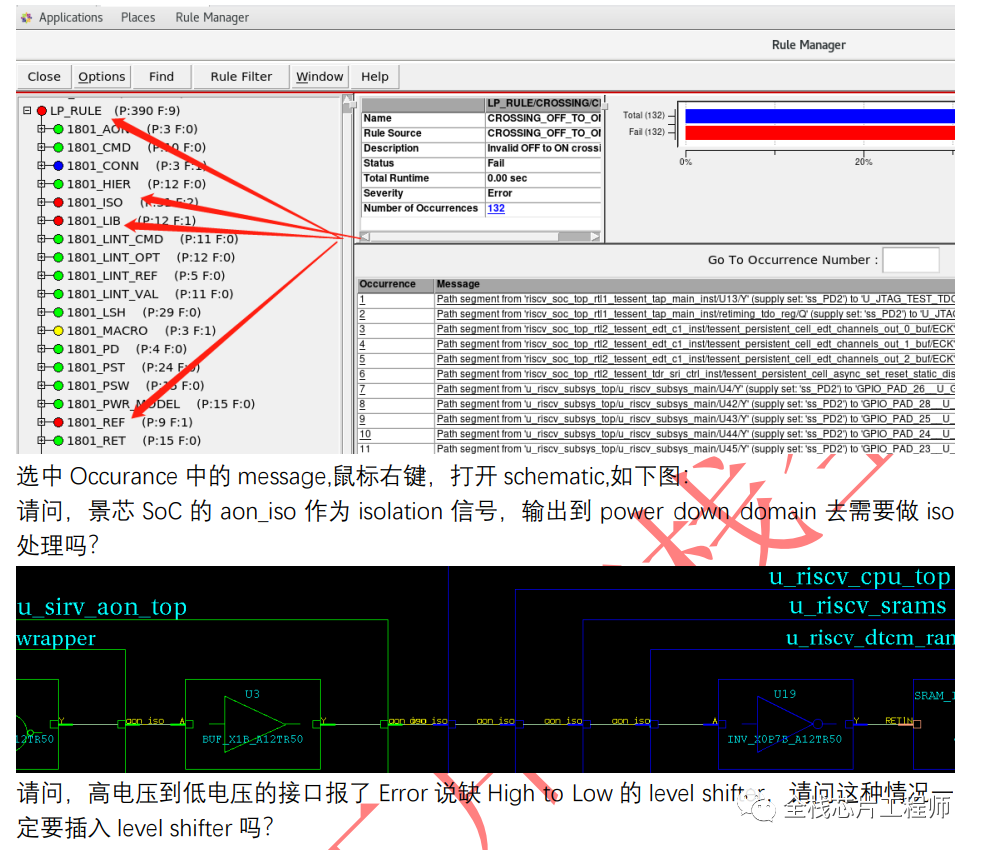

低功耗检查:

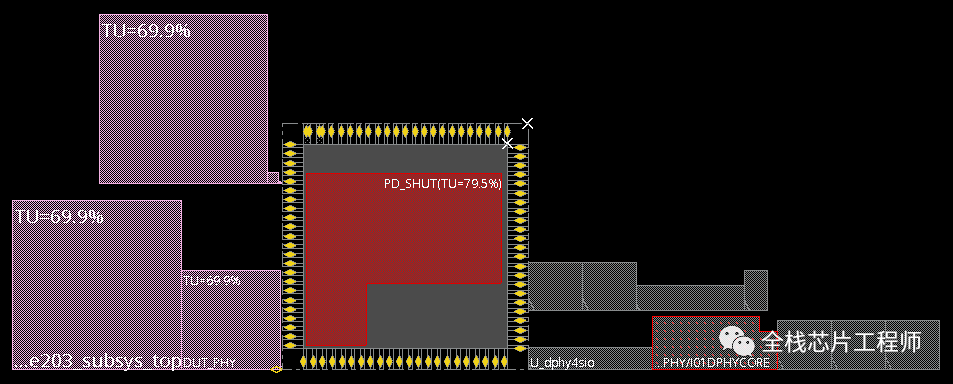

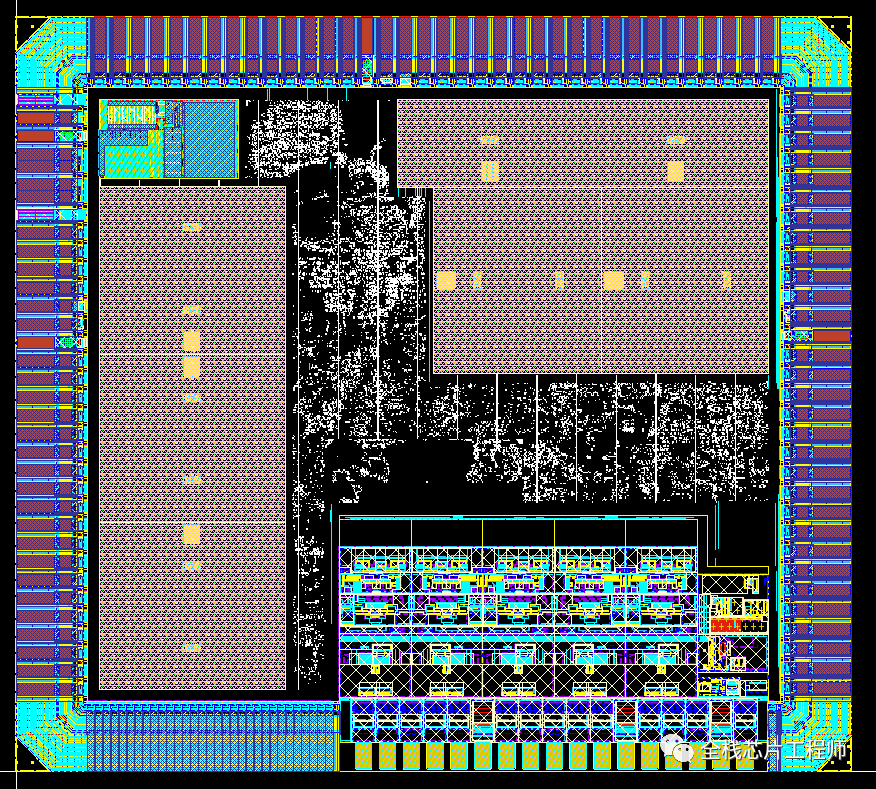

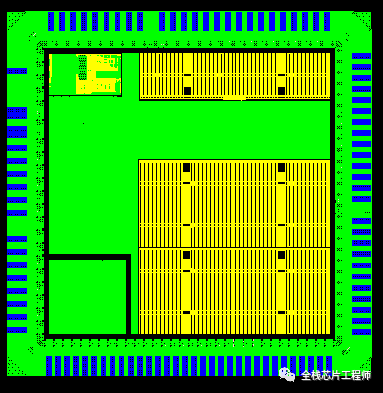

芯片的版图设计V1.0

芯片的版图设计V2.0

低功耗设计的DRC/LVS,芯片顶层的LVS实践价值极高,具有挑战性!业界独一无二的经验分享。

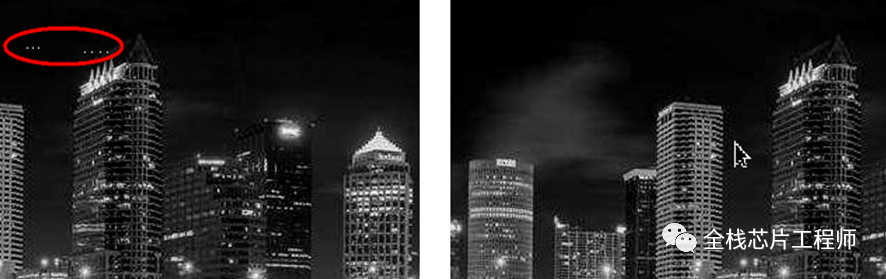

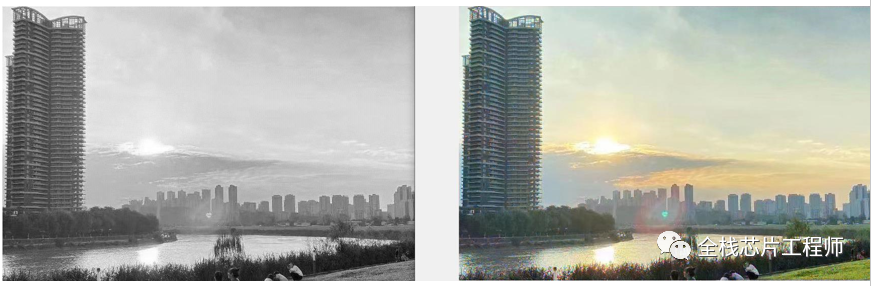

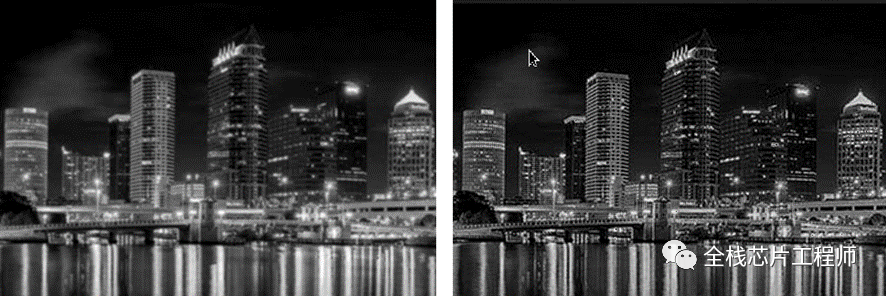

ISP图像处理

-

dpc - 坏点校正

-

blc - 黑电平校正

-

bnr - 拜耳降噪

-

dgain - 数字增益

-

-

demosaic - 去马赛克

-

wb - 白平衡增益

-

ccm - 色彩校正矩阵

-

csc - 色彩空间转换 (基于整数优化的RGB2YUV转换公式)

-

gamma - Gamma校正 (对亮度基于查表的Gamma校正)

-

ee - 边缘增强

-

stat_ae - 自动曝光统计

-

stat_awb - 自动白平衡统计

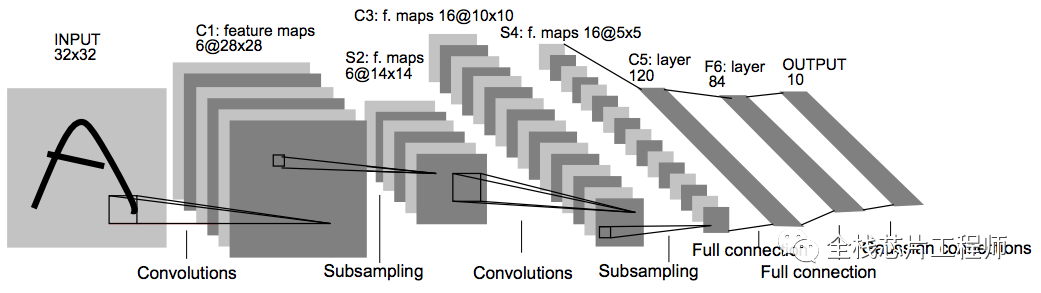

CNN图像识别

支持手写数字的AI识别:

仿真结果:仿真识别上图7、2、1、0、4、1、4、9

景芯微SoC团队业务

景芯微SoC团队业务介绍:

-

提供全网最全流程的实际芯片项目培训

-

提供SoC、MCU、ISP、CIS等芯片设计服务

-

提供芯片设计、验证、DFT设计服务

-

提供后端设计服务,工艺包括7nm、12nm、28nm、40nm、55nm、65nm、90nm、110nm、180nm等,提供投片渠道

-

提供高校、企业定制化芯片设计培训及就业推荐与就业指导

丰富的教程文档

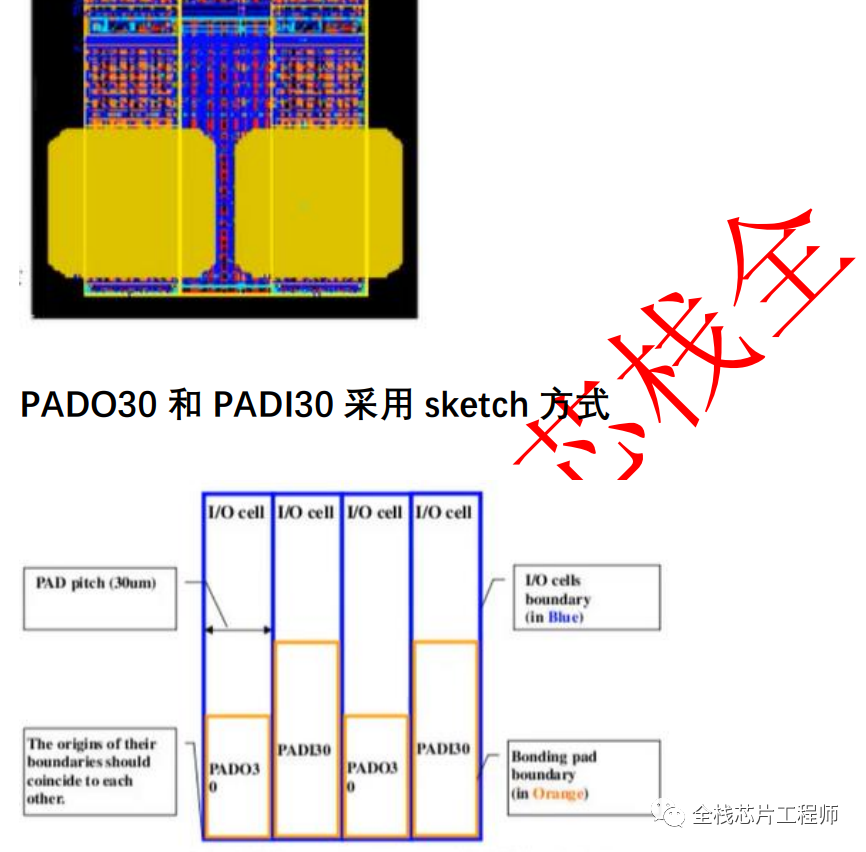

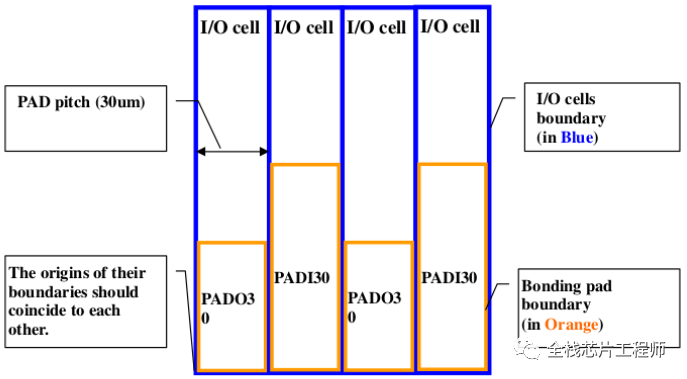

7天冲刺PR训练营有同学问如何给IO添加PAD?请思考景芯SoC的IO和PAD如何实现最佳?

加入知识星球,加入芯片设计知识宝库!

SoC培训营的知识星球

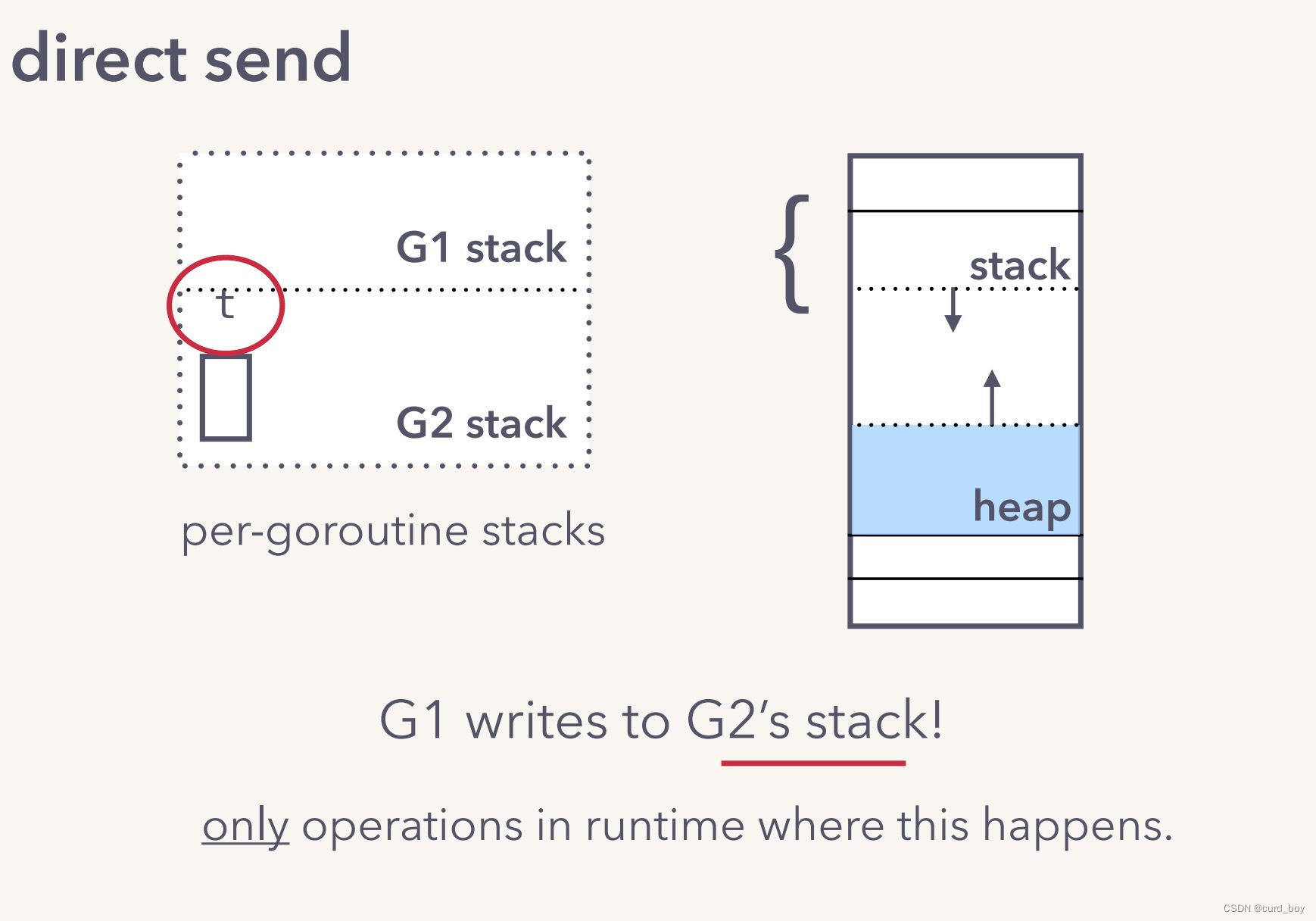

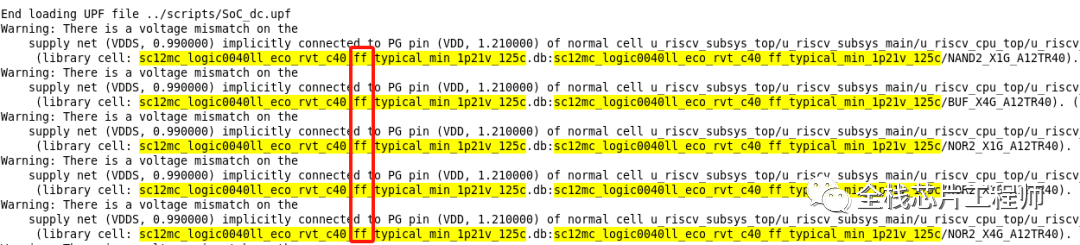

SoC训练营VIP学员问为何低功耗cell没有插入网表?

虽然提问题是值得鼓励的,但是我们在遇到问题时,还是先主动思考,主动解决问题,实在解决不了我们再求助,这样成长更快。

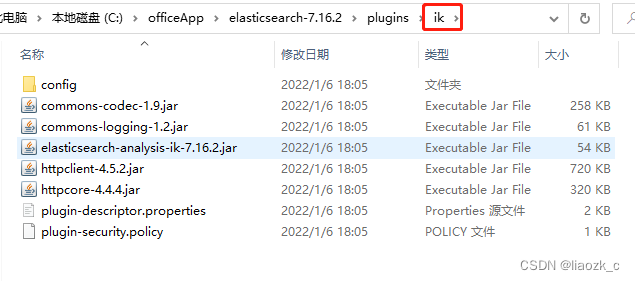

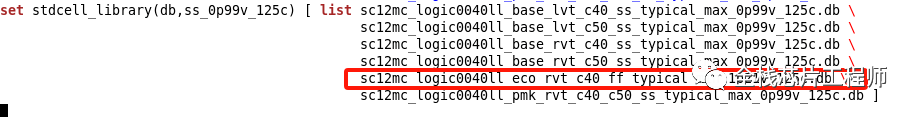

首先,小编拿到这问题,就打开log,查看log是一种IC设计美德!发现EDA工具吃进UPF文件后,报了warning如下,用到了很多ff库。

上图报错UPF指定电压是0.99V,而CELL是1.20V,电压不匹配,导致逻辑综合出来的网表没有插入MV CELL。注意,综合时,我们用的ss库,怎么会是ff库呢?打开约束脚本发现如下bug:

于是,更改约束,将ff换成ss即可。再次run一下,结果就出来了:

低功耗设计部分,设计里面我会留一点小bug在里面 非常简单,我不会公布答案,大家一定要多思考、多动手跑跑,这样才学的深刻。

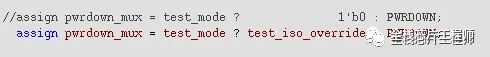

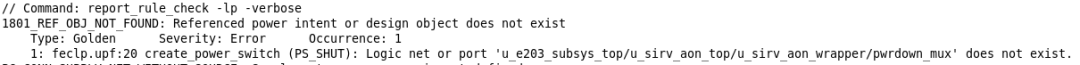

培训学员请注意,景芯SoC用always on的power domain电压域的pwrdown_mux信号作为power switch cell的switch控制信号,但是设计里面有个小问题,不太算bug的bug,但对upf低功耗flow而言,毫无疑问就是bug!

培训学员请登陆服务器追踪一下pwrdown信号,注意其负载情况,RTL代码如下:

结合PR输出的netlist, 我们做个clp低功耗检查,脚本参见服务器。可以发现,clp报错说power switch的switch控制信号找不到。

不得不说,clp检查对低功耗而言多么重要,对芯片设计而言多重要!景芯SoC的价值就在把芯片设计全流程的这些细小的知识点,全部串接起来!犹豫啥?抓紧报名加入吧!

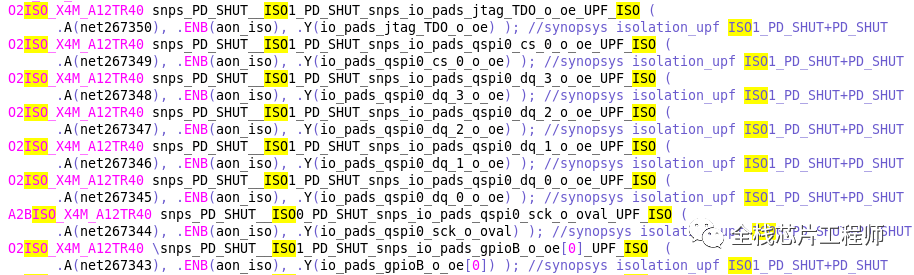

在芯片设计中端流程时,景芯SoC会插入UPF约束中的isolation等cell,但是无法插入power switch等cell,因此,作为power switch cell的控制信号pwrdown_mux在没有负载的情况下,会被裁员掉(优化掉),因此需要设置上面MUX器件为dont_touch或者使pwrdown_mux成为module的port并禁止auto_ungroup(并设置no_boundary_optimization),这样这个信号才能保留给后端,供后端实现power switch控制。请学员完成代码修改,基于全套flow环境完成如下任务:

-

lint检查、前端仿真,

-

完成中端、后端flow,

-

完成clp检查, 完成后仿真

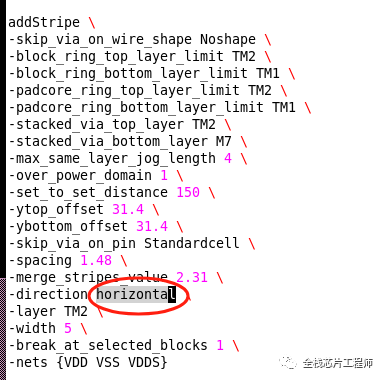

7天冲刺PR训练营有同学问,同样的floorplan,有些同学很快跑完,有些同学则遇到大量DRC问题(EDA工具不停iteration)导致工具始终无法跑完,具体什么问题呢?

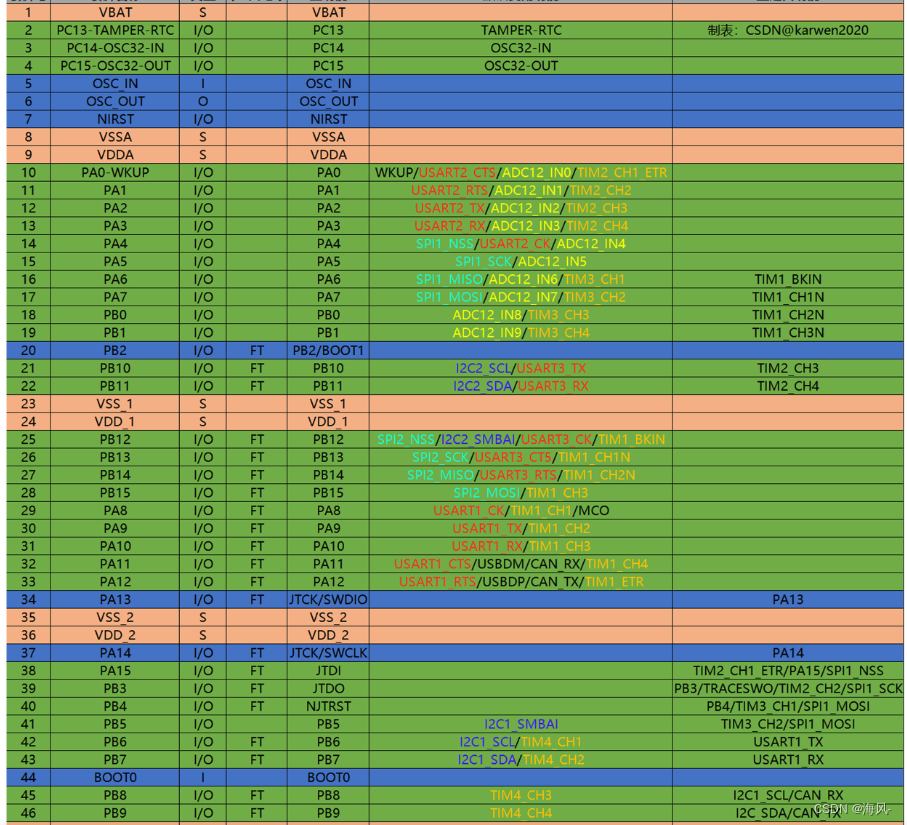

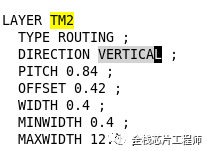

首先,小编发现该同学的stripe把TM2定义为了horizontal,而熟悉景芯工艺的同学知道,TM2的preference direction是VERTICAL。

查询景芯的lef库文件也可以确认:

用错方向有多大影响呢?大家上景芯SoC的后端flow实践一下吧,实践出真知。

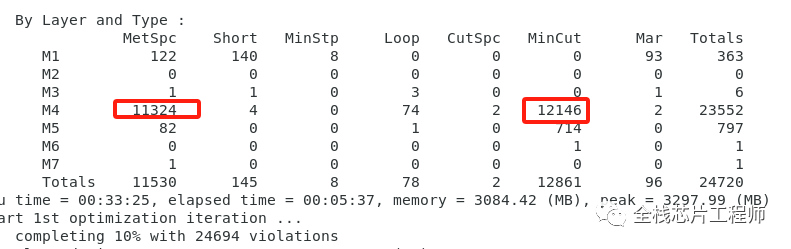

7天冲刺PR训练营有同学问,为啥PR花了一天一夜24个小时完成布线还大量DRC错误?小编已经将设计规模尽可能减小以加速PR设计,实际上2小时就可以跑完routing,为何这么慢?原因就是低功耗单元的走线。具体原因及解决办法欢迎加入景芯训练营讨论。

其错误主要集中在M4上,请思考如何解决。

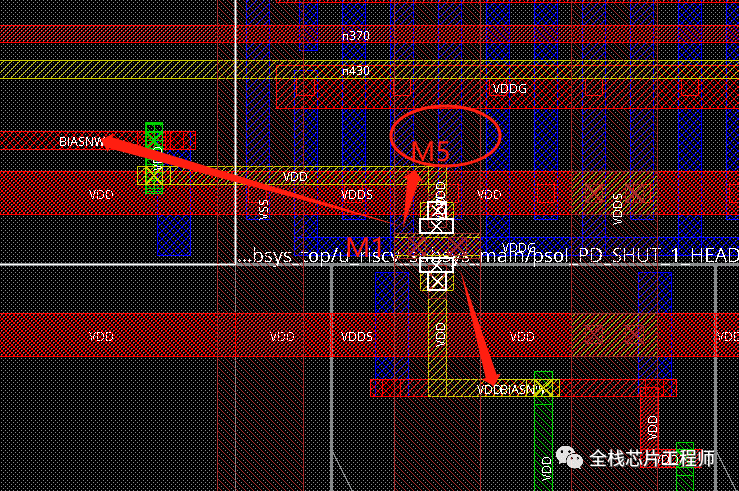

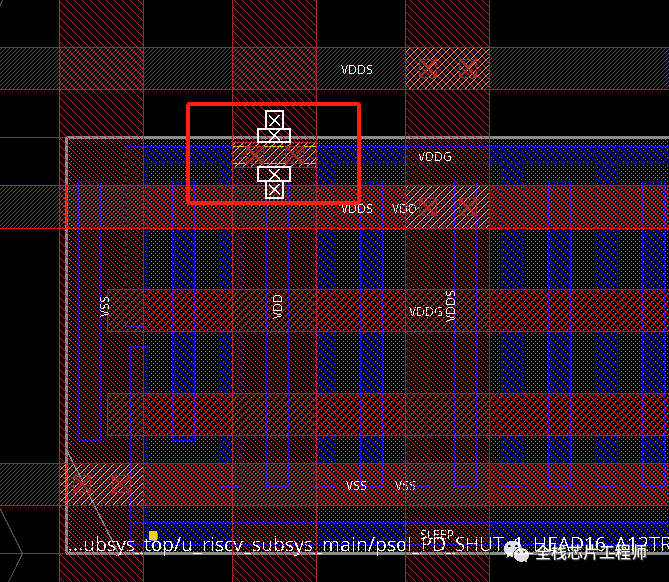

7天冲刺PR训练营有同学问,power switch cell的secondPG pin(VDDG)从M1接出的,而不是M2, 请思考有什么问题?如何解决?

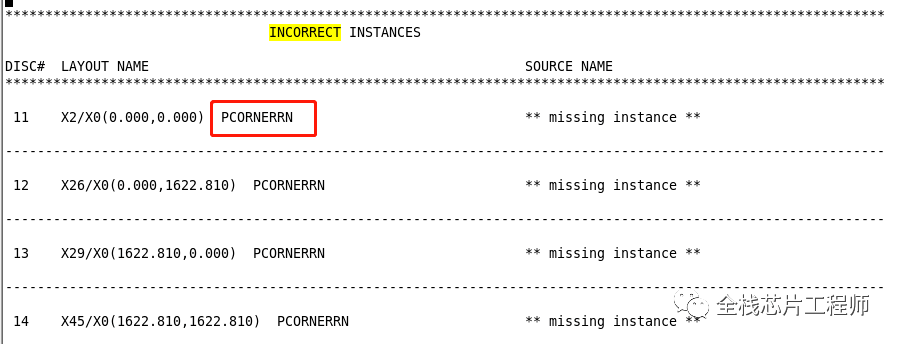

7天冲刺PR训练营有同学问,景芯SoC培训营同学遇到Corner Pad LVS不过怎么处理?

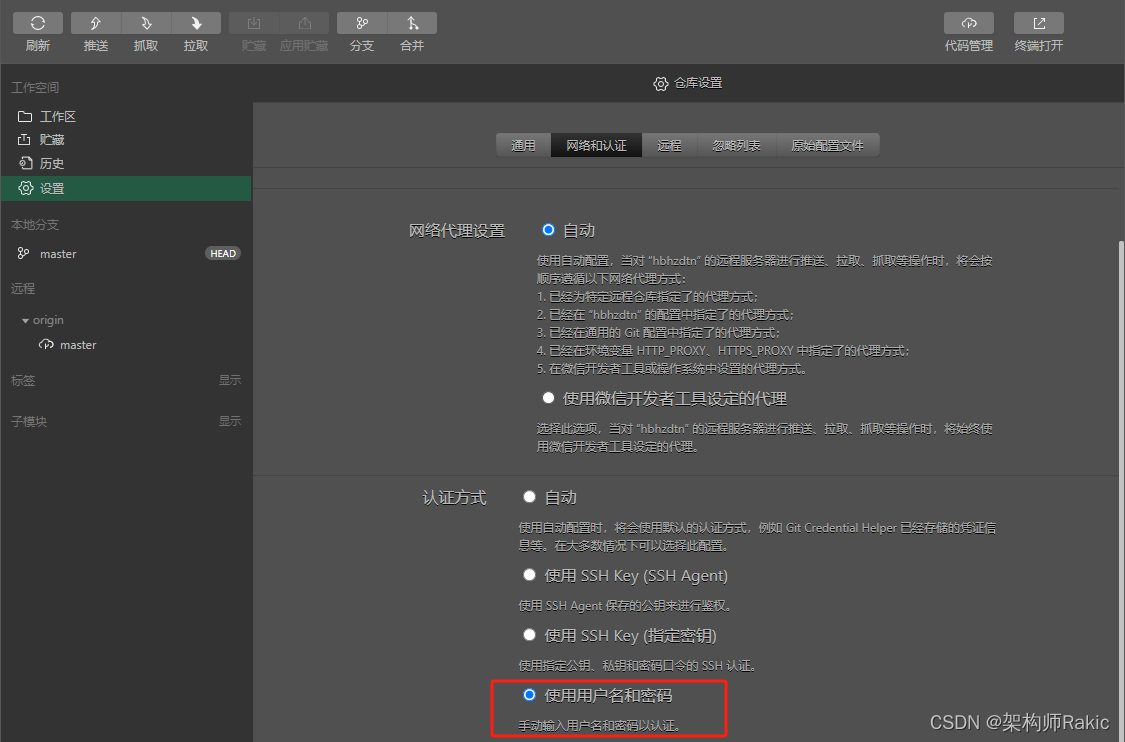

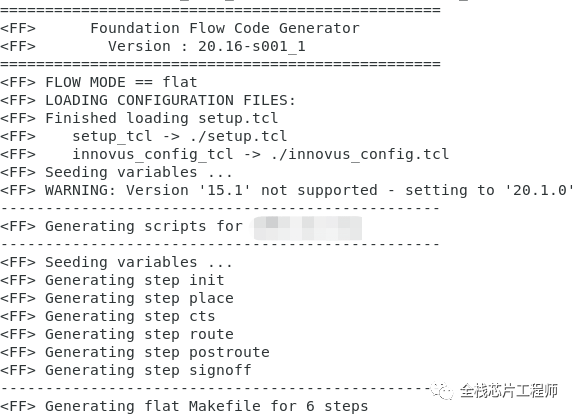

完成景芯SoC培训的前端设计仿真、DFT后,我们来到后端flow,本教程教你一键式跑完数字后端flow。

生成脚本命令如下:

tclsh ./SCRIPTS/gen_flow.tcl -m flat all

生成flow脚本之前需要配置setup.tcl等相关参数,具体参见【全网唯一】【全栈芯片工程师】提供自研的景芯SoC前端工程、DFT工程、后端工程,带你从算法、前端、DFT到后端全流程参与SoC项目设计。

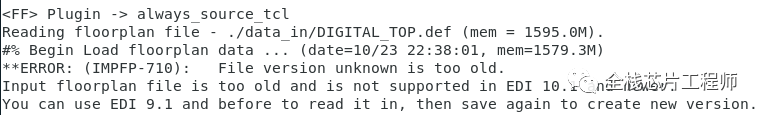

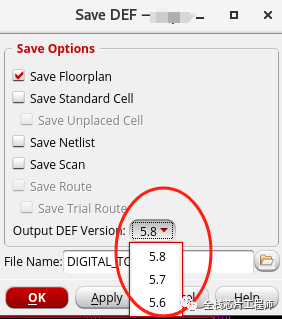

景芯SoC训练营的同学问,为何innovus读取做好的floorplan def文件报Error? 首先看log:

Reading floorplan file - ./data_in/DIGITAL_TOP.def (mem = 1595.0M).

#% Begin Load floorplan data ... (date=10/23 22:38:01, mem=1579.3M)

**ERROR: (IMPFP-710): File version unknown is too old.

以前EDI的时期,我们可以通过定义fp_file的方式来加载floorplan:

set vars(fp_file) "./data_in/DIGITAL_TOP.def"

但是现在innovus升级并放弃了fp_file的加载方式,当然也可以用老版本的EDI9.1及以前版本来加入fp_file,然后转存为新版本,这方式明显没有必要。正如下log提示所说,检查log是非常好的工程师习惯。

Input floorplan file is too old and is not supported in EDI 10.1 and newer.

You can use EDI 9.1 and before to read it in, then save again to create new version.

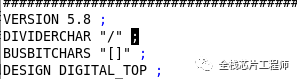

小编的直觉告诉我,先去看看同学保存的def文件是哪个def版本?

同学保存方式如下:

那么请问如何解决?请大家加入景芯训练营实践。

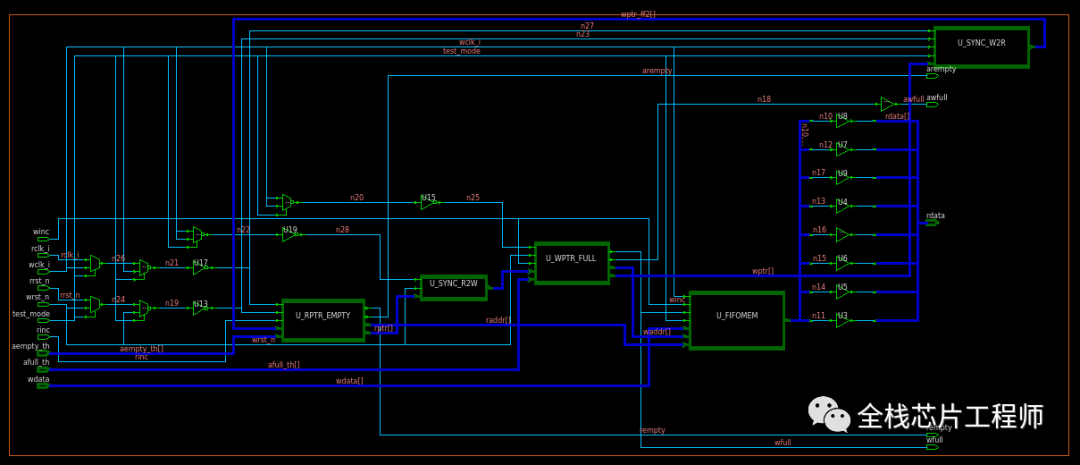

景芯SoC用了很多异步FIFO,关注异步RTL实现的同学,可以抓取异步FIFO出来看一下版图连线:

查看下所有异步FIFO cell的面积;

dbget [dbget top.insts.pstatus unplaced -p].area

查下所有异步FIFO的cell的名字:

dbget [dbget top.insts.pstatus unplaced -p].name

那么怎么抓出异步路径来观察版图走线呢?如何让report_timing呢?更多内容参见知识星球和SoC训练营。

前端设计目录

中端设计目录

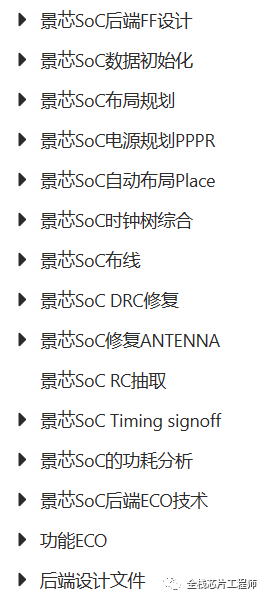

后端设计目录

欢迎加入【全栈芯片工程师】知识星球交流技术,从算法、前端、DFT到后端的全流程设计交流。点击下方图片,加入知识星球!

欢迎加入SoC MCU全流程设计交流群,先加我微信,验证岗位后进群!

SoC MCU全流程设计交流群4

SoC MCU全流程设计交流群3

SoC MCU全流程设计交流群2

SoC MCU全流程设计交流群1

欢迎加入CMOS图像传感器+ISP交流群,先加我微信,验证岗位后进群!

CMOS图像传感器+ISP交流群2

CMOS图像传感器+ISP交流群1