这部分是笔者对基本定时器的理论知识进行学习与总结!,主要记录自己在学习过程中遇到的重难点,其他一些基础点就一笔带过了!

1. 定时器概述

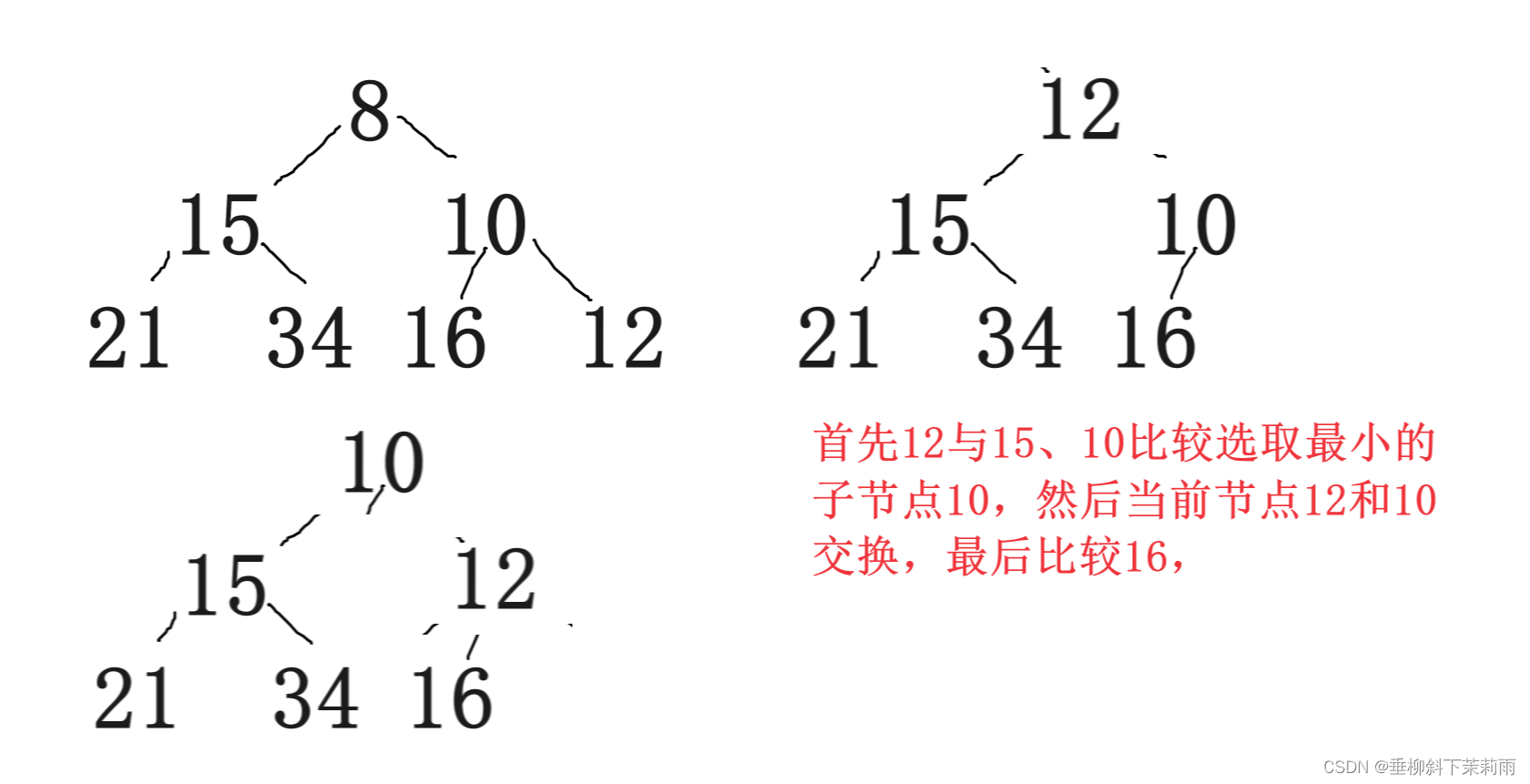

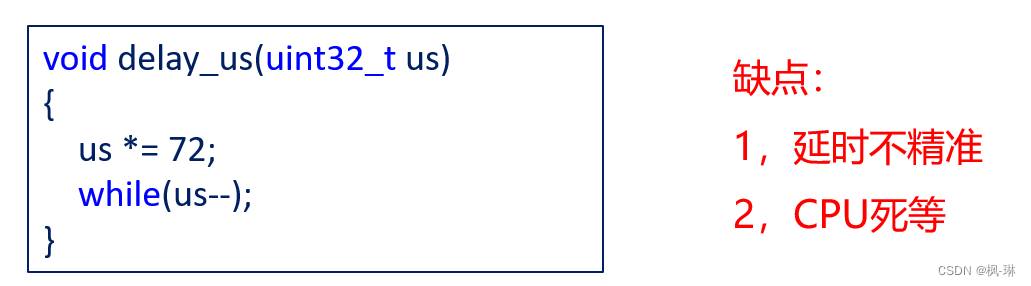

1.1 软件定时原理

使用纯软件(CPU死等)的方式实现定时(延时)功能。

比如想要延时1s,那么CPU就卡在延时函数里1s,什么事情都不能干,就会大大占用CPU资源。

软件定时不精准的原因:

1.函数调用有一个压栈和出栈的过程,压栈和出栈也需要消耗时间。

2.stm32是arm架构,有三级流水线,( 流水线可以在一个时钟周期内同时处理多个指令的不同阶段,降低了单个指令的执行时间。),所以指令执行的时间是不确定的。

因为有压栈出栈的不确定,以及流水线指令执行时间的不确定,导致软件编写的函数是一个不精准的延时。

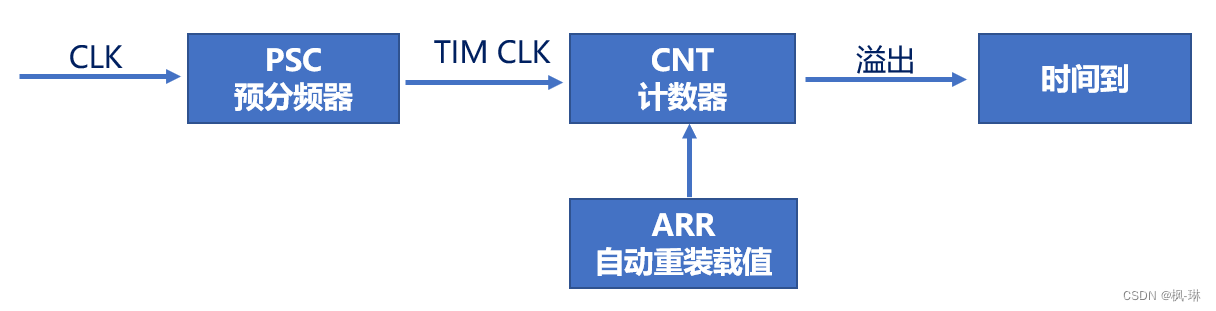

1.2 定时器定时原理

使用精准的时钟源,通过硬件的方式,实现定时功能;定时器核心就是计数器。

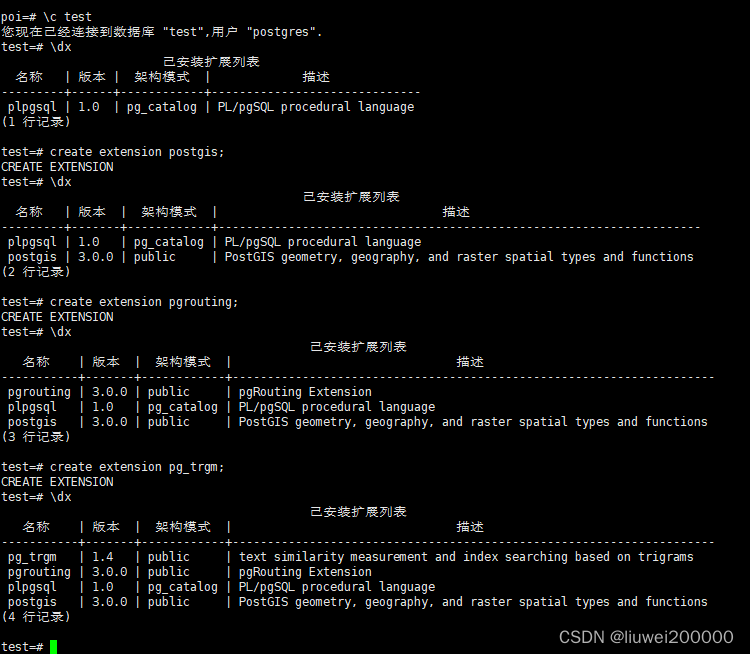

时钟源(CLK)通过预分频器(PSC)分频,得到TIM CLK(定时器工作的时钟频率),每来一个时钟,计数器就计一个数,当计数值到达自动重装载值时产生事件/中断,达到计时的效果。

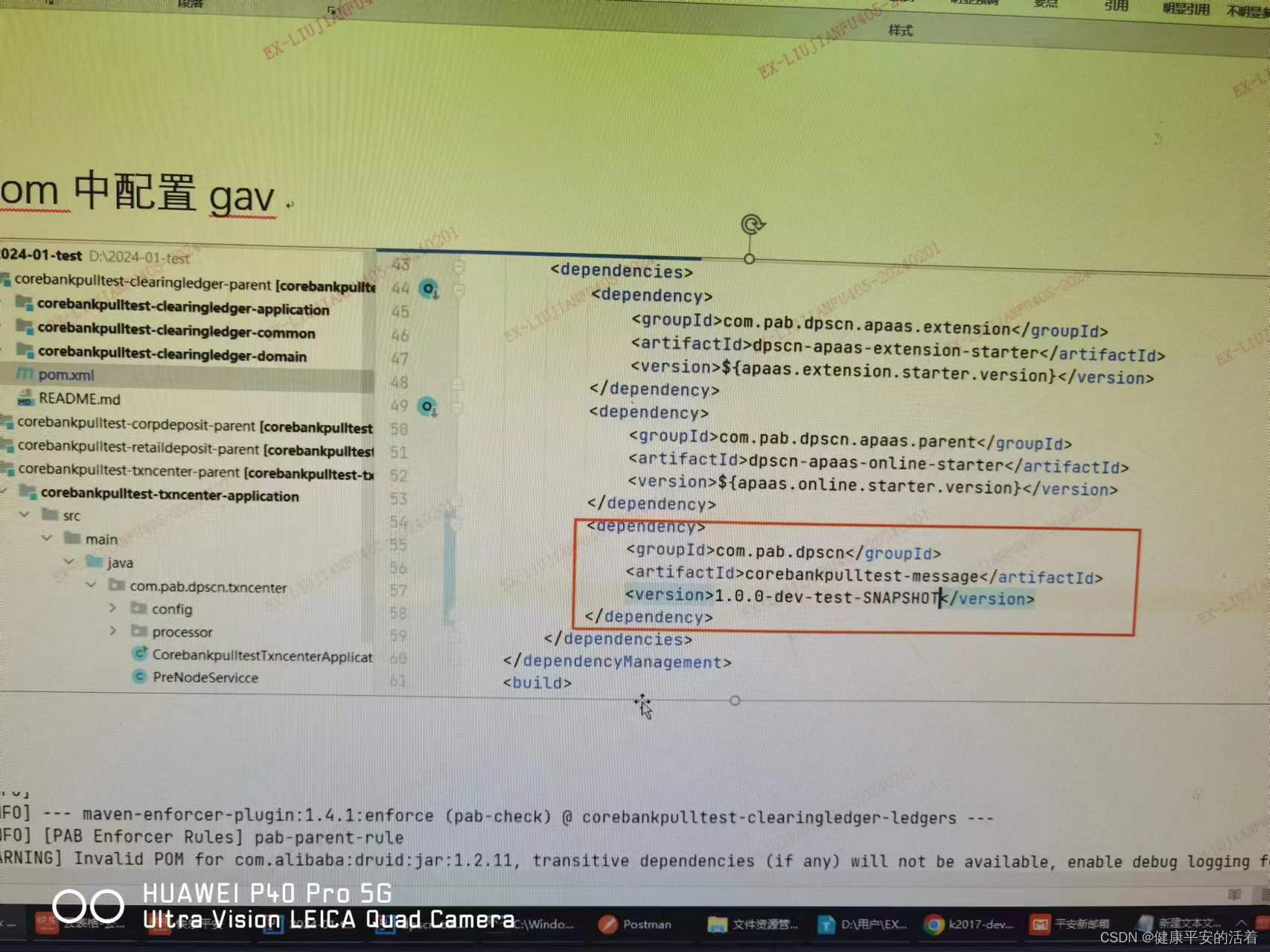

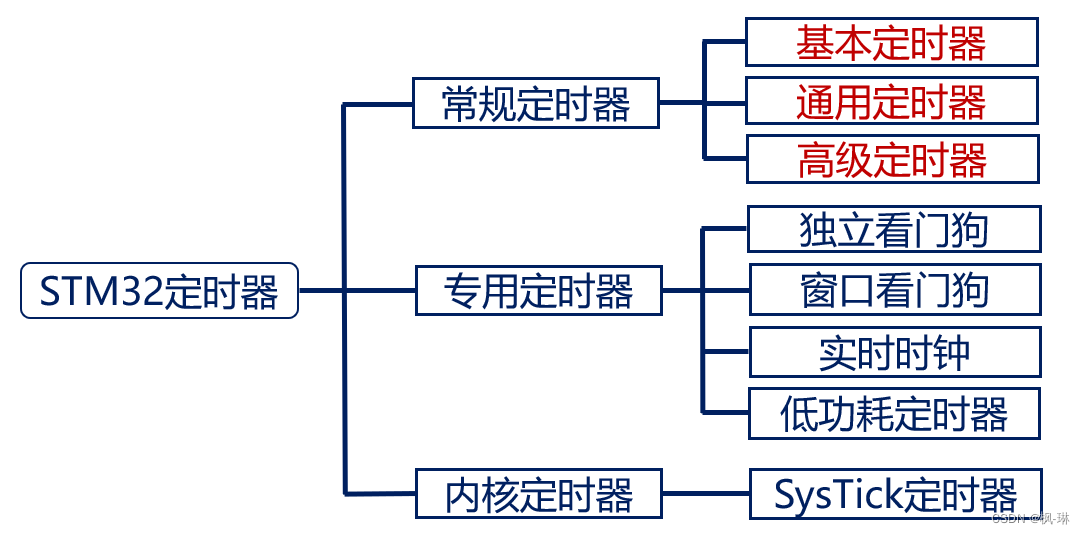

1.3 定时器分类

1.4 定时器特性表

说明:

计数器位数表示定时器可以计数的值,16位可以计数2^16 = 65536个数,计数范围0~65535;

当计数时间到后会产生DMA请求;

1.5 基本、通用、高级定时器的功能整体区别

从基本定时器到通用定时器到高级定时器层层迭代!基本定时器具有的功能通用定时器都有,通用定时器具有的功能高级定时器都有。

2. 基本定时器简介

基本定时器有两个,TIM6和TIM7

主要特性:

16位递增计数器(计数值范围:0~65535),16位预分频器(分频系数:1~65536)

定时器溢出时,会产生触发信号,用于触发DAC,进行数模转换;

在更新事件(计数器溢出)时,会产生中断/DMA请求。

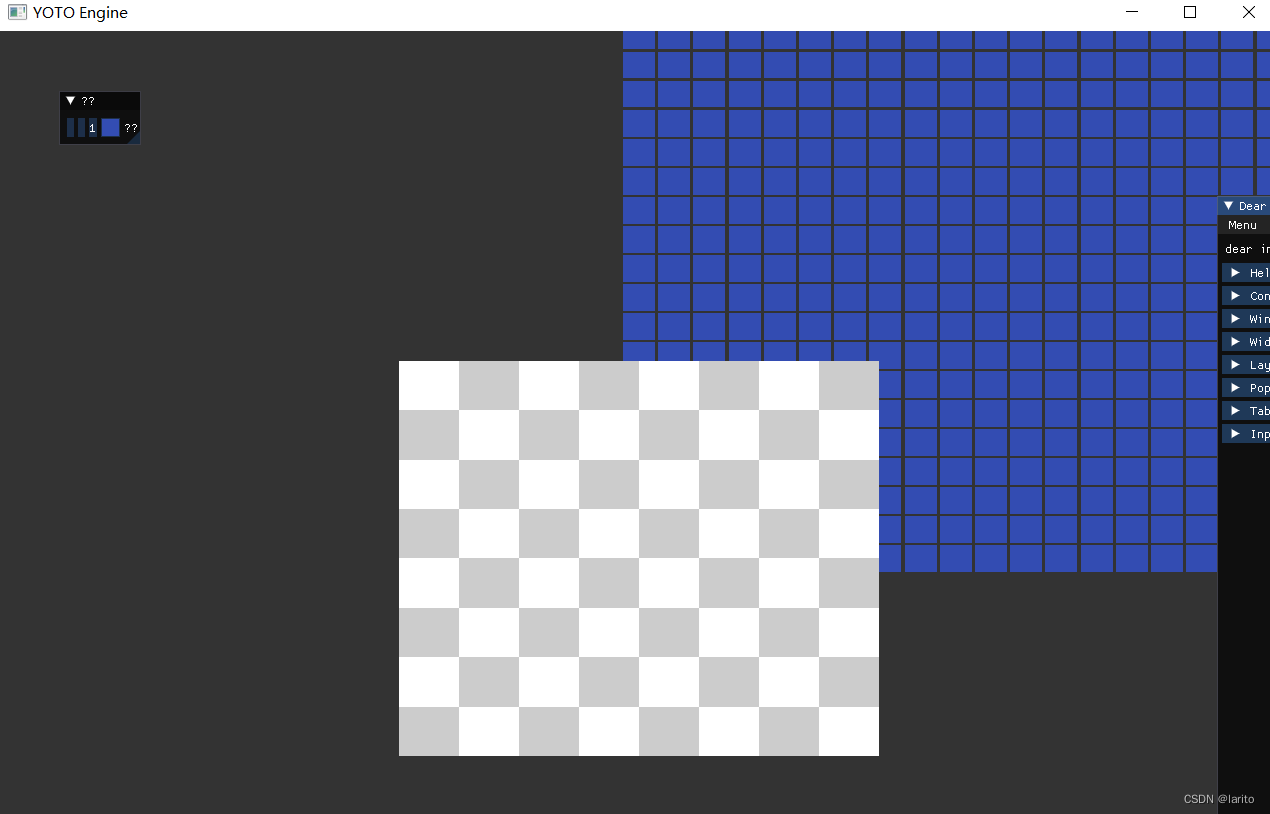

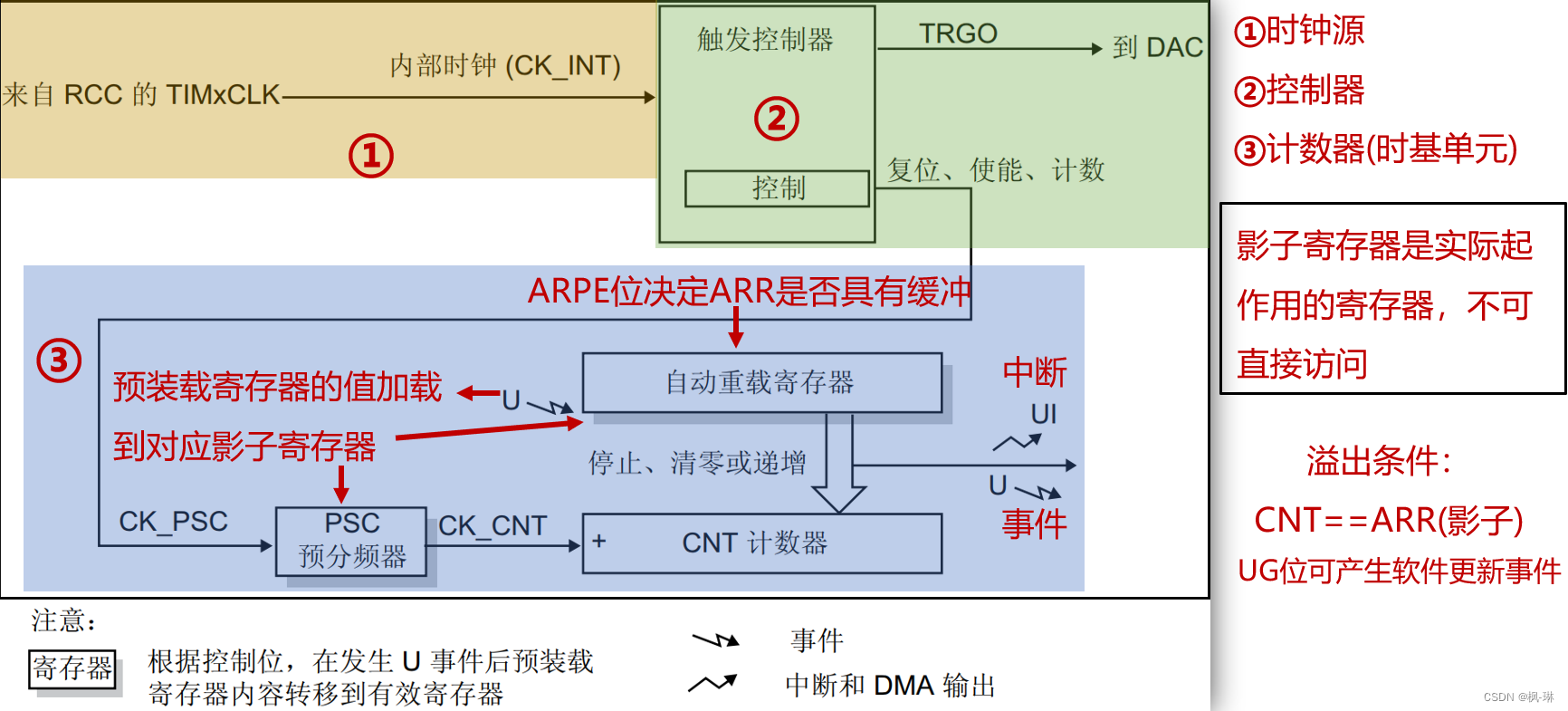

3. 基本定时器框图

流程框图分析:首先时钟源经过控制器来到预分频器PSC里,经过分频之后得到计数器的真正工作频率CK_CNT,每来一个时钟则计数器自增1,当计数值等于ARR(影子寄存器)的值时,会产生溢出,即产生事件/中断。

第①部分:定时器时钟TIMxCLK,即内部时钟CK_INT;

第②部分:控制器控制CNT计数器复位、使能、计数;当CNT计数器溢出时触发控制器产生触发输出信号TRGO,触发一次DAC数模转换。

第③部分:

影子寄存器:是实际起作用的寄存器,不能直接访问,而ARPE位决定了ARR是否具有缓冲,当设置为有缓冲时,ARR的预装载寄存器写入某个值,这个值不会立即起作用,必须等到更新事件发生时,才会把ARR的预装载寄存器的值转移到影子寄存器,从而真正起作用生效;而设置无缓冲时,给ARR的预装载寄存器写入某个值,它会立即转移到影子寄存器中,会立即生效。

预装载寄存器实际上起到一个缓冲的作用。

特别说明:

两者区别:计数器溢出时,默认会产生事件,也可以人为设置为不产生事件;而中断和DMA请求是默认不产生,可以人为的配置它产生。

总的来说,当计数器溢出时,事件会默认产生,中断和DMA输出默认不产生。

产生更新事件后,会让预装载寄存器的值加载到对应的影子寄存器当中。预装载寄存器是黑色的那个框框,影子寄存器是灰色的那个矩形。

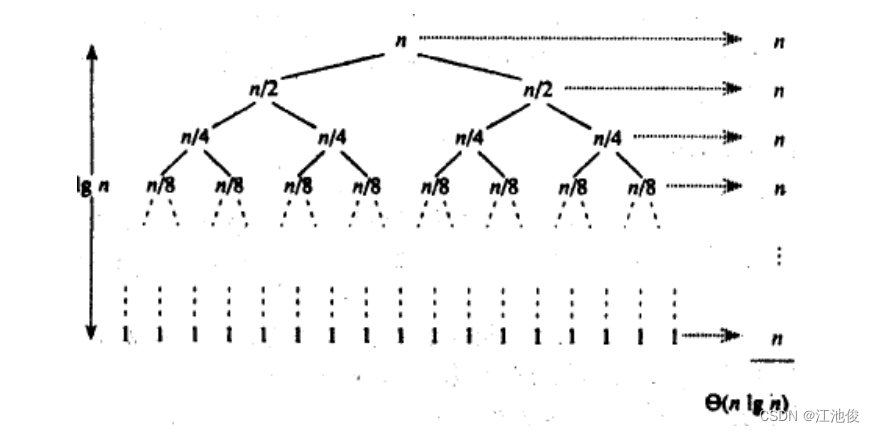

时钟树分析

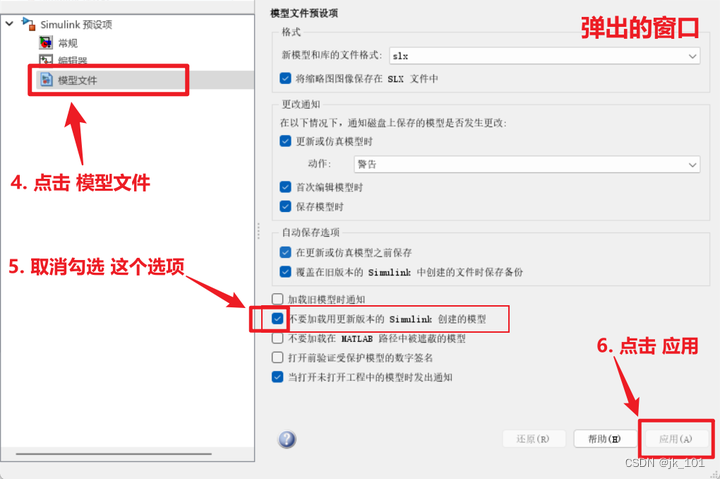

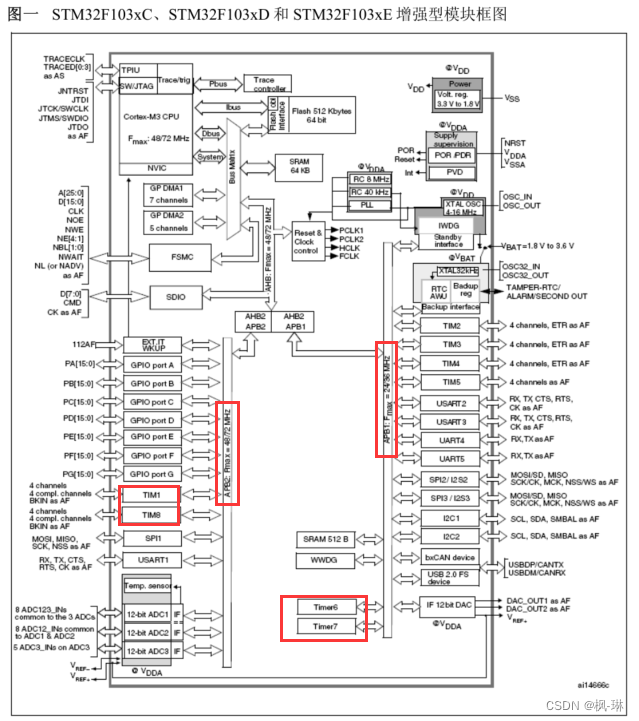

在《STM32F103系列数据手册》 中可以找到该模块框图,由图知,TIM6和TIM7挂载在APB1总线,该总线的最高频率为36M。

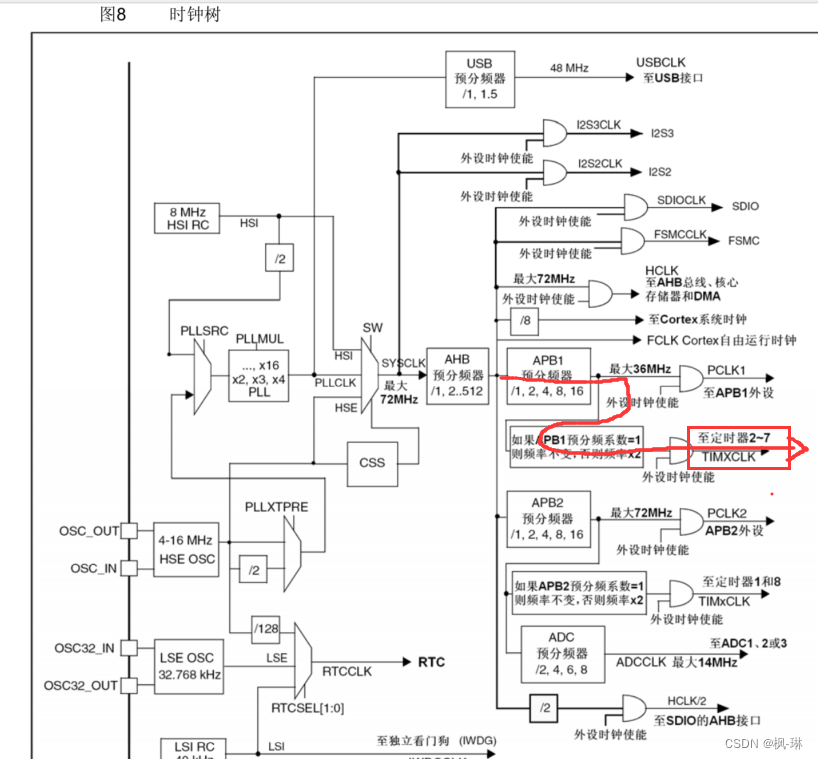

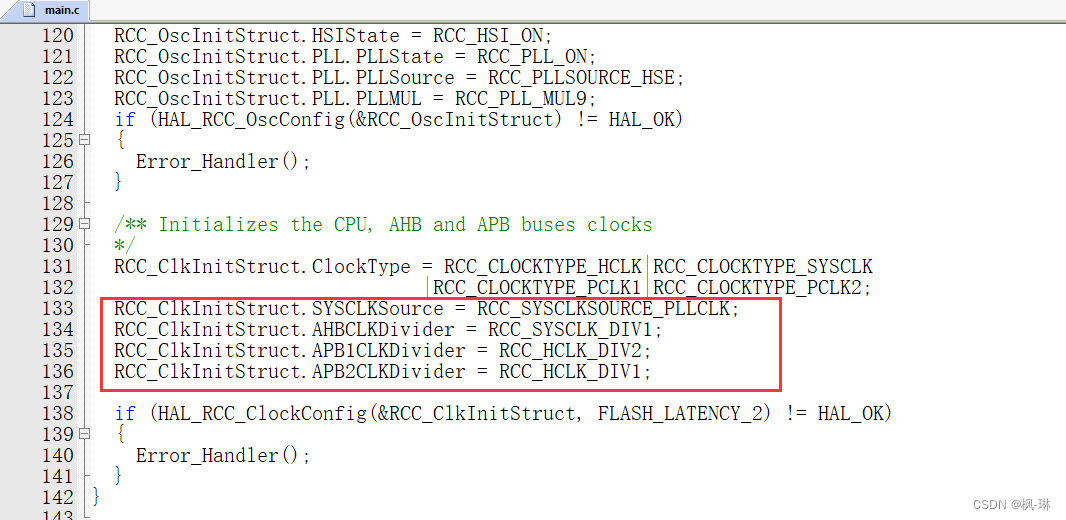

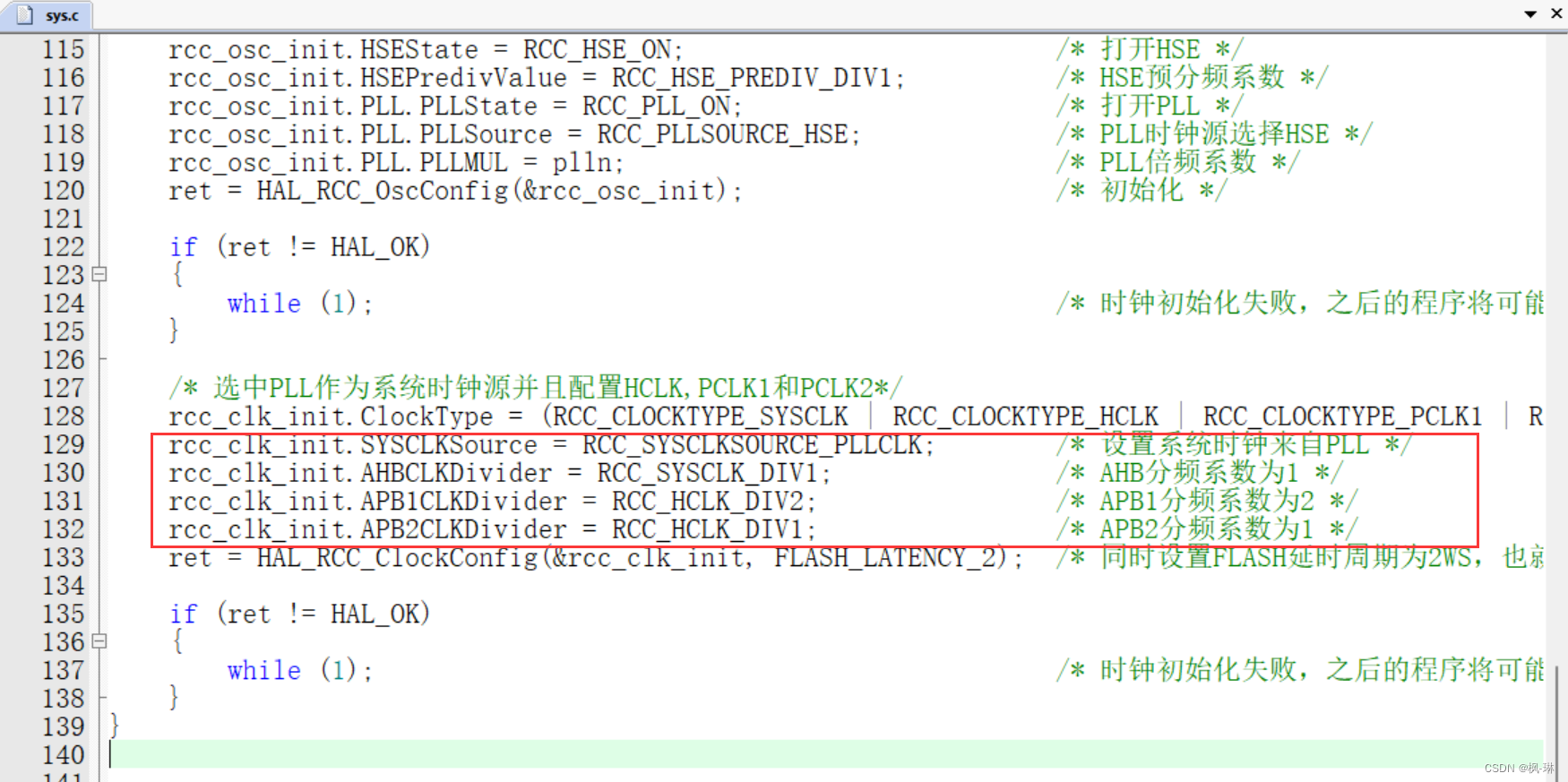

由时钟树得知,想要TIM2~TIM7的时钟频率为72MHz,就要对AHB、APB1进行分频配置,下面两张图分别是通过STM32CubeMX配置的时钟树,以及正点原子官方给的sys.c文件中的时钟树配置,配置效果都是一样,对AHB进行1分频,APB1进行2分频,APB2进行1分频。当SYSCLK为最大72MHz时,AHB进行1分频为72M,APB1进行2分频为36M,因为此时APB1的预分频系数≠1,所以输入到定时器2~7的TIMXCLK为36M*2=72M。

本篇完。

本人博客仅代表个人见解方便记录成长笔记。

若有不足,请指出,感谢您的阅读!