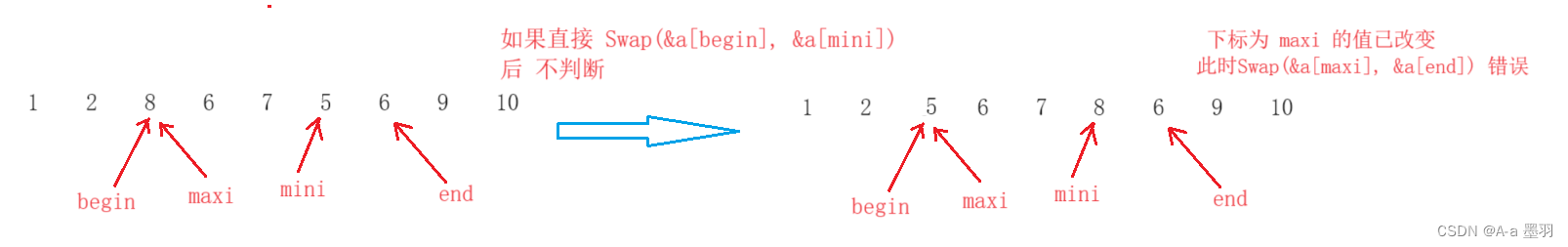

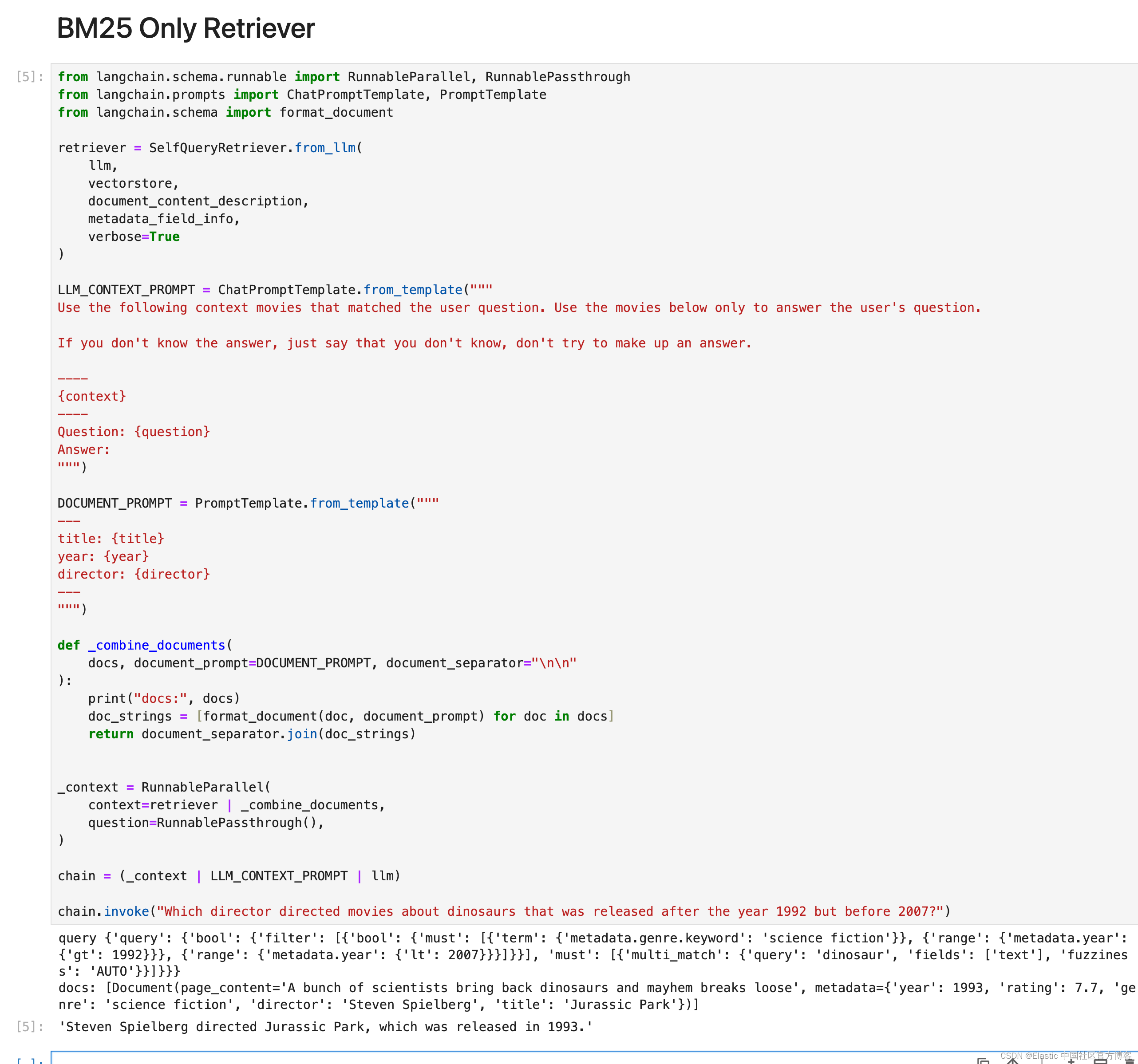

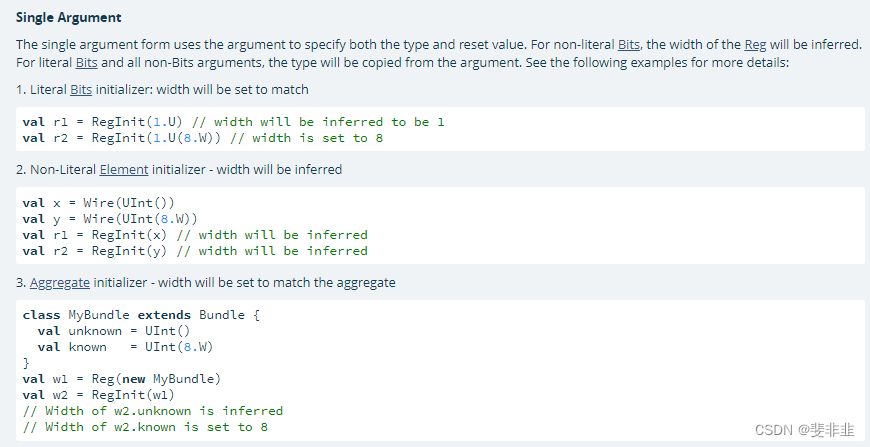

val reg = RegInit(0.U(8.W)) //ok

val reg = RegInit(0.UInt(8.W)) //err

U 使用在数字 . 后边50.U

UInt 使用在IO(new Bundle val a = Input(UInt(8.W)) 或者 def counter(max:UInt, a1:UInt)

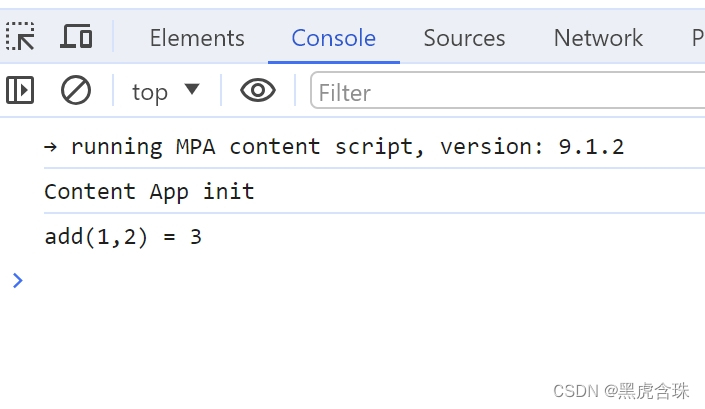

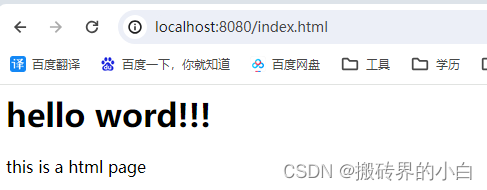

package emptyimport chisel3._

import chisel3.util._class MyCounter extends Module {val io = IO(new Bundle {val a = Input(UInt(8.W)) //val a = Input(U(8.W)) val c = Output(UInt(8.W))})val init = io.adef counter(max:UInt, a1:UInt) ={ //max:U //errval reg = RegInit(a1) //ok//val reg = RegInit(0.U(8.W)) //ok//val reg = RegInit(0.UInt(8.W)) //errwhen(reg===max) {reg := 0.U(max.getWidth.W)}.otherwise {reg := reg + 1.U(1.W)}reg // return value}io.c := counter(50.U, io.a)

}object MyCounterMain extends App {println("Generating the adder hardware")emitVerilog(new MyCounter(), Array("--target-dir", "generated"))

}