在上篇文章 ARMv8-AArch64 的异常处理模型详解之异常处理概述Handling exceptions中,作者对异常处理整体流程以及相关概念做了梳理。接下来,本文将详细介绍处理器在获取异常、异常处理以及异常返回等过程中都做了哪些工作。

ARMv8-AArch64 的异常处理模型详解之异常处理详解

- 一, 保存当前处理器状态(Saving the current processor state)

- PSTATE,Processor state

- PSTATE at AArch32

- SPSR,Saved Process Status Register

- 二,异常路由以及中断控制器

- SCR_EL3, Secure Configuration Register

- RW, bit [10], Execution state control for lower Exception levels.

- HCE, bit [8],Hypervisor Call instruction enable. HVC指令使能

- SMD, bit [7],Secure Monitor Call disable. 禁止使用SMC指令

- EA, bit [3],External Abort and SError interrupt routing,用于控制是否将外部异常以及SError路由到EL3

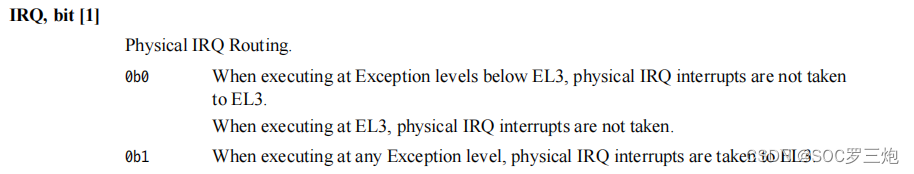

- FIQ, bit [2],IRQ, bit [1],用于控制IRQ和FIQ是否要路由到EL3

- NS, bit [0],用于控制EL2,EL1,以及EL0是否处于Non-secure状态

一, 保存当前处理器状态(Saving the current processor state)

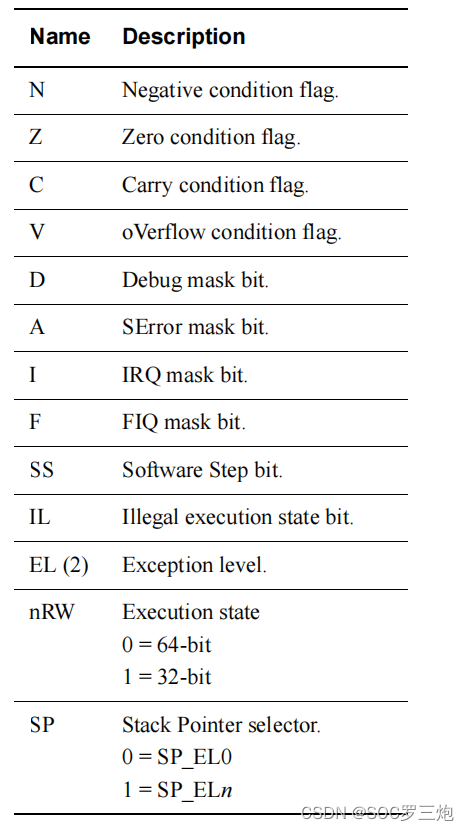

在ARMv7以及更早的架构中,有个程序状态寄存器(CPSR)来保存当前处理器的状态。而在ARMv8架构中,该寄存器被称为PSTATE(processor state)。PSTATE里包含了当前异常等级以及算数逻辑单元(Arithmetical Logical Unit (ALU))的一些标志位。在AArch64下,它们包括:

-

状态标志位,Condition flags

-

执行状态控制,Execution state controls

-

异常屏蔽位,Exception mask bits

-

访问控制位,Access control bits

-

Timing control bits

-

Speculation control bits

比如PSTATE中有四个屏蔽bit(DAIF),用于屏蔽四种异常: -

D - 调试屏蔽,Debug exception mask bit

-

A - SError异步异常屏蔽,SError asynchronous exception mask bit, for example, asynchronous external abort

-

I - IRQ异步异常屏蔽,IRQ asynchronous exception mask bit

-

F -FIQ异步异常屏蔽, FIQ asynchronous exception mask bit

PSTATE,Processor state

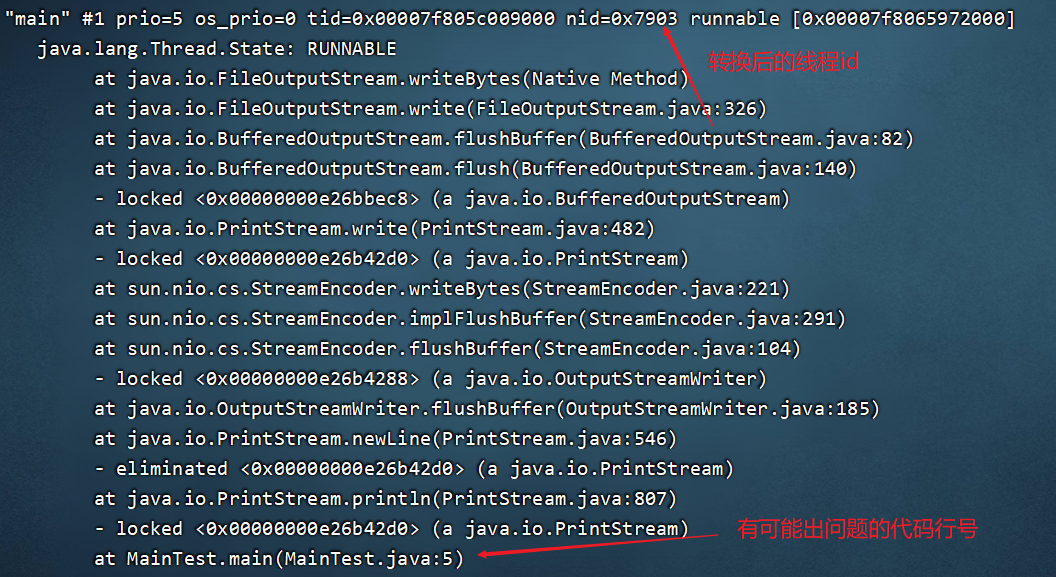

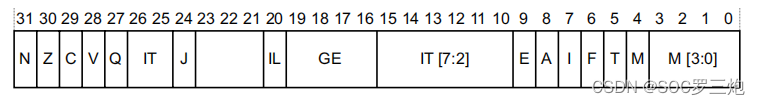

下图为AArch64模式下的PSTATE各个bit的功能描述表格:

在AArch64下,当使用ERET指令进行异常返回时,会让SPSR_ELn的值拷贝到PSTATE中。该操作会让处理器恢复到异常处理前的状态,其中包括:ALU的状态标志位(NZCV),执行状态(AArch64 或者AArch32),当前所处的异常等级以及处理器分支等等。并且将ELR_ELn中保存的地址恢复到PC(Program Counter)中,让处理器从该地址继续工作。

需要注意的是,PSTATE.{N, Z, C, V}可以在EL0下被访问,除了这四个bit,PSTATE的其他bit只能在EL1及更高的异常等级下被访问,对EL0来说是未定义的。

PSTATE at AArch32

在AArch32下,为了与ARMv7的CPSR相对应,PSTATE相比于AArch64,有额外的一些bit:

SPSR,Saved Process Status Register

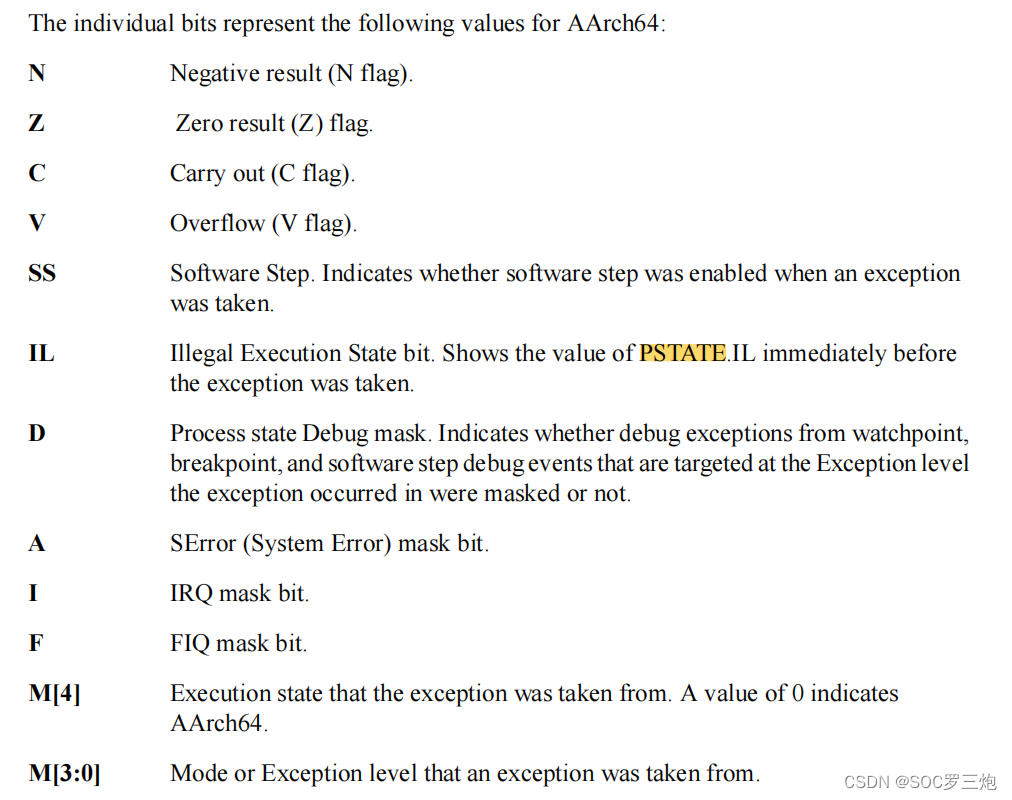

当异常发生时,处理器的PSTATE会被保存到对应的SPSR中,SPSR的作用相当于临时保存PSTATE的值,等到异常处理完成,执行了ERET指令后,SPSR的值将会重新写入到PSTATE中。

以下是AArch64下的SPSR的bit功能:

在ARMv8中,SPSR有三个:, SPSR_EL3,, SPSR_EL2以及SPSR_EL1。异常发生在哪个异常等级(taken to)就用哪个SPSR,比如异常发生在EL1(taken to EL1,taken from EL0),则使用SPSR_EL1,并且ELR_ELn和SPSR_ELn是成对使用的。

当PSTATE的值在SPSR里有了备份,然后,处理器就可以将当前的PSTATE更新为体系结构中为该异常类型定义的PSTATE,以反映新的状态。这包括更新受影响的目标异常级别和安全级别。当PSTATE被更新后,处理器就可以跳转到异常向量表的的异常处理函数中,具体从哪个目标异常等级的异常向量开始执行,这个由异常类型决定。

下图为EL0->EL1->EL0的异常处理示意图,在异常处理前需要将PC和PSTATE备份到ELR以及SPSR中,由于目标异常等级为EL1(taken to EL1),所以写入ELR_EL1以及SPSR_EL1中,在异常处理完成后,再将ELR_EL1以及SPSR_EL1中的值恢复到PC和PSTATE中。

二,异常路由以及中断控制器

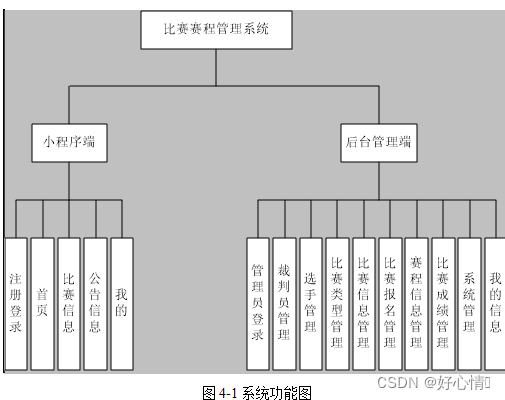

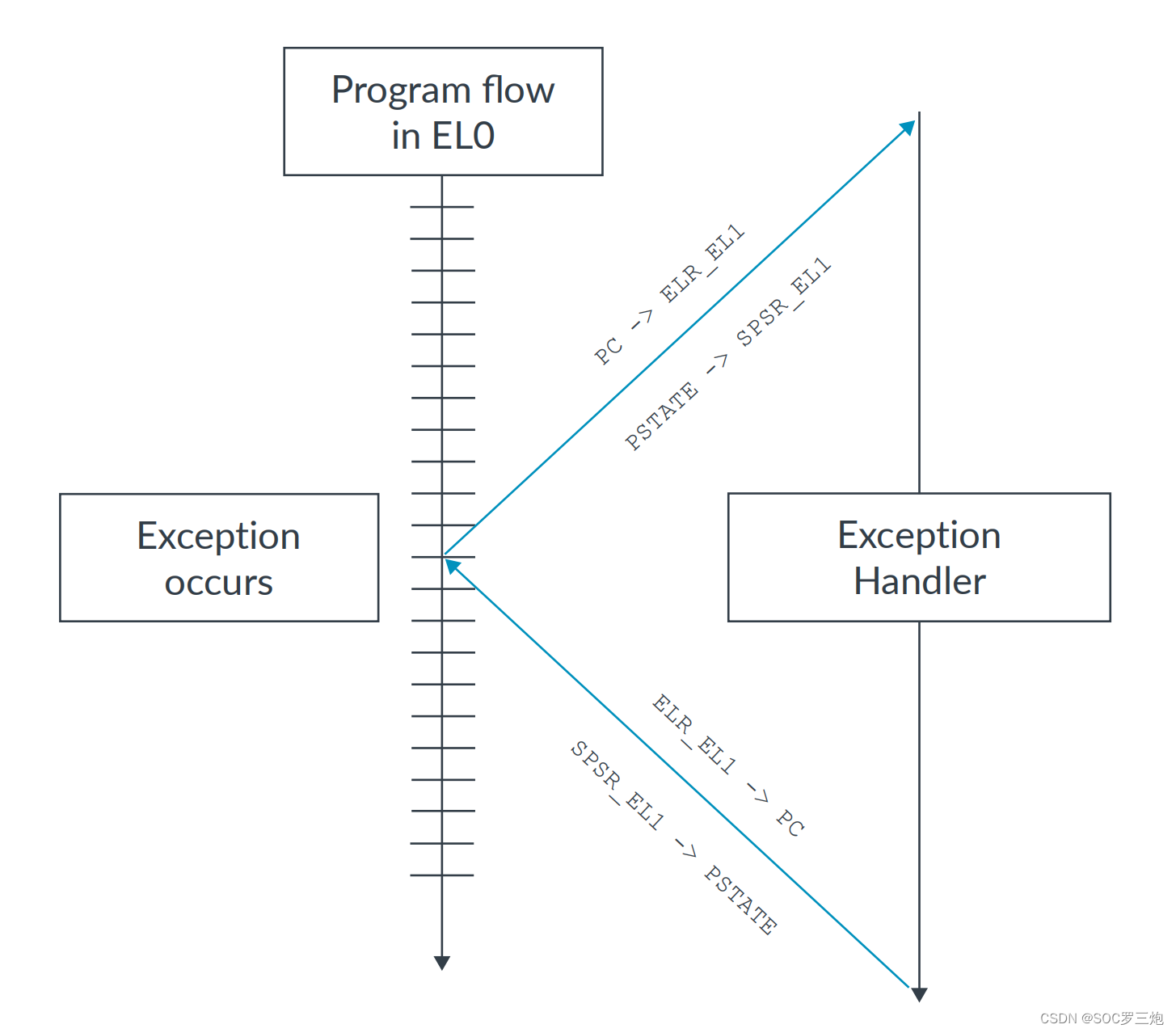

事实上,每种异常类型都有一个目标异常等级,有以下两种方式来指定:

- 通过异常类型隐式地指定。

- 由系统控制寄存器中的配置bit来指定。

总的来说,异常的目标异常等级要么是由架构实现定义的(固定,不可更改),要么就是软件使用路由控制来配置的。此外,异常的目标异常等级不能是EL0(taken to EL0)。

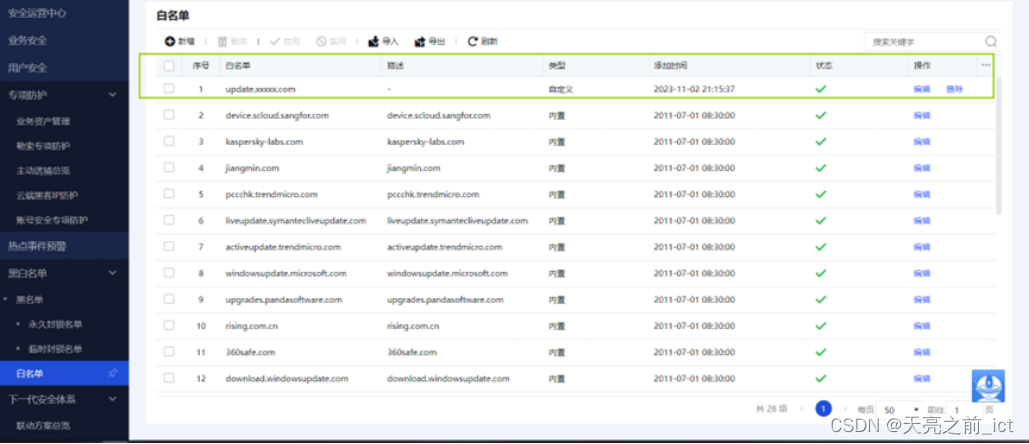

同步异常将根据与异常生成指令SVC、HVC和SMC相关联的规则进行路由。当系统实现了EL2或者EL3时,可以将其他类型的异常路由到EL2(Hypervisor)或EL3(Secure Monitor)。异常路由对IRQ、FIQ以及SError来说是独立设置的,如下图所示,在某个实现实例中,可以将所有的IRQ中断都路由到EL1中。

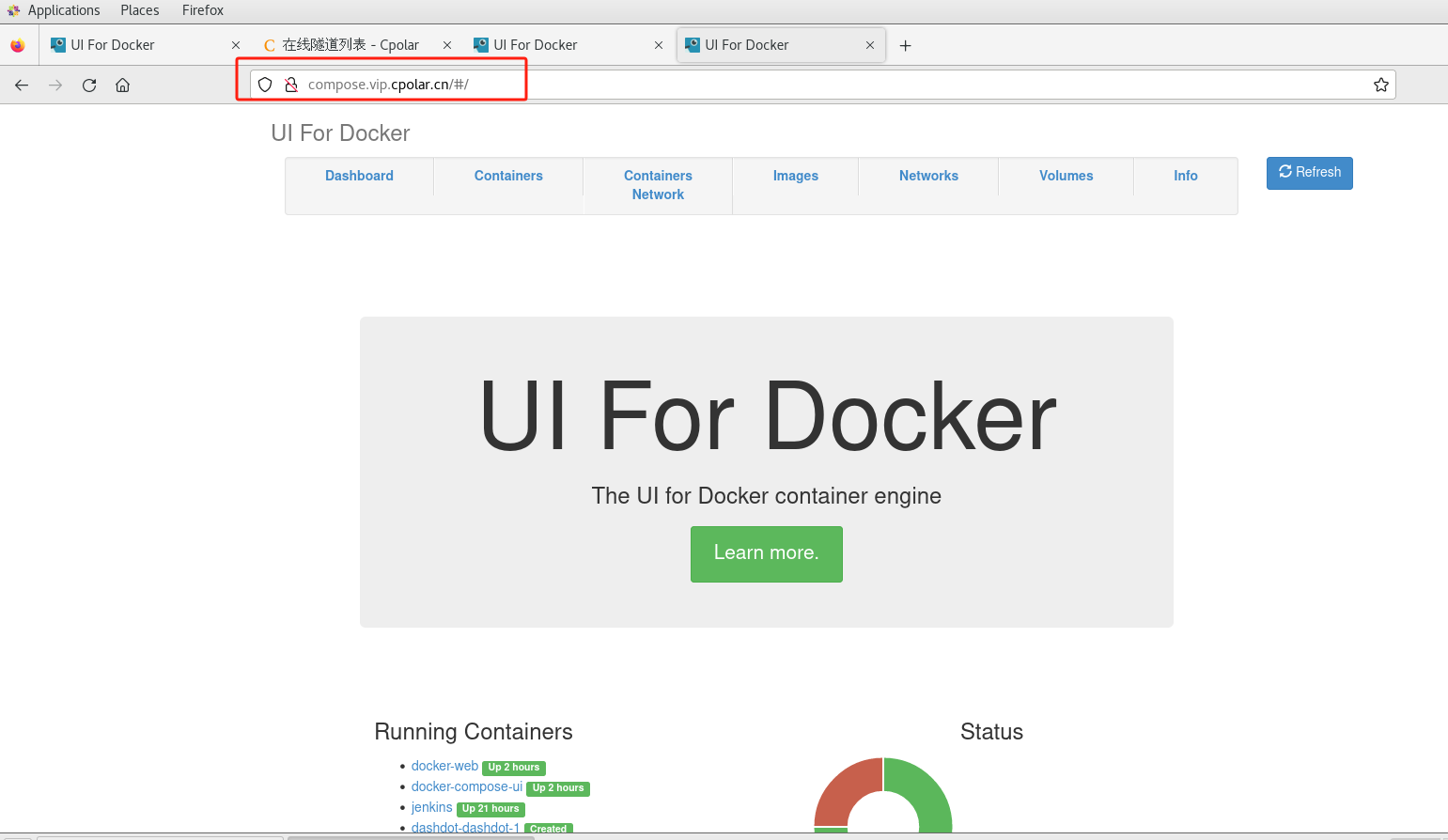

SCR_EL3, Secure Configuration Register

当EL3被实现时,安全配置寄存器SCR_EL3才能被访问。它主要用于配置当前处理器的安全状态,包括如下配置:

- EL0,EL1和EL2的安全状态,可以是Secure,Non-secure以及Realm。(EL3肯定是Secure的)

- 更低的异常等级的执行状态(AArch32还是AArch64)。

- IRQ、FIQ,SError中断以及外部中止异常(External abort exceptions)是否要在EL3下处理。

- 某些操作是否要在EL3下执行。

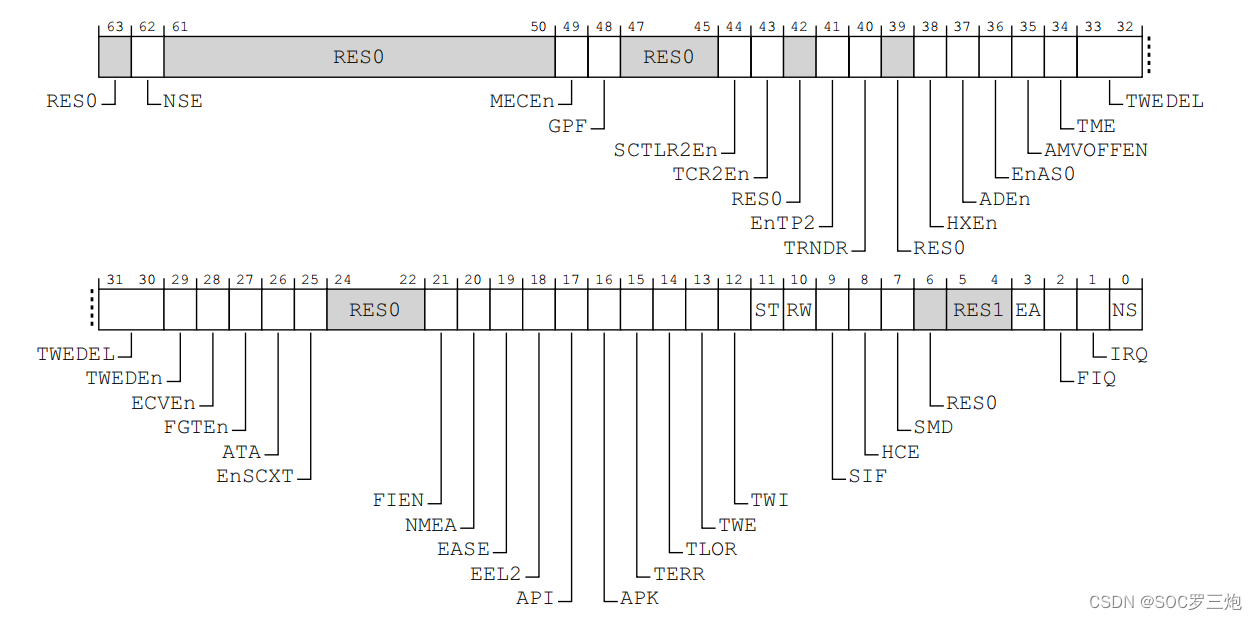

SCR_EL3是一个64-bit寄存器,它的各个bit如下图所示:

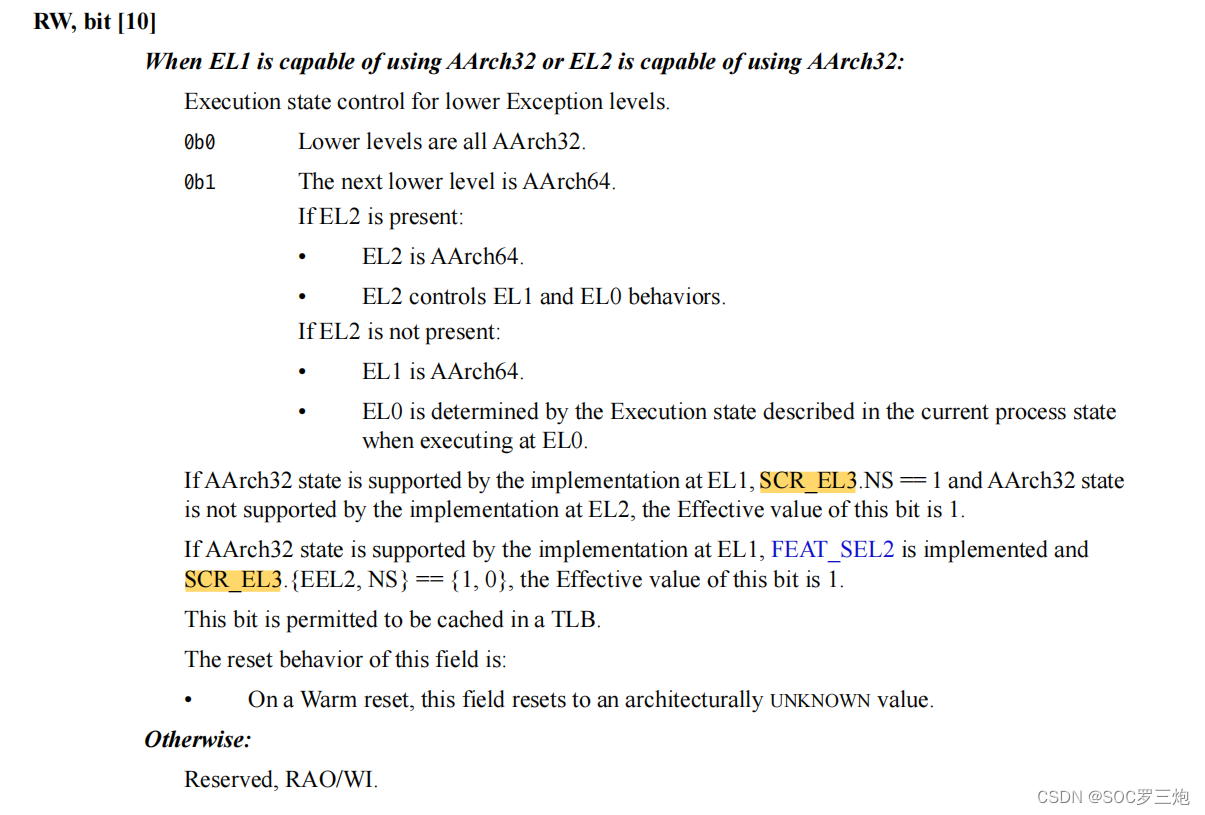

RW, bit [10], Execution state control for lower Exception levels.

HCE, bit [8],Hypervisor Call instruction enable. HVC指令使能

SMD, bit [7],Secure Monitor Call disable. 禁止使用SMC指令

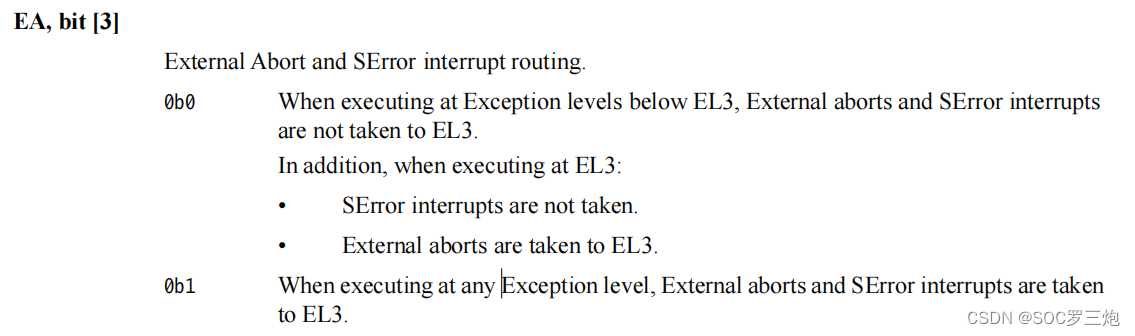

EA, bit [3],External Abort and SError interrupt routing,用于控制是否将外部异常以及SError路由到EL3

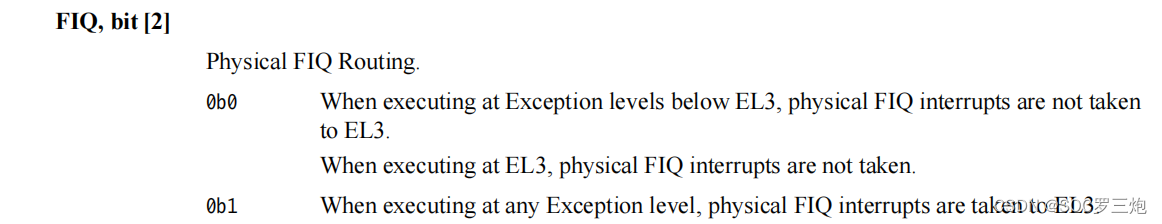

FIQ, bit [2],IRQ, bit [1],用于控制IRQ和FIQ是否要路由到EL3

NS, bit [0],用于控制EL2,EL1,以及EL0是否处于Non-secure状态

上小节简单介绍了安全配置寄存器SCR_EL3的用来配置异常路由的相关bit。除了SCR_EL3,还有Hypervisor

Configuration Register HCR_EL2。SCR_EL3寄存器指定哪些异常被路由到EL3,而HCR_EL2寄存器同样指定哪些异常被路由到EL2。

通过配置这些寄存器,可以将不同的中断类型路由到不同的异常级别。例如,IRQ中断可能由EL1的操作系统处理,而SErrors通常是由运行在EL3的固件处理。

在SCR_EL3以及HCR_EL2中都有单独的控制bit,允许单独控制IRQ、FIQ和SError中断的路由。如果SCR_EL3和HCR_EL2中的配置发生冲突时,SCR_EL3的路由配置会覆盖掉HCR_EL2中的配置。此外,这些控制bit在reset后的值是未知的,需要由软件来初始化。

在ARM架构中,有一个独立的模块:Generic Interrupt Controller (GIC),ARM 通用中断控制器,用于中断的管理,优先级分配以及中断路由。

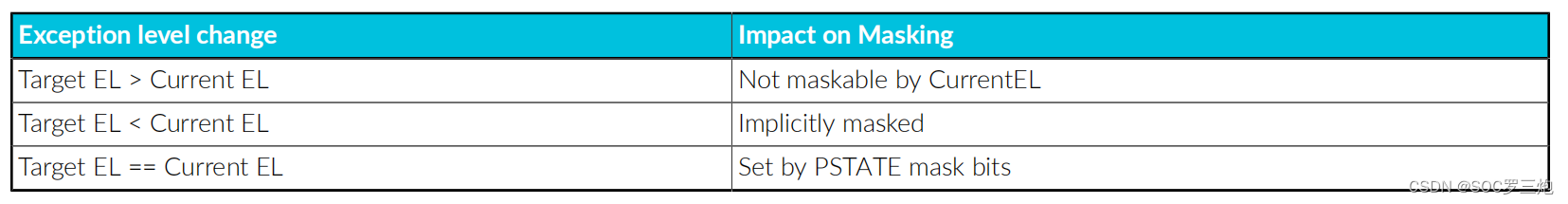

在之前介绍异步异常的时候提到过,异步异常可以暂时屏蔽并保持pending状态,直到异常被解除屏蔽并被获取。异常路由也会影响异常屏蔽,因为屏蔽的能力取决于当前和目标异常等级。

- 路由到较高异常级别的异常无法被较低的EL屏蔽(Target EL > Current EL)。例如,如果中断在EL1中被屏蔽,并且一个中断被路由到EL2,那么EL1的屏蔽设置将不会影响EL2的操作。但是,当处理器从EL2退出时,EL2的中断可能已经被屏蔽,这仍然可能导致中断在进入EL2时被屏蔽。

- 如果异常没有导致异常等级更改(Target EL == Current EL),那么路由到当前异常级别的异常可以被当前级别屏蔽。

- 路由到较低异常级别的异常总是可以被屏蔽(Target EL < Current EL)。

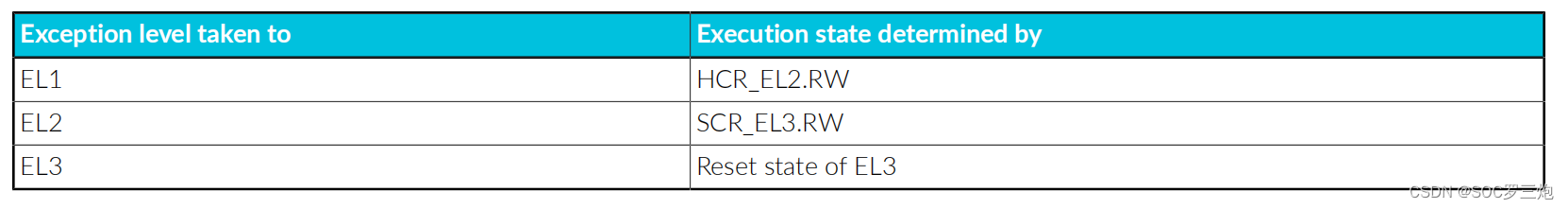

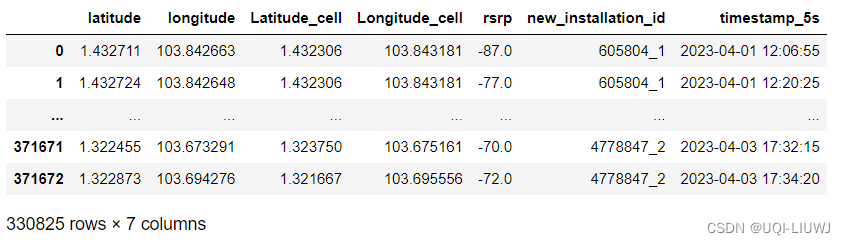

接收异常的异常级别(taken to)的执行状态由更高的异常级别决定。假设所有异常级别都已实现,下表显示了如何确定某个异常等级的执行状态(AArch32 or AArch64):