相关阅读

静态时序分析![]() https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

时序路径是静态时序分析中的一个重要概念,了解时序路径能帮助设计者更好地编写SDC脚本,本文旨在详细介绍时序路径相关内容。

首先给出时序路径的定义:时序路径是由时序弧构成的数据路径,静态时序分析会分别对每条有约束的时序路径进行时序检查(例如建立时间检查、保持时间检查、移除时间检查、恢复时间检查等)。

时序路径可以是典型的,也可以是非典型的;时序路径可以是有约束的,也可以是未约束的。

典型的时序路径

典型时序路径的起点是输入端口(包括输入输出双向端口)或触发器的时钟引脚;典型时序路径的终点是输出端口(包括输入输出双向端口)或触发器的数据引脚(包括复位引脚)。

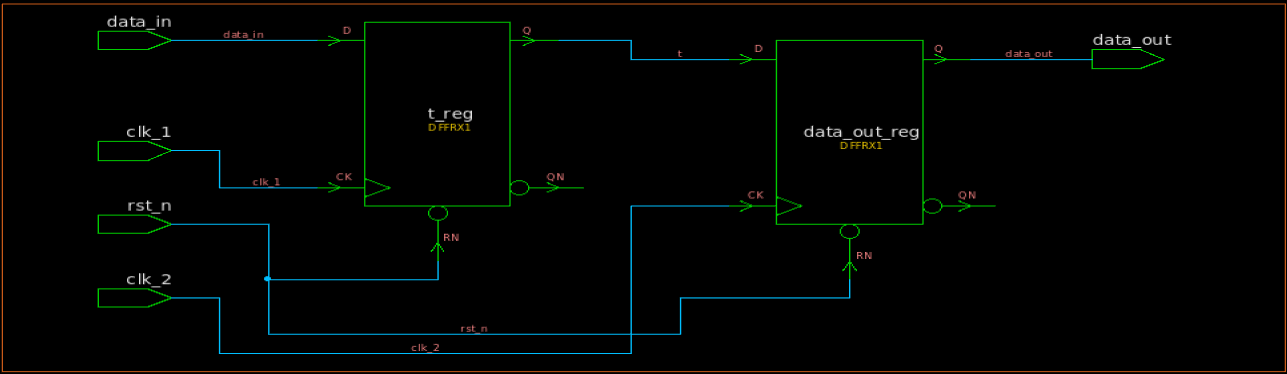

下面将举例进行说明,图1是一个简单电路的示意图,它由两个D触发器组成。

图1 一个简单的例子

按照上面的定义,此时一共存在五条典型的时序路径,分别是:

- 输入端口data_in到触发器t_reg的数据引脚D。

- 触发器t_reg的时钟引脚CK到触发器data_out_reg的数据引脚D。

- 触发器data_out_reg的时钟引脚CK到输出端口data_out。

- 输入端口rst_n到触发器t_reg的复位引脚RN。

- 输入端口rst_n到触发器data_out_reg的复位引脚RN。

可以使用下面的report_timing命令,分别给出这五条时序路径的时序报告(仅给出最大路径max时序报告),如图1到图5所示。

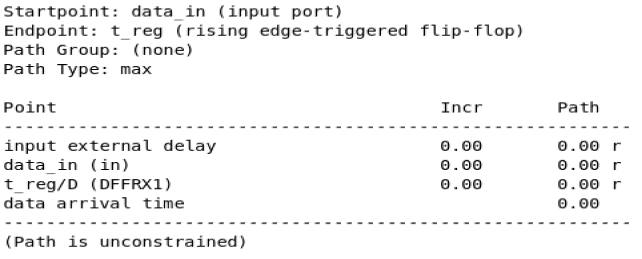

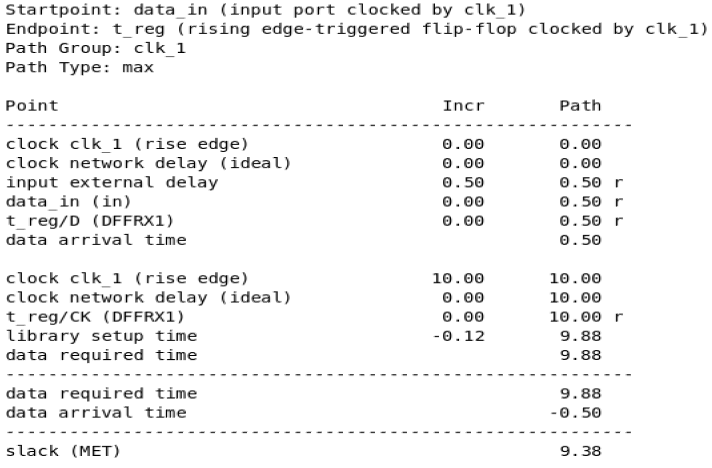

report_timing -from [get_port data_in] -to [get_pin t_reg/D]

图1 第一条时序路径的时序报告

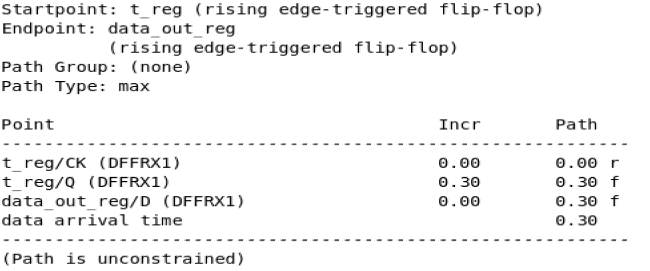

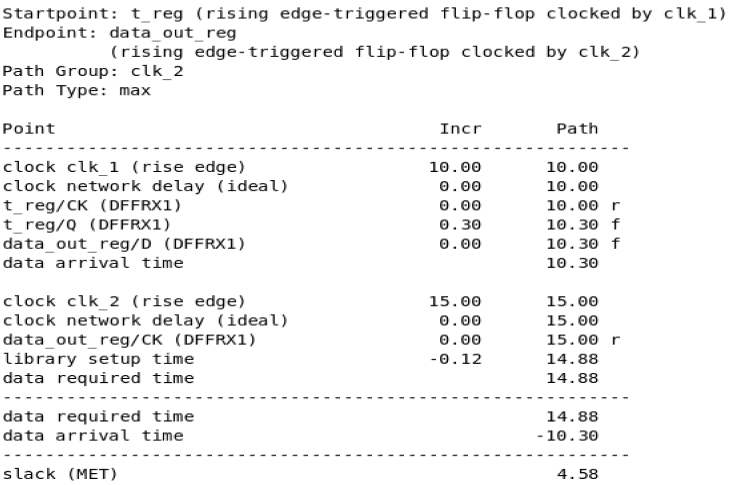

report_timing -from [get_pin t_reg/CK] -to [get_pin data_out_reg/D]

图2 第二条时序路径的时序报告

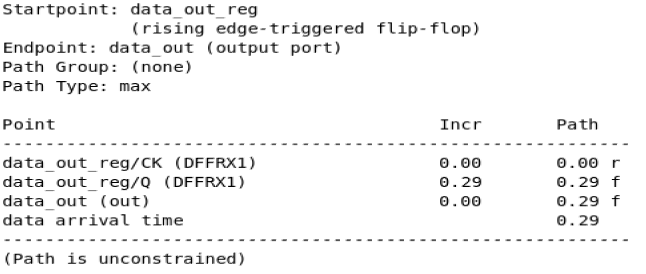

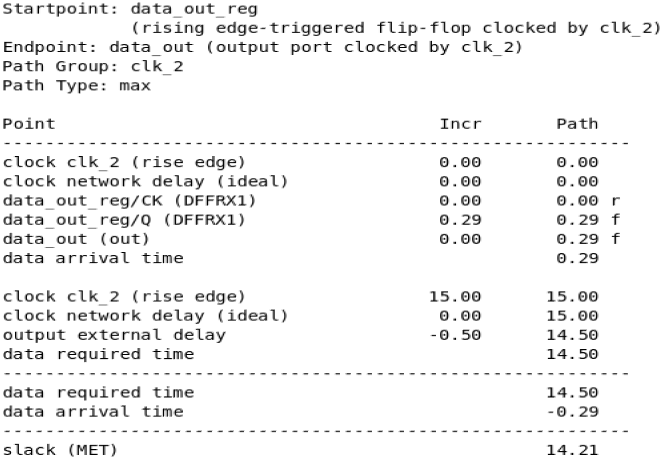

report_timing -from [get_pin data_out_reg/CK] -to [get_port data_out]

图3 第三条时序路径的时序报告

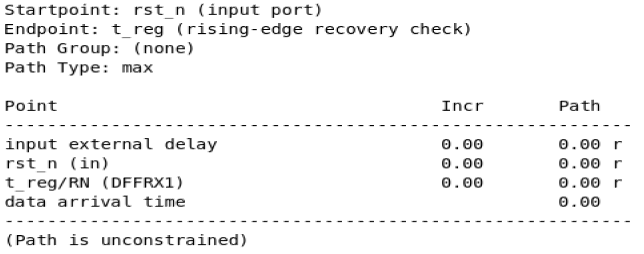

下面两条终点是异步复位信号的时序路径在使用report_timing命令报告前,需要先设置DC中的环境变量,因为默认情况下,DC会将触发器时钟引脚CK到复位引脚RN的时序弧中断。

enable_recovery_removal_arcs 默认值false

timing_disable_recovery_removal_checks 默认值true/*它们永远保持相斥,可以将enable_recovery_removal_arcs设置为true,也可以将

timing_disable_recovery_removal_checks设置为fasle,DC会自动设置另一个变量。*/set enable_recovery_removal_arcs true

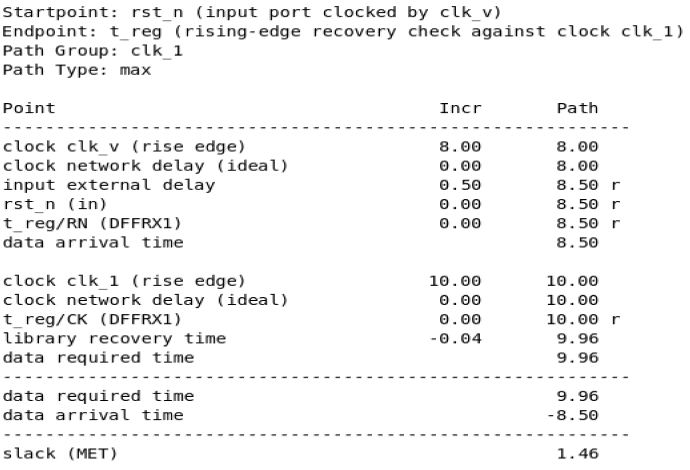

set timing_disable_recovery_removal_checks false //两者取一即可report_timing -from [get_port rst_n] -to [get_pin t_reg/RN]

图4 第四条时序路径的时序报告

report_timing -from [get_port rst_n] -to [get_pin data_out_reg/RN]

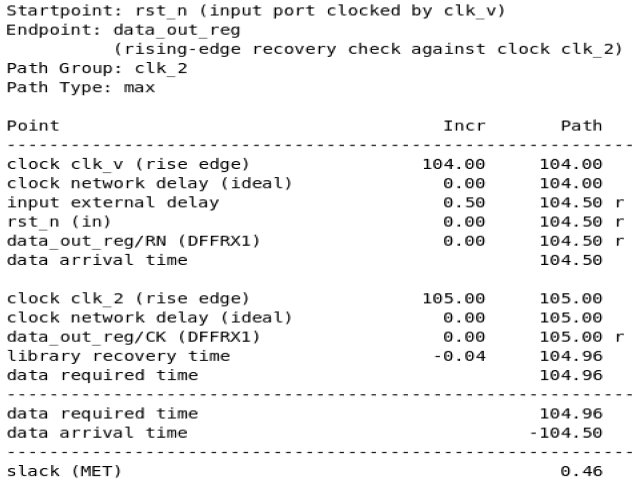

图5 第五条时序路径的时序报告

从图1到图5中的Startpoint和Endpoint可以清晰地看出时序路径的起点和终点,图中并未将触发器的时钟引脚、数据(复位)引脚直接写作起点和终点,而是将整个触发器作为起点和终点,并且括号内还说明了触发器的类型,这代表触发器拥有从时钟引脚到数据输入/输出端的时序弧。在后面的非典型时序路径中,我们会看到数据(复位)引脚直接写作终点的情况,这反而是少见的。

从图中我们可以看到,这些时序路径都属于none路径组,这是因为它们未约束的。下面我们使用命令约束这几条时序路径,如图6到图10所示。

create_clock -period 10 [get_port clk_1]

create_clock -period 15 [get_port clk_2]

create_clock -period 8 -name clk_v //创建虚拟时钟,为了约束复位端口set_input_delay 0.5 -clock [get_clock clk_1] [get_port data_in] //输入延迟约束

set_input_delay 0.5 -clock [get_clock clk_1] [get_port data_in] //输入延迟约束

set_input_delay 0.5 -clock [get_clock clk_v] [get_port rst_n] //输入延迟约束set_output_delay 0.5 -clock [get_clock clk_2] [get_port data_out] //输出延迟约束

report_timing -from [get_port data_in] -to [get_pin t_reg/D]

图6 第一条时序路径的时序报告(建立时间)

report_timing -from [get_pin t_reg/CK] -to [get_pin data_out_reg/D]

图7 第二条时序路径的时序报告(建立时间)

report_timing -from [get_pin data_out_reg/CK] -to [get_port data_out]

图8 第三条时序路径的时序报告(建立时间)

report_timing -from [get_port rst_n] -to [get_pin t_reg/RN]

图9 第四条时序路径的时序报告(恢复时间)

report_timing -from [get_port rst_n] -to [get_pin data_out_reg/RN]

图10 第五条时序路径的时序报告(恢复时间)

从图6到图9中可以看出,时序路径起点和终点的括号内的clock信息表示端口、触发器(引脚)已经被时钟约束了,一般而言(指典型时序路径)只有起点和终点都被时钟约束了,才代表这条时序路径才可以进行时序分析(还有一个条件:该路径不能被设置为伪路径),此时每条时序路径属于一个时序组,从图6到图9中可以看出其按照约束其终点的时钟分组,即时序路径1、4属于时序组clk_1,时序路径2、3、5属于时序组clk_2。

非典型的时序路径

非典型时序路径只有在使用几条特定的约束命令后可能出现,包括set_disable_timing命令、set_min_delay命令和set_max_delay命令,这些命令会导致时序路径分割,一般情况不会遇见。

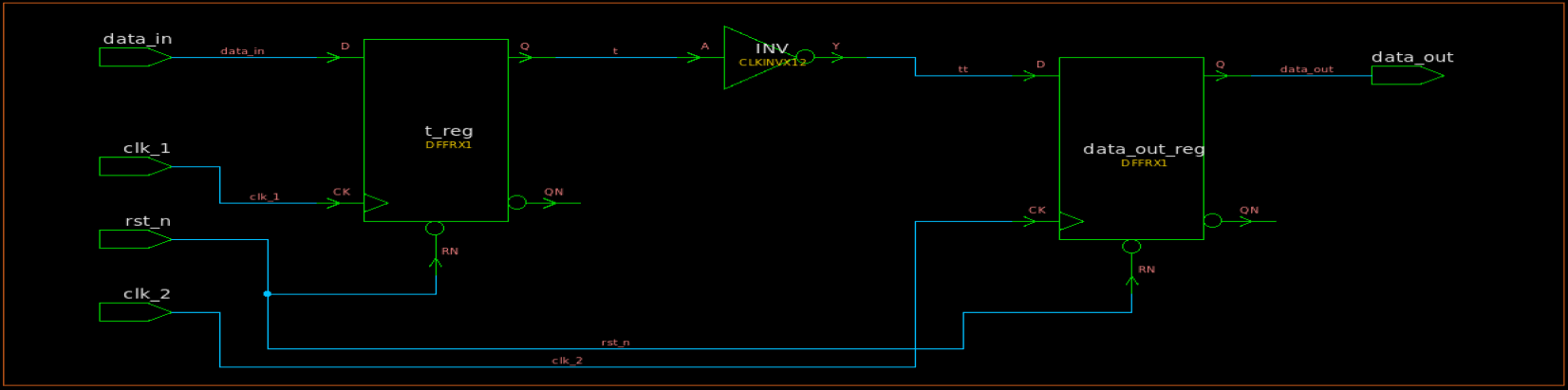

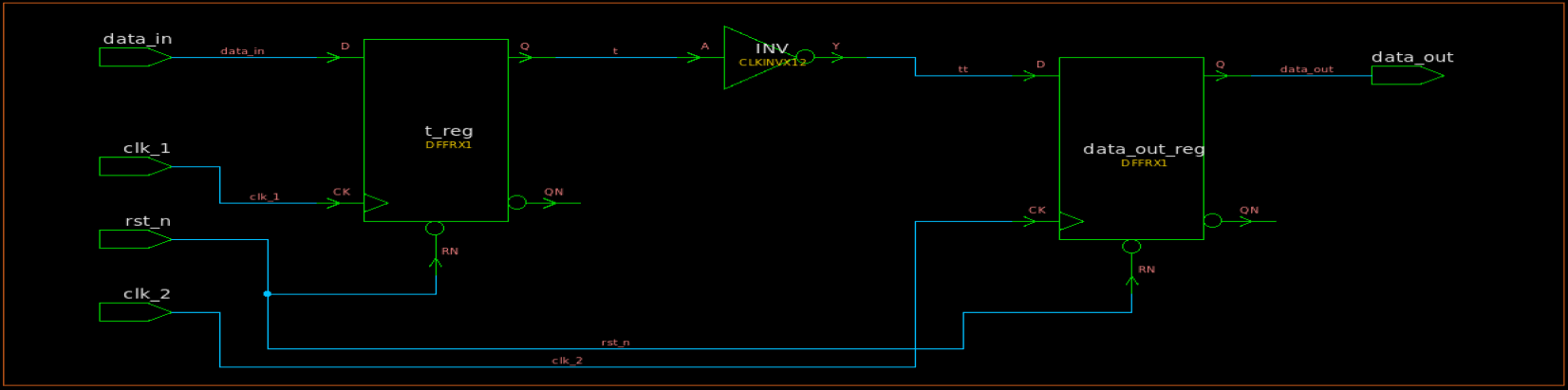

非典型路径的起点可以是端口和任意单元的引脚,只要能保证有相应的时序弧。下面将举例进行说明,图11是一个简单电路的示意图,它和图1很相似,只多了一个反相器,因此也拥有相似的五条时序路径。

图11 另一个简单的例子

还是使用相同的命令,为设计添加约束。

create_clock -period 10 [get_port clk_1]

create_clock -period 15 [get_port clk_2]

create_clock -period 8 -name clk_v //创建虚拟时钟,为了约束复位端口set_input_delay 0.5 -clock [get_clock clk_1] [get_port data_in] //输入延迟约束

set_input_delay 0.5 -clock [get_clock clk_1] [get_port data_in] //输入延迟约束

set_input_delay 0.5 -clock [get_clock clk_v] [get_port rst_n] //输入延迟约束set_output_delay 0.5 -clock [get_clock clk_2] [get_port data_out] //输出延迟约束

随后我们使用set_max_delay命令,指定从触发器t_reg的时钟引脚CK到反相器INV的输入引脚A的最大延迟。这会导致路径分割,原本从触发器t_reg的时钟引脚CK到触发器data_out_reg的数据引脚D的时序路径被分割为两条:一条从触发器t_reg的时钟引脚CK到反相器INV的输入引脚A;另一条从反相器INV的输入引脚A到触发器data_out_reg的数据引脚D,如图12和图13所示。

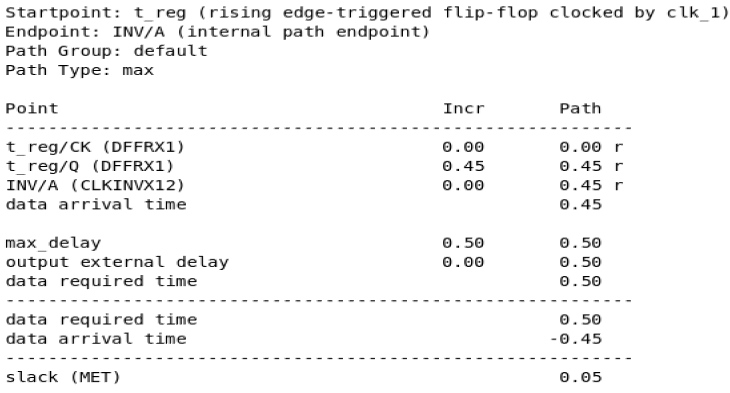

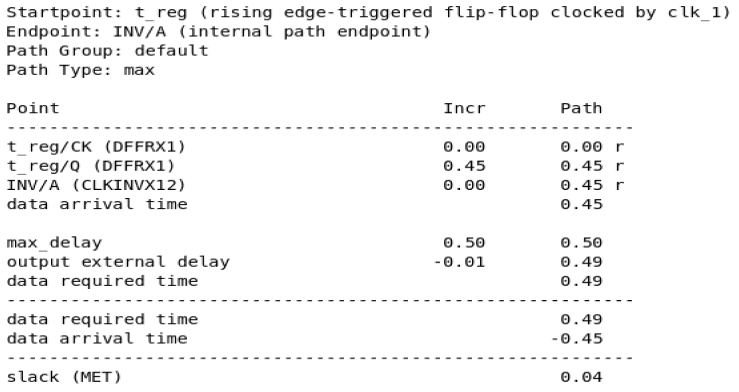

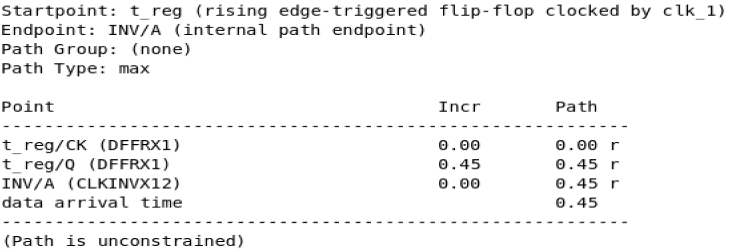

set_max_delay 0.5 -from [get_pin t_reg/CK] -to [get_pin INV/A]report_timing -from [get_pin t_reg/CK] -to [get_pin INV/A]

图12 第一条非典型的时序路径(最大延迟)

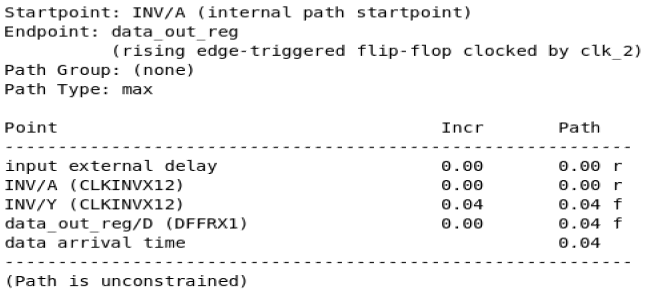

report_timing -from [get_pin INV/A] -to [get_pin data_out_reg/D]

图13 第二条非典型的时序路径

尽管已经提前介绍,但这两份时序报告仍可能会让人产生很多疑惑,下面详细说明。图12中时序路径的终点和图13中时序路径的起点分别是反相器的输入、输出引脚,这是时序分割所带来的,括号内的internal path也说明了着这是一个内部的起、终点,它们没有被时钟约束。

第一条时序路径即使终点没有时钟约束,但依旧进行了最大延迟的时序分析,这是因为第一条时序路径就是set_max_delay命令所指定的路径,这种终点没有时钟约束的时序路径被归为时序组default。另外要注意的是,可以为第一条时序路径的终点添加输出延迟约束(无论是否关联时钟),如关联了时钟,则时序组会变成关联时钟组,图14和图15分别展示了这两种情况。

set_output_delay 0.01 [get_pin INV/A] //输出延迟约束(无关联时钟)report_timing -from [get_pin t_reg/CK] -to [get_pin INV/A]

图12 第一条非典型的时序路径(输出延迟约束(无关联时钟))

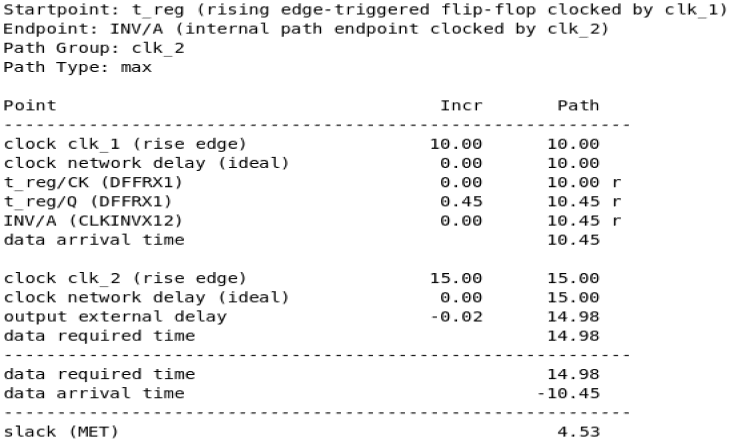

set_output_delay 0.02 -clock [get_clock clk_2] [get_pin INV/A] //输出延迟约束(有关联时钟)report_timing -from [get_pin t_reg/CK] -to [get_pin INV/A]

图13 第一条非典型的时序路径(输出延迟约束(有关联时钟))

第二条时序路径的起点没有时钟约束,但无法进行时序分析,因为第二条时序路径不是set_max_delay命令所指定的路径,即使终点已经被时钟约束,此时要为第二条时序路径的起点添加有关联时钟的输入延迟约束。

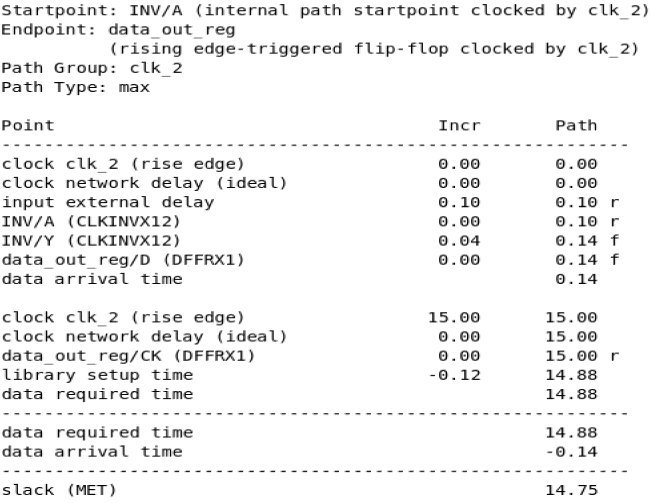

set_input_delay 0.1 -clock [get_clock clk_2] [get_pin INV/A] //输入延迟约束(有关联时钟)report_timing -from [get_pin INV/A] -to [get_pin data_out_reg/D]

图14 第二条非典型的时序路径(输出延迟约束(有关联时钟))

下面来看最后一个例子巩固一下,非典型时序路径的相关知识。还是以图11为例,为了方便重绘为图15。

图15 另一个简单的例子

这次我们使用set_max_delay命令,指定从反相器INV的输入引脚A到反相器INV的输出引脚Y的最大延迟。路径分割后,原本从触发器t_reg的时钟引脚CK到触发器data_out_reg的数据引脚D的时序路径被分割为三条:一条从触发器t_reg的时钟引脚CK到反相器INV的输入引脚A;一条从反相器INV的输入引脚A到反相器INV的输出引脚Y;一条从反相器INV的输出引脚Y到触发器data_out_reg的数据引脚D。如图16、图17和图18所示。

set_max_delay 0.5 -from [get_pin INV/A] -to [get_pin INV/Y]report_timing -from [get_pin t_reg/CK] -to [get_pin INV/A]

图16 第一条非典型的时序路径

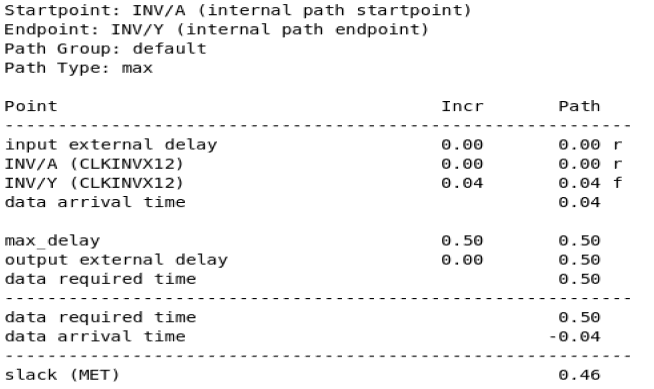

report_timing -from [get_pin INV/A] -to [get_pin INV/Y]

图17 第二条非典型的时序路径(最大路径)

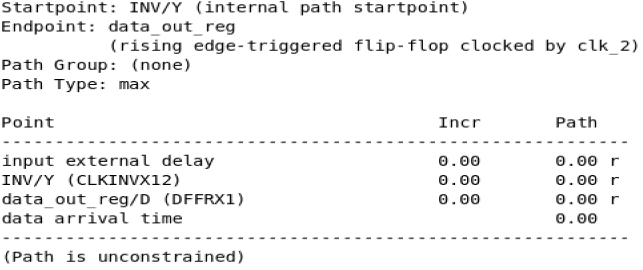

report_timing -from [get_pin INV/Y] -to [get_pin data_out_reg/D]

图18 第三条非典型的时序路径(最大路径)

可上一个例子一样,可以为第一条非典型的时序路径的终点添加有关联时钟的输出延迟约束。可以为第二条非典型的时序路径的起点添加有(无)关联时钟的输入延迟约束、终点添加有(无)关联时钟的输出延迟约束。可以为第三条非典型的时序路径的起点添加有关联时钟的输入延迟约束。

因为篇幅问题,本文的第一部分到此结束,后面随缘更。