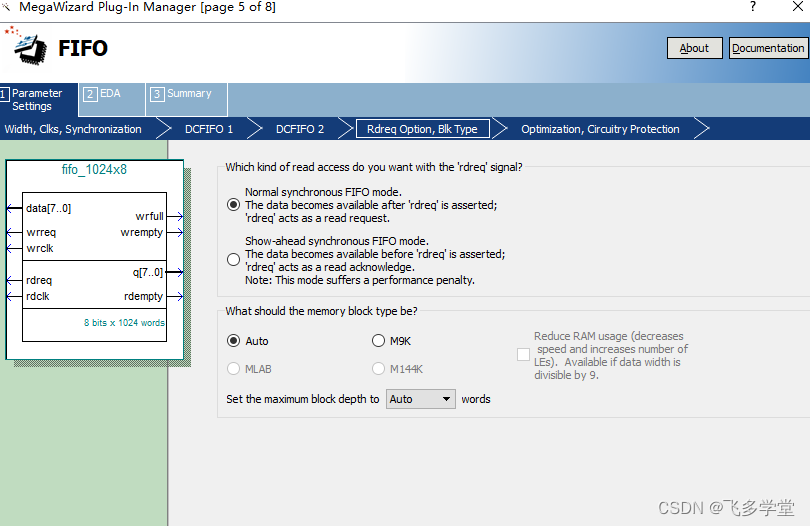

FPGA FIFO 读取模式分两种:

- Normal Mode:

- In normal mode, the “rdreq” signal serves as the read request or read enable. When this signal goes high, the data output provides the first data from the FIFO.

- Essentially, in normal mode, data is available at the rising edge of the clock following a valid “rdreq” signal.

- Show-Ahead Mode:

- Show-ahead mode introduces a slight twist. Here, the “rdreq” signal acts as a confirmation that data has already been read. When “rdreq” becomes inactive, the data output provides the first data from the FIFO.

- But wait, there’s more! When “rdreq” goes high again, the data output now presents the second data.

- In summary, show-ahead mode anticipates the next read and provides the second data ahead of time, which can be useful in certain scenarios.

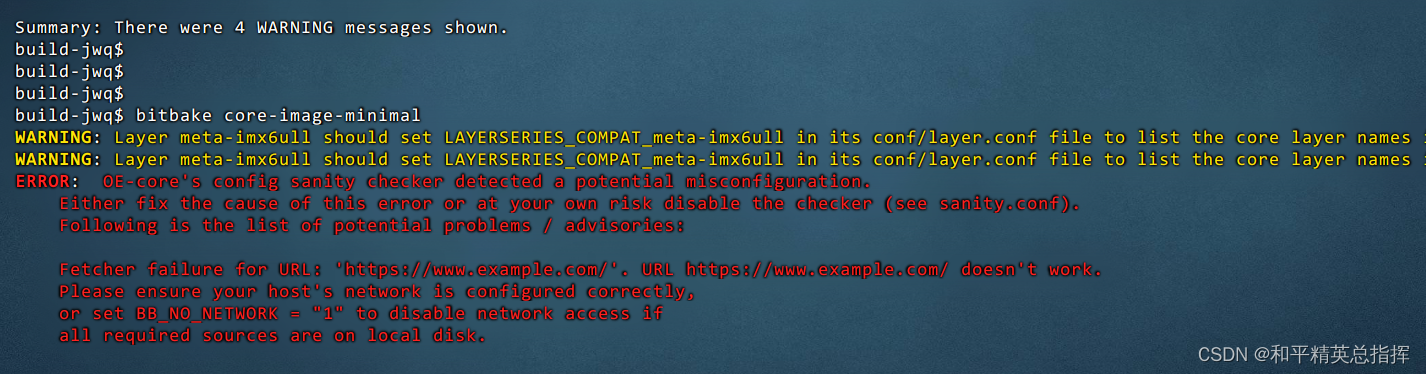

正常模式:

在正常模式下,“rdreq” 信号用作读取请求或读取使能。当此信号变高时,数据输出提供 FIFO 中的第一个数据。 基本上,在正常模式下,数据在有效的 “rdreq” 信号之后的时钟上升沿处可用。

Show-Ahead 模式:

Show-ahead 模式引入了一个小小的变化。在这里,“rdreq” 信号充当一个确认信号,表明数据已经被读取。当 “rdreq” 变为非活动状态时,数据输出提供 FIFO 中的第一个数据。 但等等,还有更多!当 “rdreq” 再次变高时,数据输出现在呈现第二个数据。 总之,show-ahead 模式预期下一次读取,并提前提供第二个数据,这在某些情况下非常有用。

虽然 show-ahead 模式提供了即时读取的特性,但它也存在一个缺点:与正常模式相比,它可能会稍微降低性能。