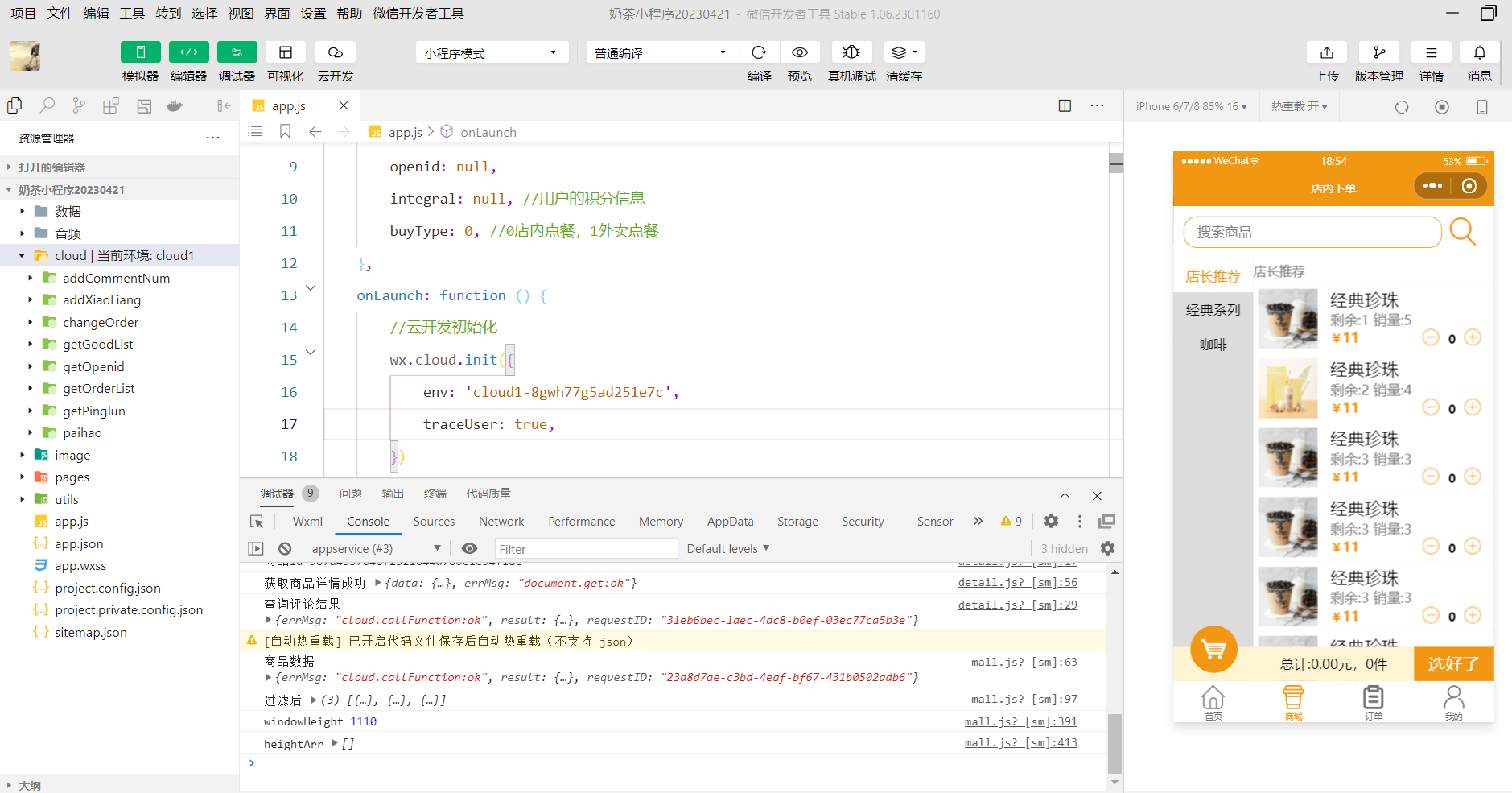

视频链接

FPGA-K7板级系统硬件实战01_哔哩哔哩_bilibili

FPGA-K7板级原理图硬件实战

- 基于XC7K325TFFG900的FPGA硬件实战框图

基于XILINX 的KINTEX-7 芯片XC7K325FPGA的硬件平台,FPGA 开发板挂载了4 片512MB 的高速DDR3 SDRAM 芯片,另外板上带有一个SODIMM接口用于扩展DDR3 的内存条。FPGA 芯片配置使用1 片128Mb 的QSPI FLASH 芯片。外围电路方面为用户扩展了丰富的接口,比如1 个PCIex8 接口、4 路10G SFP 光纤接口、1 路40G 的QSPF+光纤接口、1 路UART 串口接口、1 路SD 卡接口、1 个FMC 扩展接口、一个40 针的扩展口等等。

满足用户各种高速数据交换,数据存储,视频传输处理以及工业控制的要求,是一款"专业级“的FPGA 开发平台。为高速数据传输和交换,数据处理的前期验证和后期应用提供了方案。

1、系统框图(★)

1.1、时钟框图

1.2、复位框图

1.3、电源框图(S5课详解)

2、基于XC7K325T-2FFG900的FPGA硬件实战

2.1、XC7K325T-2FFG900 FPGA 简介

Kintex 7 FPGA Package Device Pinout Files (K7)

《 ug475_7Series_Pkg_Pinout 》

主芯片使用的是Xilinx公司的KINTEX-7 FPGA芯片,型号为XC7K325T-2FFG900I。

属于Xilinx公司Kintex-7系列的产品。

速度等级为-2,温度等级为工业级。此型号为FGG900 封装,900 个引脚,引脚间距为1.0mm。

Xilinx ARTIX-7 FPGA的芯片命名规则如下:

芯片XC7K325T-2FFG900I为例进行简单介绍:

·XC7K:Xilinx公司KINTEX-7系列;

·325T:LE逻辑单元的数量,并带有高速串行收发器,各型号的逻辑资源量详见图下图

·-2:器件的速度等级,数字越大表示速度等级越高;

·FFG:封装方式;

·900:表示封装引脚数量;

·I:工作温度,商业级C:0℃~70℃,工业级I:-40℃~85℃、军工级: -55℃~125℃

k系列资源库

其中FPGA芯片XC7K325T的主要参数如下所示:(★)

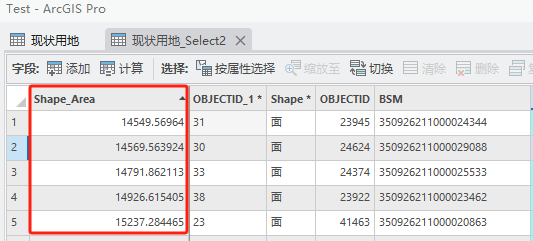

| 名称 | 具体参数 |

| 逻辑单元Logic Cells | 326,080 |

| 查找表(Slices) | 50,950 |

| 触发器(CLB flip-flops) | 407,600 |

| Block RAM(36kb each)大小 | 445 |

| DSP处理单元(DSP Slices) | 840 |

| PCIe Gen2 | 1 |

| 模数转换/XADC | 1个12bit, 1Mbps AD |

| GTP Transceiver | 16 个,12.5Gb/s max |

| 速度等级 | -2 |

| 温度等级 | 工业级 |

2.1.1、XC7K325T-2FFG900的管脚分类

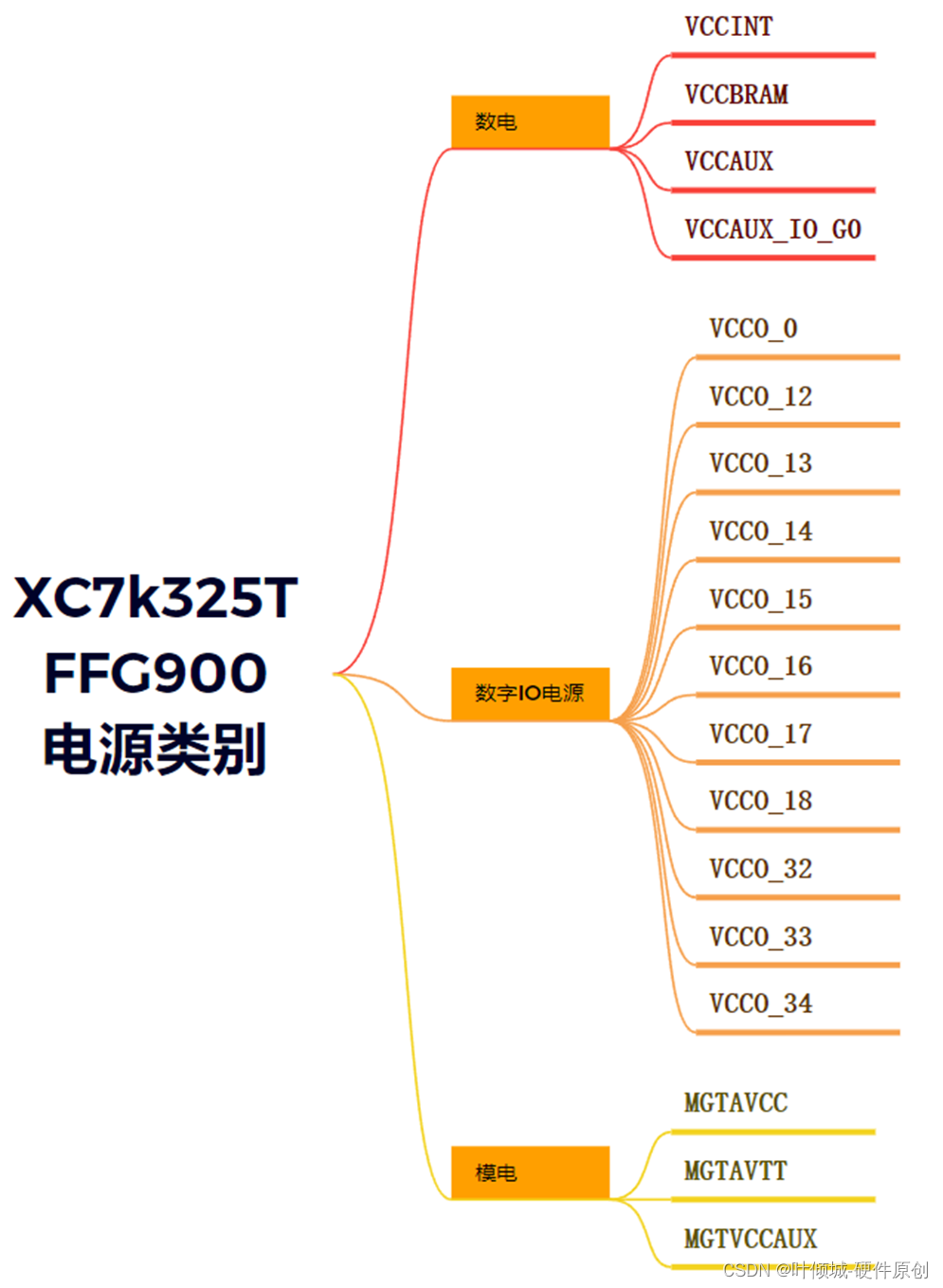

2.1.2、XC7K325T-2FFG900电源管脚分类

2.2、时钟电路 (参考19课)

2.3、复位按键 (参考20课)

2.4、JTAG接口 (参考31课)

2.5、QSPI Flash (参考22课)

2.6、DDR3 (参考23课)

2.7、SODIMM内存条接口 (参考25课)

2.8、USB转串口 (参考7课)

2.9、SFP光纤接口 (参考3课)

2.10、QSFP+光纤接口 (参考3课)

2.11、pcie插槽 (参考47课)

2.12、温度传感器 (参考11课)

2.13、SD卡槽 (参考8课)

2.14、FMC连接器 (参考56课)

2.15、风扇 (参考12课)

2.16、LED灯 (参考42课)

2.17、40针扩展接口(注意电平匹配)

2.18、电源接口 (参考实战Power2-电源入口)

3、基于K7的FPGA硬件设计注意事项(★)

3.1、FPGA中Config0的相关管脚设置

| CFGBVS_0 | VCCO_0电压为3.3V/2.5V时,CFGBVS为高电平,即接到VCCO_0; VCCO_0电压为1.8V/1.5V时,CFGBVS为低电平,即接到GND。 |

| PROGRAM_B_0 | 低电平有效复位配置逻辑。当PROGRAM_B脉冲为低电平时,FPGA配置被清零并启动新的配置序列。 在下降沿启动配置复位,并且配置(即编程)序列在随后的上升沿开始。为了确保输入稳定的高电平,需要外部连接一个≤4.7kΩ的电阻到VCCO_0。 |

| INIT_B_0 | 配置存储器的初始化(低电平有效); 当FPGA处于配置复位状态,FPGA正在初始化(清除)其配置存储器时,或者当FPGA检测到配置错误时,FPGA将此引脚驱动为低电平。完成FPGA初始化过程后,INIT_B释放到高阻态,此时外部电阻预计将INIT_B拉高。 在上电期间,INIT_B可以在外部保持低电平,以在初始化过程结束时停止上电配置序列。 当初始化过程后在INIT_B输入检测到高电平时,FPGA继续执行M [2:0]引脚设置所指示的配置序列的其余部分。 将INIT_B连接至一个≤4.7kΩ的上拉电阻至VCCO_0,以确保从低到高的转换。 |

| DONE_0 | DONE表示配置成功完成(高电平有效)作为输出,这个引脚说明配置过程已经完成;作为输入,配置为低电平可以延迟启动。 |

| DXP_0,DXN_0 | 温度检测二极管引脚(阳极:DXP;阴极:DXN)。使用bank0中的DXP和DXN引脚访问热敏二极管。不使用时,连接到GND。 要使用热敏二极管,必须添加适当的外部热监控IC。 |

| VP_0, VN_0 | XADC专用差分模拟输入 如果不使用,这个引脚应该连接到GND。 |

| VREFP_0 | 如果没有提供外部参考,则该引脚应该始终连接到GNDADC。 |

| VREFN_0 | 即使没有提供外部引用,该引脚也应该始终连接到GND。 |

| VCCBATT | VCCBATT是FPGA内部易失性存储器的电池备份电源,用于存储AES解密器的密钥。1.8V电平 |

3.1.2、M2_0、M1_0、M0_0、CCLK_0(FPGA采用Master SPI配置模式001)

3.1.3、VCCADC_0、GNDADC_0 (XADC模块)

3.1.4、TCK_0、TDI_0、TDO_0、TMS_0 (JTAG)

3.2、FPGA中bank 14 & 15的相关管脚设置(Master SPI)

3.3、FPGA与外设电平匹配(★)

3.4、FPGA中HP的DCI功能(★)

对于7系列FPGA,DCI技术只用在HP I/O bank,对HR I/O bank并不适用。

Xilinx DCI使用两个复用管脚来调整驱动器的阻抗或者并联终端电阻。这两个管脚分别是VRN和VRP。

VRN必须通过一个参考电阻Rref上拉到VCCO,而VRP则必须通过一个参考电阻Rref下拉到地。这个Rref的阻值一般等于PCB走线的特征阻抗或者是这个阻抗的2倍。