写在前面:在STM32F103中有众多的定时器,其中包括两个基本定时器,基本定时器的内容已经在上节进行了介绍,基本定时器的功能、结构、使用都较为简单。而STM32F1中还含有4个通用定时器(TIM2\3\4\5),这些定时器相互独立,不共享资源。本节我们来学习通用定时器的基本使用。

一、通用定时器

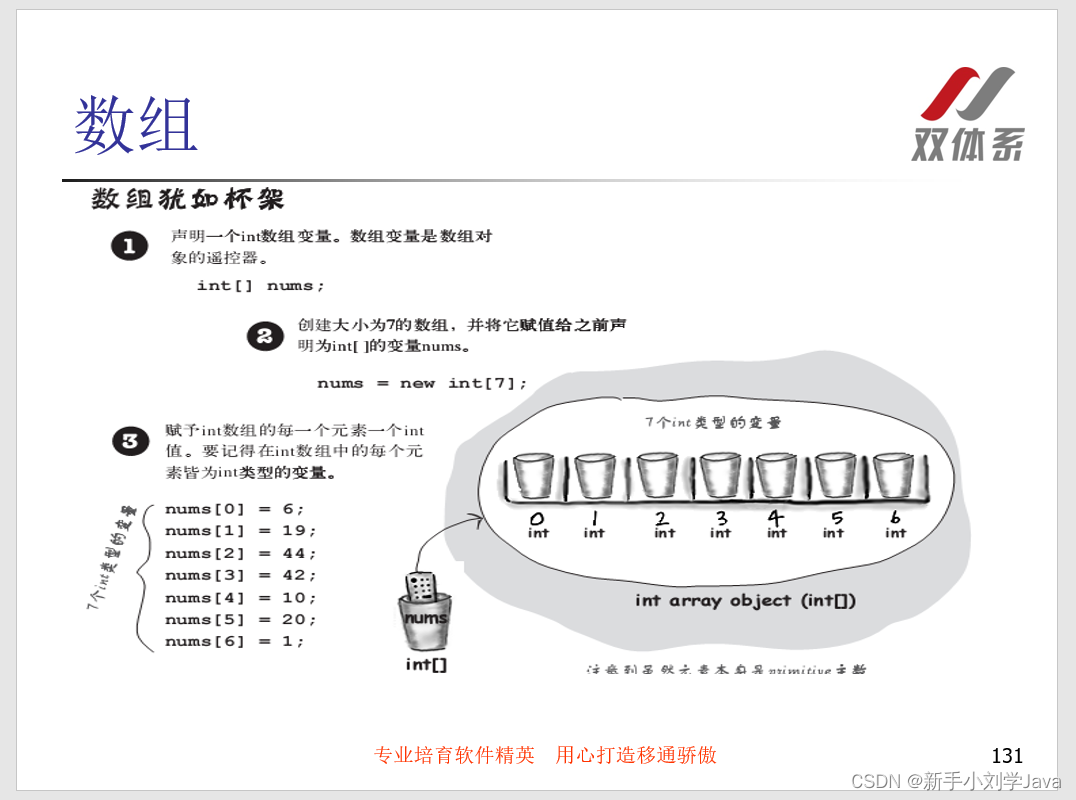

基本定时器回顾:CSDN

1.1 定时器简介

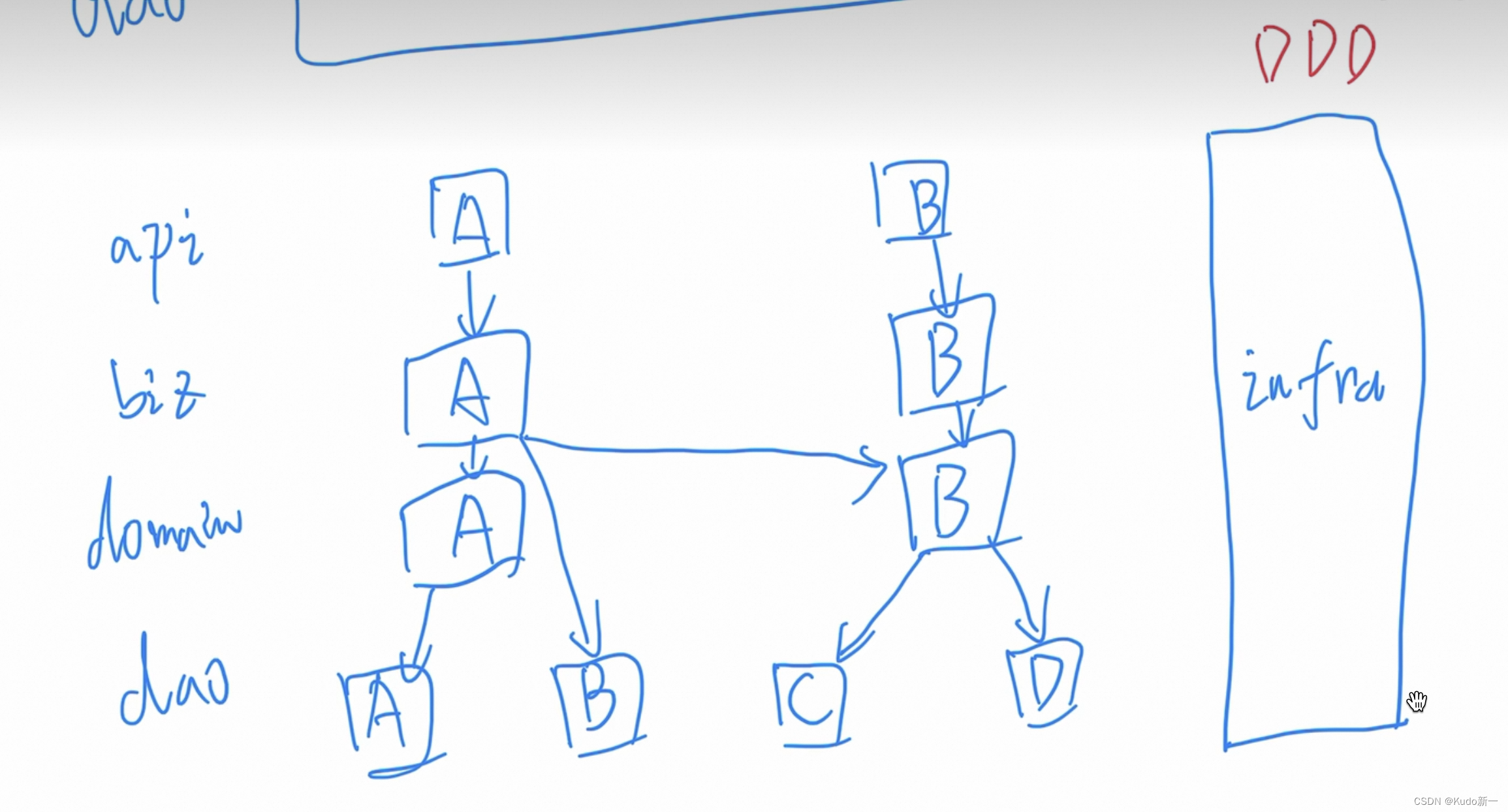

上图为通用定时器与基本、高级定时器的基本区别;其中主要的特性是:

1、含有16位递增、递减、中心对齐的计数器;

2、含有16位预分频器,分频系数为1-65536;

3、可用于触发DAC、ADC事件;

4、在更新事件、触发事件、输入捕获、输出比较中可以产生中断以及DMA请求;

5、含有4个独立通道,用于输入捕获、输出比较 、输出PWM波形以及单脉冲模式。

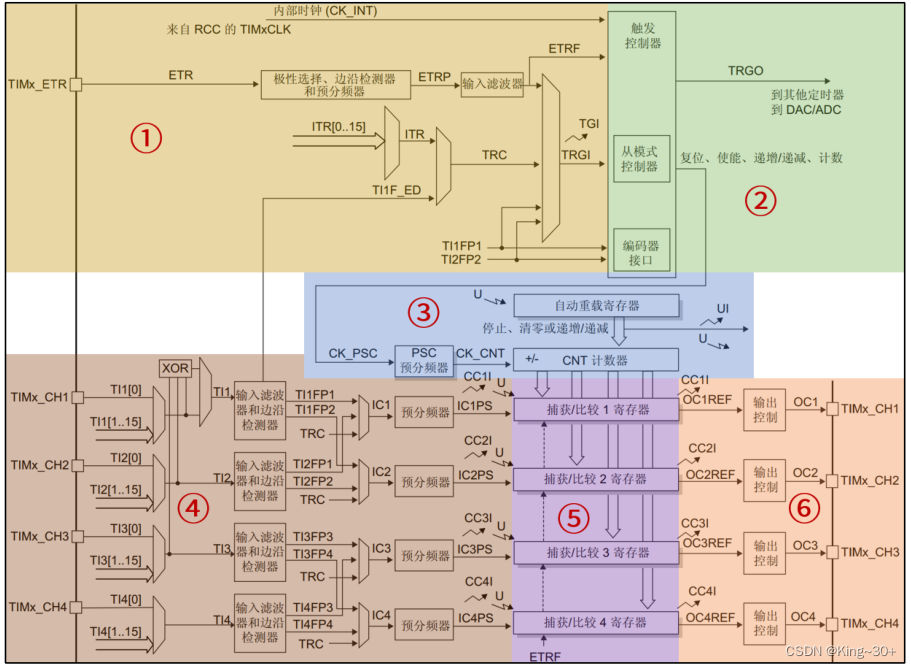

1.2 定时器结构框图

如上图所示,为STM32F1中通用定时器的结构框架,其结构相对于基本定时器来说就很复杂,可能第一眼就很厌烦。但是我们将核心抓住,然后分模块化的进行学习,将一一进行消化。手带你我们看第三部分:也就是图中蓝色区域,我们细心看可以发现,其结构就是基本定时器的结构,这样就只剩下五部分学习了:先对五部分进行简单介绍,后面在细细进行学习;

1、时钟源

与基本定时器(只能来自内部时钟)不同的是:

通用定时器时钟可以选择下面四类时钟源之一:

1)内部时钟(CK_INT)

2)外部时钟模式 1:外部输入引脚(TIx),x=1,2(即只能来自于通道 1 或者通道 2)

3)外部时钟模式 2:外部触发输入(ETR)

4)内部触发输入(ITRx):使用一个定时器作为另一定时器的预分频器

2、控制器

控制器包括:从模式控制器、编码器接口和触发控制器(TRGO)。从模式控制器可以控制计数器复位、启动、递增/递减、计数。编码器接口针对编码器计数。触发控制器用来提供触发信号给别的外设,比如为其它定时器提供时钟或者为 DAC/ADC 的触发转换提供信号。

3、时基单元

与基本定时相同,主要的作用就是进行计数,在来自第一部分的时钟信号下,计数器以(递增、递减、中心对齐) 的方式进行计数,然后同自动重装载寄存器进行比较,产生事件或中断。

4、输入捕获

一般应用是要和第5部分一起完成测量功能。TIMx_CH1~ TIMx_CH4 表示定时器的 4 个通道,这 4 个通道都是可以独立工作的。IO 端通过复用功能与这些通道相连。配置好 IO 端口的复用功能后,将需要测量的信号输入到相应的IO 端口,输入捕获部分可以对输入的信号的上升沿,下降沿或者双边沿进行捕获,常见的测量有:测量输入信号的脉冲宽度、测量 PWM 输入信号的频率和占空比等。

5、输入捕获与输出比较共同部分

6、输出比较

输出比较,一般应用是要和第⑤部分一起完成定时器输出功能。TIMx_CH1~ TIMx_CH4 表示定时器的 4 个通道,这 4 个通道都是可以独立工作的。IO 端口通过复用功能与这些通道相连。

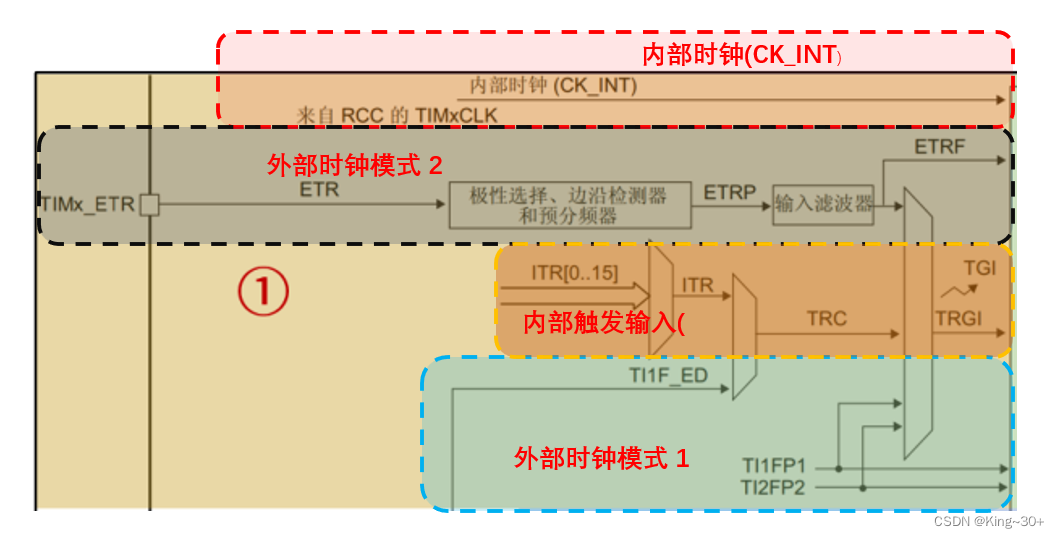

二、时钟源介绍

2.1 内部时钟

同基本定时器相同,TIM2-TIM6都是过载在APB1总线上,我们知道APB1总线的时钟频率是32MHz,但是这些定时器的时钟并不是由APB1直接提供的,而是经过了一个倍频器,APB1 总线时钟频率为 36MHz,APB1 预分频器的预分频系数为 2,所以这些定时器时钟源频率为 72MHz。一般情况下,我们都是用的内部时钟,所以内部时钟也是最重要的部分。

2.2外部时钟模式1

外部时钟模式 1 这类时钟源,顾名思义时钟信号来自芯片外部。时钟源进入定时器的流程

如下:外部时钟源信号→IO→TIMx_CH1(或者 TIMx_CH2),这里需要注意的是:外部时钟模

式 1 下,时钟源信号只能从 CH1 或者 CH2 输入到定时器,CH3 和 CH4 都是不可以的。从 IO

到 TIMx_CH1(或者 TIMx_CH2),就需要我们配置 IO 的复用功能,才能使 IO 和定时器通道相

连通。

输入捕获滤波器: 由 ICF[3:0]位来设置滤波方式,也可以设置不使用滤波器,用于完善输入的信号。

边沿检测器:由 CC2P 位来设置检测的边沿,可以上升沿或者下降沿检测; TI1F_ED未经过CC2P即为双边沿检测。

触发选择:TS[4:0]位来选择 TRGI(触发输入信号)的来源, TI1F_ED、TI1FP1 和 TI2FP2 三个触发输入信号(TRGI)。前两个来自通道1,第三个来自通道2.

从模式选择:由 ECE 位和 SMS[2:0]位来选择定时器的时钟源。这里我们选择的是外部时钟模式1。

2.2 外部时钟模式2

外部时钟模式 2,顾名思义时钟信号来自芯片外部。时钟源进入定时器的流程如下:外部

时钟源信号→IO→TIMx_ETR。从 IO 到 TIMx_ETR,就需要我们配置 IO 的复用功能,才能使

IO 和定时器相连通。

外部触发极性: ETP 位来设置上升沿有效还是下降沿有效,选择下降沿有效的话,信号会经过反相器。

外部触发预分频器:ETPS[1:0]位来设置预分频系数,系数范围:1、2、4、8。例如:分频系数为2,则由io口来两个边沿信号,才能触发一次,一般情况下都是选择为1.

滤波器:ETF[3:0]位来设置滤波方式,也可以设置不使用滤波器。作用同上面的一样。

从模式选择器:由 ECE 位和 SMS[2:0]位来选择定时器的时钟源。这里我们介绍的是外部时钟模式 2,直接将ECE设置为1即可。

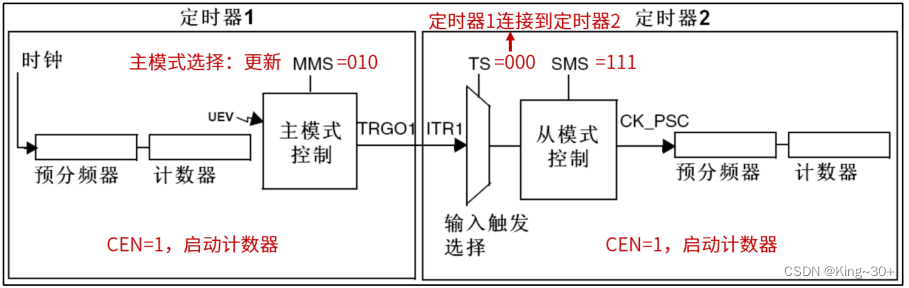

2.3内部触发输入

内部触发输入是使用一个定时器作为另一个定时器的预分频器,即实现定时器的级联。下

面以 TIM1 作为 TIM2 的预分频器。

三、时基单元

与基本定时器结构一样,时基单元包括:计数器寄存器(TIMx_CNT)、预分频器寄存器(TIMx_PSC)、自动重载寄存器(TIMx_ARR)。

不同点是:通用定时器的计数模式有三种:递增计数模式、递减计数模式和中心对齐模式;

TIM2 和 TIM5 的计数器是 32 位的。

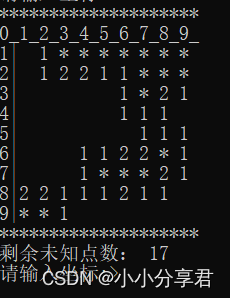

递增计数:每来一个 脉冲,计数器的值就会递增加 1。当计数器值与自动重装载寄存器的设定值相等时,计数器的值就会被自动清零并且会生成更新事件,然后下一个 脉冲到来,计数器的值的值就会递增加 1,如此循环。

递增计数:来了一个计数脉冲,计数器就减 1,直到计数器寄存器的值减到 0,减到 0 时定时器溢出,由于是递减计数,故而称为定时器下溢,定时器溢出就会伴随着更新事件的发生。

中心对齐模式:计数器先从 0 开始递增计数,直到计数器的值等于自动重载寄存器影子寄存器的值减 1 时,定时器上溢,同时生成更新事件,然后从自动重载寄存器影子寄存器的值开始递减计算,直到计数值等于 1 时,定时器下溢,同时生成更新事件,然后又从 0 开始递增计数,依此循环。

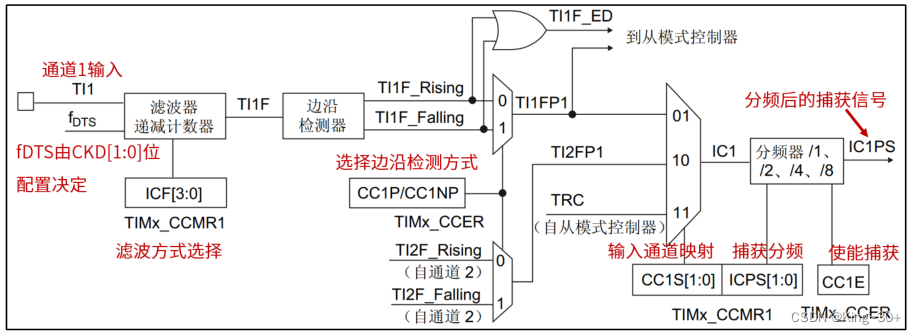

四、输入捕获

输入捕获是要同第5部分一起完成输入捕获实验,其中输入捕获含有CH1-CH4四个定时器入口,这四个入口是可以独立工作的,IO端通过复用工作模式与入口相连,将需要检测的信号输入对应的IO端口,输入捕获部分可以对信号的上升沿、下降沿以及双边沿进行捕获。

捕获的原理在于:信号的输入———上升、下降、双边沿检测极性——计数器的值锁存到相应的捕获/比较寄存器,最后通过捕获比较寄存器的差值计算信号高低电平的时间。

滤波器: 由 ICF[3:0]位来设置滤波方式,也可以设置不使用滤波器;

边沿检测器:由 CC1P 位来设置检测的边沿,可以上升沿或者下降沿检测。

输入捕获映射选择器:由 CC1S[1:0]位来选择把 IC1 映射到 TI1、TI2 还是 TRC。

输入捕获 1 预分频器:由 ICPS[1:0]位来设置预分频系数,范围:1、2、4、8。

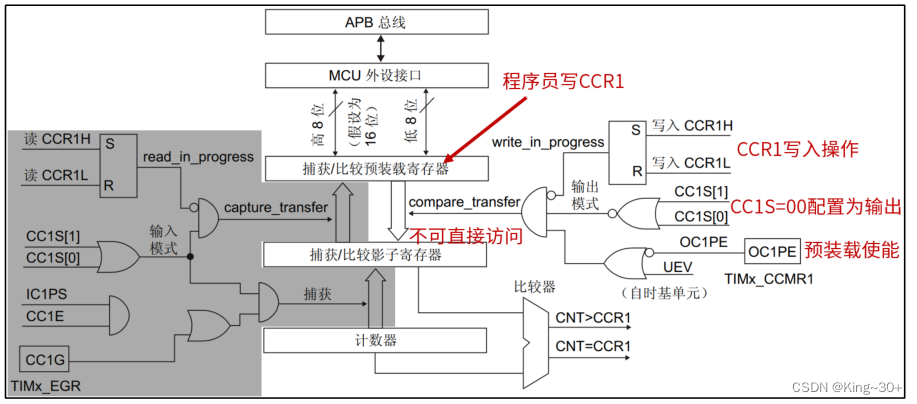

上图为第5部分输入捕获和输出比较公用部分,我们目前只看输入捕获相关的即白色部分:由下到上,分别是计数器——捕获/比较影子寄存器——捕获/比较预装载寄存器。其中当第4部分的捕获输入满足条件后,计数器的值进入影子寄存器,再满足某些条件,影子寄存器的值进入捕获/比较预装载寄存器,最后我们读取存储在预装载寄存器中的值进行处理。

五、输出比较

输出比较一般是同第5部分相结合使用的,也是通过CH41-CH4进行输出工作的,那我们就有个矛盾,第4部分的输入捕获与第6部分的输出比较用的是相同的通道,连接的是相同的IO口,那么能一起工作吗?显然是不行的。就是说要么执行输入捕获的功能,要么执行输出比较的功能,而且共用第5部分,也就是说第5部分一时间只能被共用一个。

输出:顾名思义是由通道向外部输出电平信号;

比较:顾名思义是经过比较后产生信号。

上图为输出比较同第5部分相结合的放大图,这次我们由上往下看,首先是捕获/比较预装载寄存器,我们直接设定里面的值,然后在某种情况下,将预装载寄存器的值转至影子寄存器,影子寄存器的值同计数器进行比较,他们的比较结果将输出至第六部分进行处理。

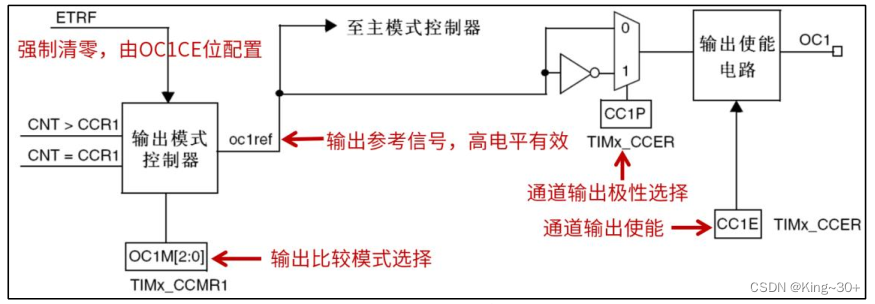

通过比较后,进入输出模式控制器: oc1ref 是输出参考信号,高电平有效,为高电平时称之为有效电平,为低电平时称之为无效电平。它的高低电平受到三个方面的影响:OC1M[3:0]位配置的输出比较模式、第⑤部分比较器的比较结果、还有就是 OC1CE 位配置的 ETRF 信号。ETRF 信号可以将 Oc1ref 电平强制清零,该信号来自 IO 外部。

CC1P 位用于选择通道输出极性。

CC1E 位置 1 使能通道输出。

OC1 信号就会从 TIMx_CH1 输出到 IO 端口,再到 IO 外部。

以上便是本节的内容,理论性较强,也是学会使用通用定时器的基本,大家可以多看几遍,熟悉其中的原理,在用的时候知道工作的流程即可。下节我们将针对相关的理论进行实验验证。

创作不易,还希望大家多多点赞支持!!!