目录

1.前言

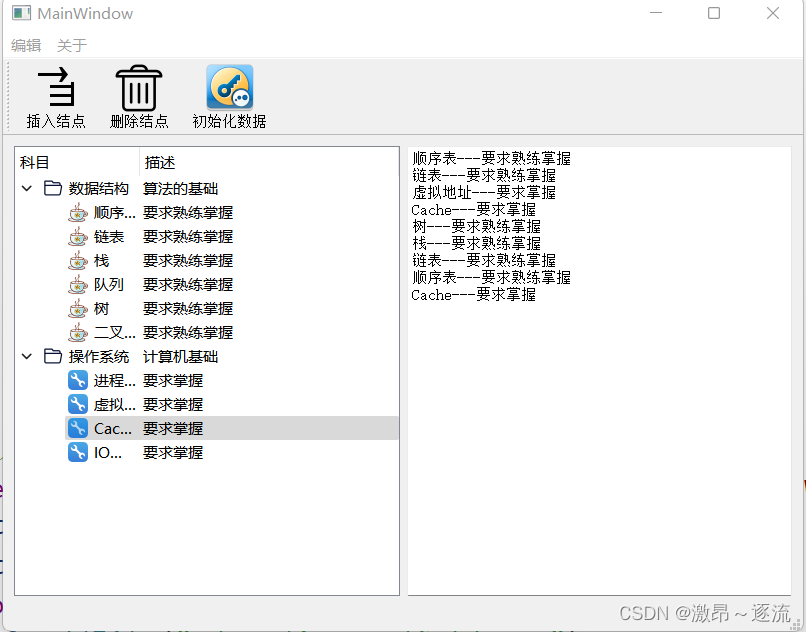

2.回顾之前的设计

3.基于读者思路的设计

4.ModelSim仿真

1.前言

昨天分享的关于FPGA对机械按键消抖的设计,有读者指出了其中的不足,并给出了他的思路。今天就读者的设计思路,来再做一个按键消抖模块。这个程序大概是大学的时候写的,当时才开始学,没考虑那么多。现在开始写博客,才陆续把以前写过的东西翻出来、分享。首先感谢这位读者,给我提出意见,学习的时候就是要多互相交流才能进步。大家对文章有问题,欢迎来和我讨论。

2.回顾之前的设计

之前的按键消抖模块链接

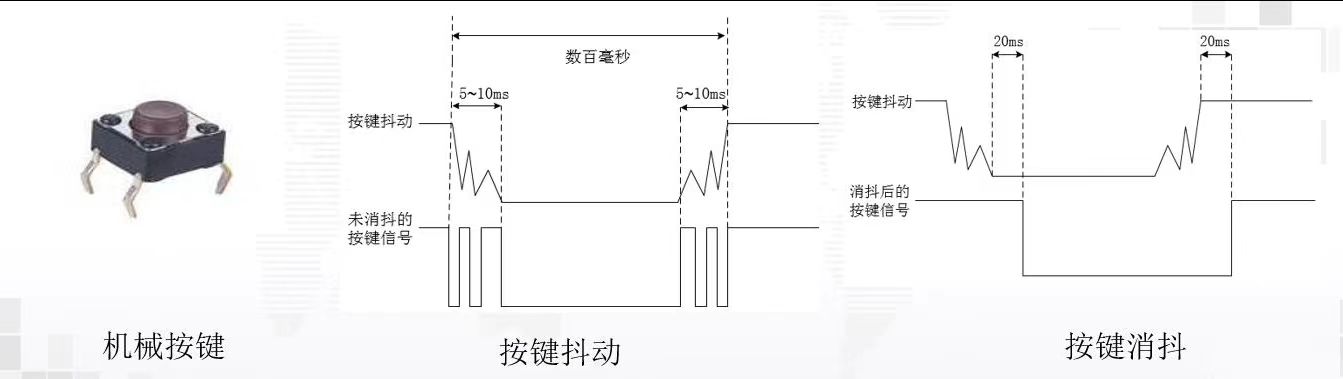

之前的设计思路是,在检测到按键稳定时,延迟20ms再进行采样,然后得到稳定的按键信号。但是有读者说了,这样处理,按下去至少20ms才会生效,对于年轻人来说可能会明显的感觉到延迟,这样设计似乎更适合老年人哈哈哈哈。不过,该方法的一个好处就是,获取的按键值是稳定后的,可以避免一些误触,或者由于抖动之类的导致按键闭合,影响判断。

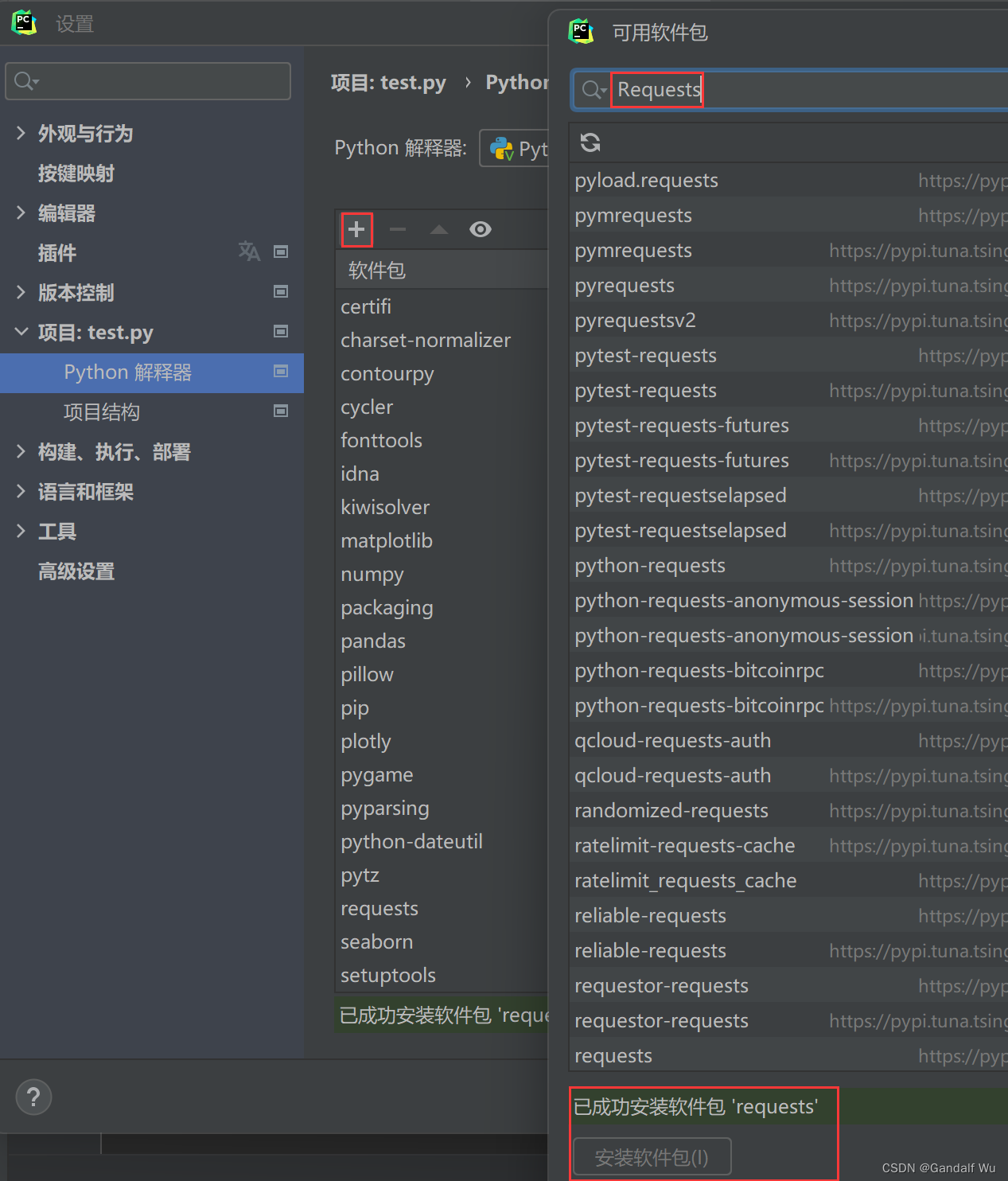

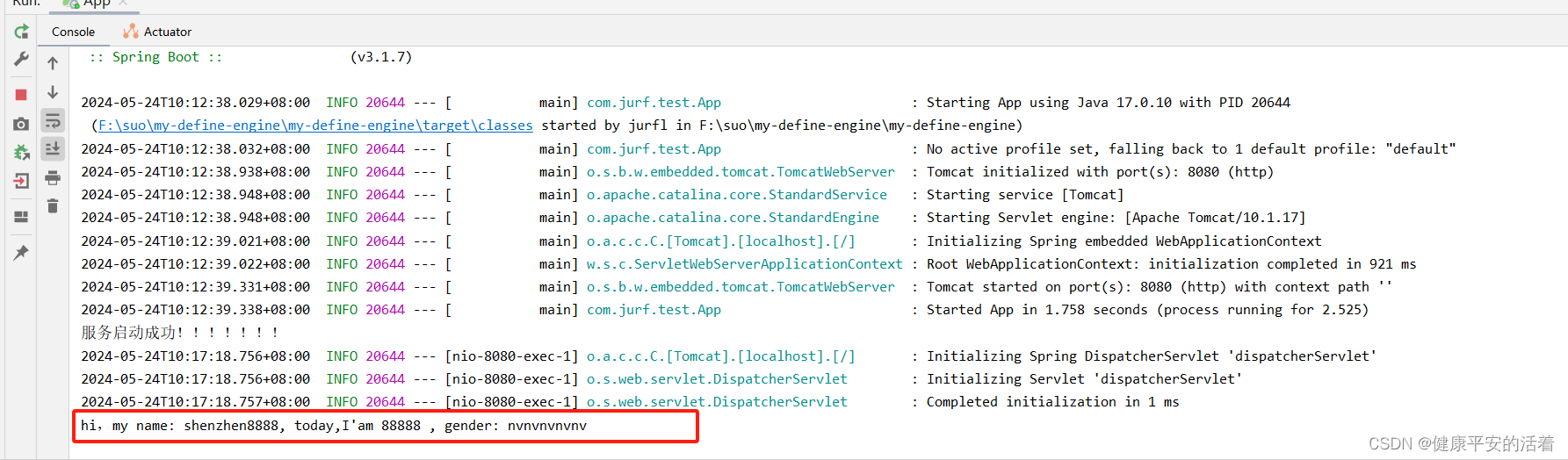

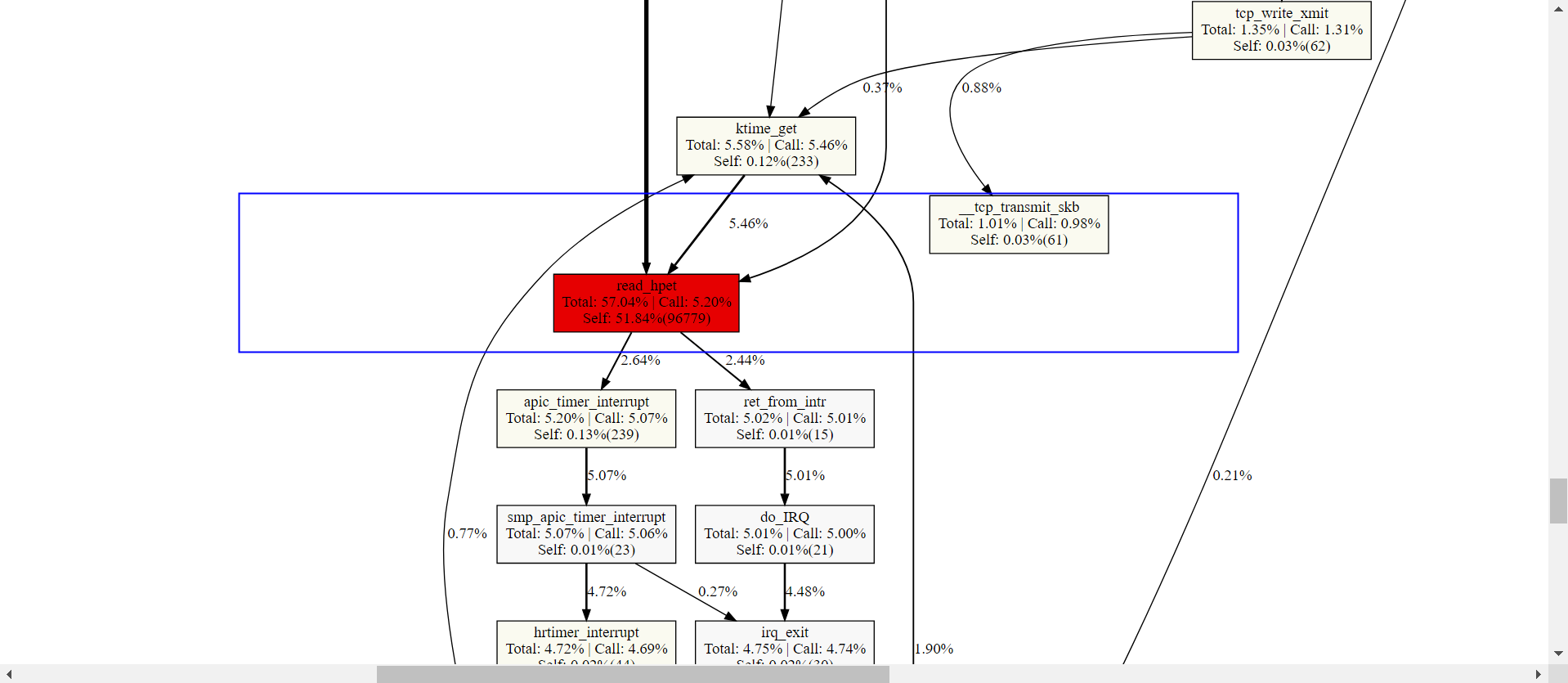

之前设计的消抖模块如下图所示,如果把延迟时间设置为5ms,一方面迟滞感就不会那么强,另一方面按键也还是稳定了一段时间才进行采样,避免了亚稳态。具体延迟时间可能要根据需求去设置,思路是这么个思路。

按键消抖过程

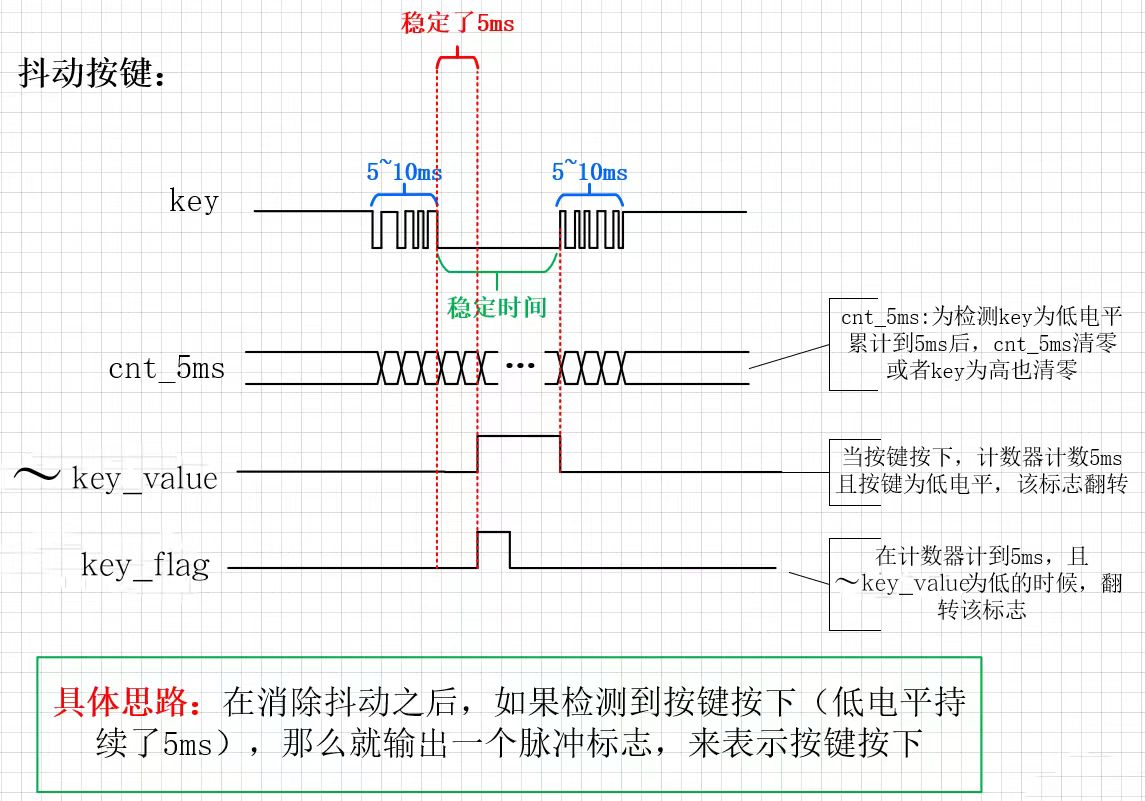

3.基于读者思路的设计

(1)在检测到按键按下时,按键即刻生效,输出一个时钟高电平脉冲。

(2)按键生效时,设置一个标志位;并开始计时20ms

(3)在计时没有完成之前,对按键作输入无效处理。

(4)计时结束,更改标志位状态,按键输入重新有效。

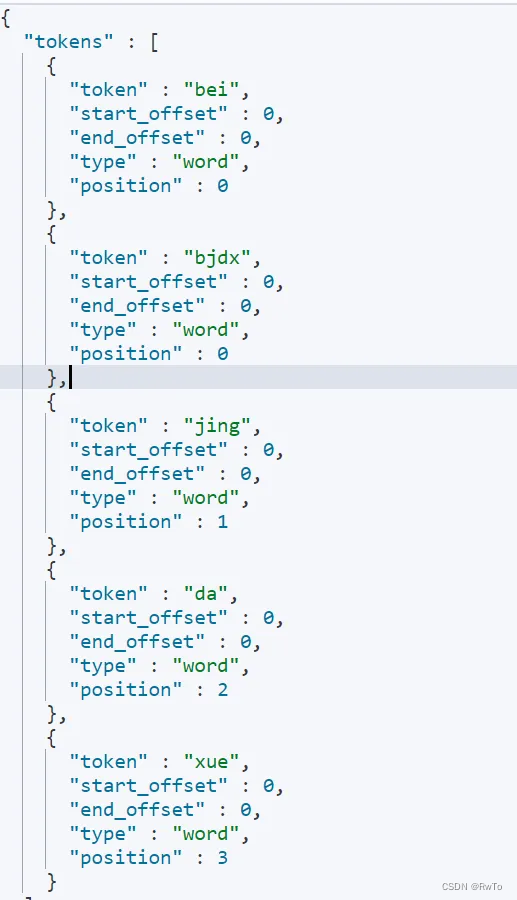

代码如下:

`timescale 1ns / 1ps

module key_debounce #(parameter DELAY_CNT = 'd1_000_000)//50M时钟时的20ms计数值

( //防抖模块端口声明input clk ,//50Minput rst_n ,input key , //定义按键输入output key_out //定义按键输出

);wire key_edge_pluse ;

wire [$clog2(DELAY_CNT) - 1:0] cnt ;

wire cnt_last ;

reg key_flag ;edge_detection #(.POSEDGE(1'b0))

u_edge_detection (.clk (clk ), .edge_din (key ),.edge_pluse (key_edge_pluse )

);assign key_out = key_edge_pluse & ~key_flag;always @ (posedge clk or negedge rst_n) beginif (!rst_n) key_flag <= 1'b0;else if(key_edge_pluse)key_flag <= 1'b1;//检测到按键按下后,在计数结束前后续按键值无效else if(cnt_last)key_flag <= 1'b0;

endcounter #(.CNT_NUM(DELAY_CNT),.ADD(1'b1))

u_counter(.clk (clk ), .rst_n (rst_n ),.En_cnt (key_flag ), .cnt (cnt ), .cnt_last (cnt_last )

);

endmodule其中使用到的计数器模块和边沿检测请参考之前的设计。

FPGA搭积木之计数器

FPGA搭积木之边沿检测电路

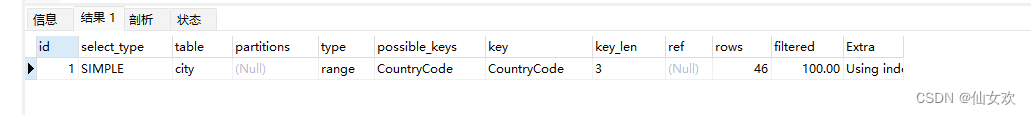

4.ModelSim仿真

`timescale 1ns / 1ps

module key_debounce_tb;

parameter T = 20;

reg clk ;

reg rst_n ;

reg key ;

wire key_out ;key_debounce #(.DELAY_CNT('d2_0))//为了减小仿真时间,将延时减小

u_key_debounce(

.clk (clk ),

.rst_n (rst_n ),

.key (key ),

.key_out(key_out)

);always #(T/2) clk = ~clk;initial beginclk = 1'b0;rst_n = 1'b0;key = 1'b1;#(10*T)rst_n = 1'b1;//模拟按键抖动,实际只有一次按键输入#(T)key = 1'b0;#(T)key = 1'b1;#(T)key = 1'b0;#(3*T)key = 1'b1;#(T)key = 1'b0;#(5*T)key = 1'b1;#(T)key = 1'b0;#(T)key = 1'b1;//模拟第二次按键抖动#(20*T)key = 1'b0;#(T)key = 1'b1;#(2*T)key = 1'b0;#(T)key = 1'b1;#(T)key = 1'b0;#(5*T)key = 1'b1;#(T)key = 1'b0;#(T)key = 1'b1;end

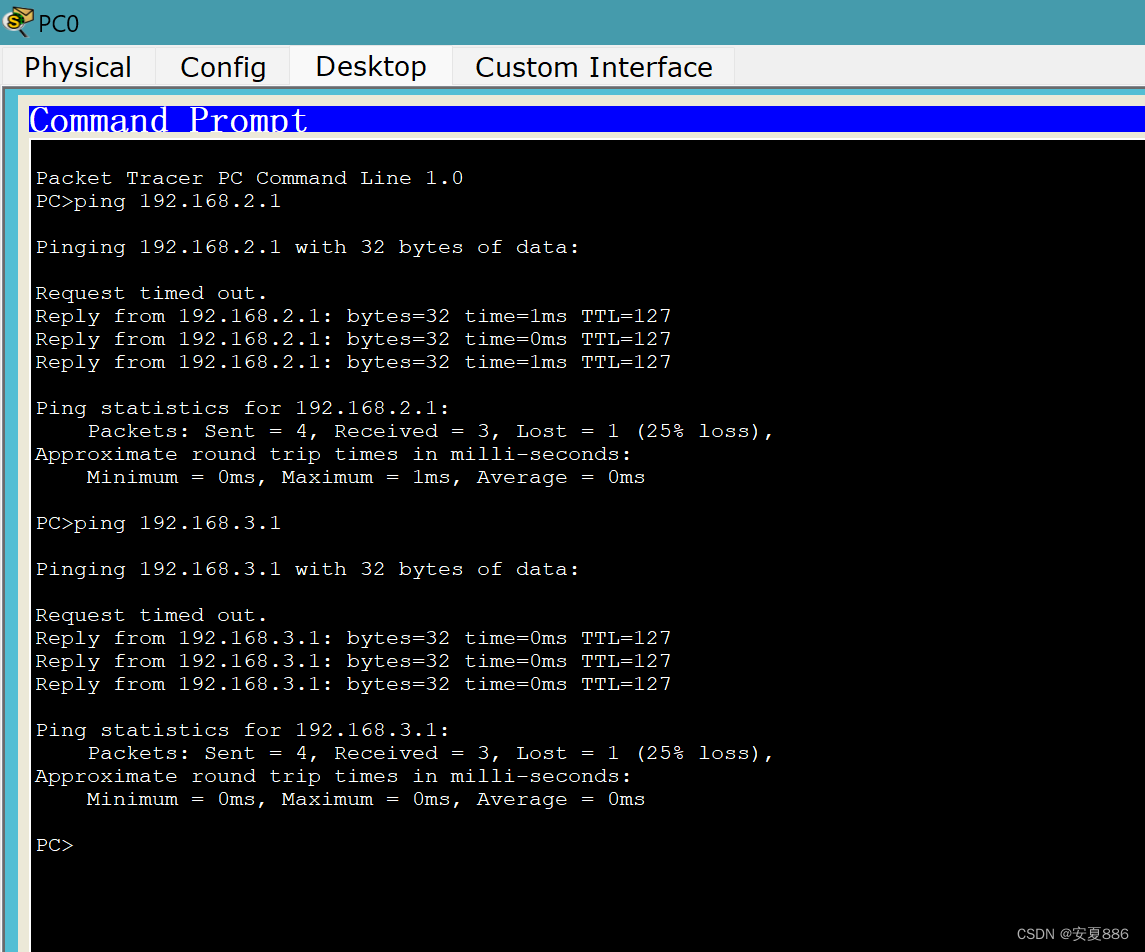

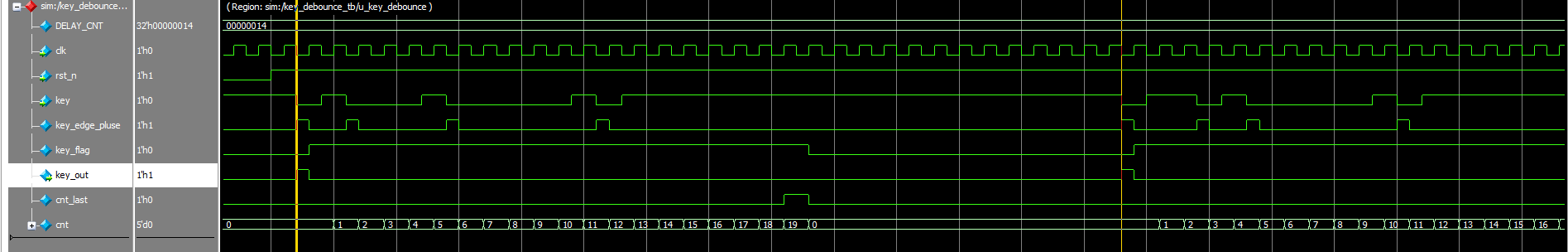

endmodule为了减小仿真时间,例化按键消抖模块时,将延时计数器值改小,方便验证逻辑。然后模拟两次按键输入。

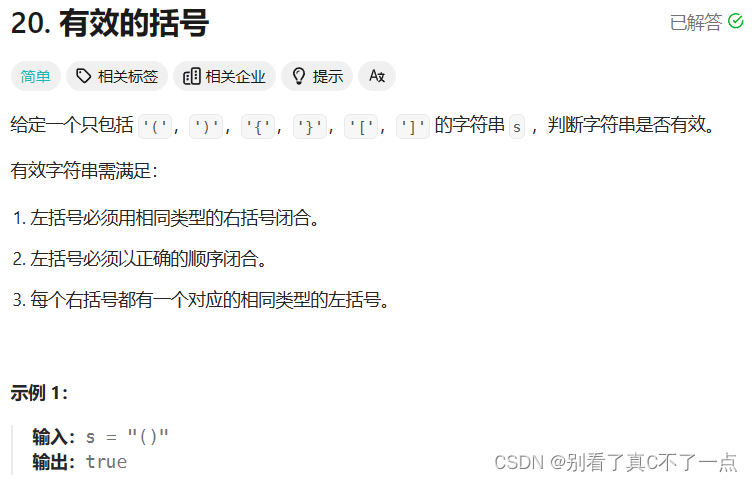

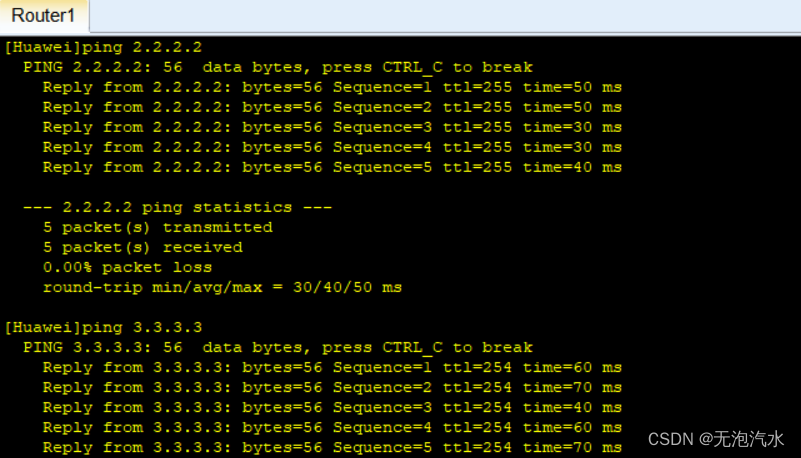

仿真

从仿真波形可以看到,只输出了两次按键值。 将设计参数化,放入自己的代码库,供有需要时直接使用。相比于官方提供的封闭的IP核,自己设计的IP核虽然性能比不过,但是更灵活,方便进行个性化修改。FPGA其实就像搭积木一样,只要自己的代码库够丰富,设计只会越来越轻松! 此合集持续分享一些笔者自己设计的可复用硬件模块:FPGA搭积木