CIC滤波器结构简单,没有乘法器,只有加法器、积分器和寄存器,适合工作在高抽样率条件下,而且CIC滤波器是一种基于零点相消的FIR滤波器。

CIC滤波器分为单级和多级滤波器。

1.在单极滤波器中:

当CIC滤波器的长度M远大于1时,第一旁瓣电平相对于主瓣电平的差值几乎是固定的13.46dB。显然这样小的阻带衰减远不能满足较高的CIC滤波器要求。

要想阻带衰减满足高的CIC滤波器要求,是对CIC滤波器进行级联,每增加一级滤波器,则第一旁瓣电平衰减增加13.46dB。例如采用5级CIC滤波器级联,则第一旁瓣电平衰减变为67.3dB

单级CIC滤波器实现的matlab代码:

%用Matlab仿真不同长度的单级CIC滤波器的频谱特性。M=2; %滤波器长度

b=ones(1,M);

delta=[1,zeros(1,1023)];

s=filter(b,1,delta); %求取滤波器冲激响应

Spec=20*log10(abs(fft(s))); %求取滤波器频谱特性

Spec2=Spec-max(Spec);

f=0:length(Spec)-1;

f=2*f/(length(Spec)-1); %对频率轴进行归一化处理M=5; %滤波器长度

b=ones(1,M);

delta=[1,zeros(1,1023)];

s=filter(b,1,delta); %求取滤波器冲激响应

Spec=20*log10(abs(fft(s))); %求取滤波器频谱特性

Spec5=Spec-max(Spec);M=7; %滤波器长度

b=ones(1,M);

delta=[1,zeros(1,1023)];

s=filter(b,1,delta); %求取滤波器冲激响应

Spec=20*log10(abs(fft(s))); %求取滤波器频谱特性

Spec7=Spec-max(Spec);M=8; %滤波器长度

b=ones(1,M);

delta=[1,zeros(1,1023)];

s=filter(b,1,delta); %求取滤波器冲激响应

Spec=20*log10(abs(fft(s))); %求取滤波器频谱特性

Spec8=Spec-max(Spec);% plot(f,Spec2,f,Spec5,f,Spec7,f,Spec8);axis([0 1 -50 0]);grid;

% xlabel('归一化频率');ylabel('幅度(dB)');

% legend('M=2','M=5','M=7','M=8');

% grid;

plot(f,Spec2,'-',f,Spec5,'.',f,Spec8,'--');axis([0 1 -50 0]);

xlabel('归一化频率');ylabel('幅度(dB)');

legend('M=2','M=5','M=8');

grid;2.多级CIC滤波器:

matlab代码:

%用Matlab仿真不同长度的5级CIC滤波器的频谱特性。M=2; %滤波器长度

b=ones(1,M);

delta=[1,zeros(1,1023)];

s1=filter(b,1,delta); %求取滤波器冲激响应

s2=filter(b,1,s1); %求取滤波器冲激响应

s3=filter(b,1,s2); %求取滤波器冲激响应

s4=filter(b,1,s3); %求取滤波器冲激响应

s=filter(b,1,s4); %求取滤波器冲激响应

Spec=20*log10(abs(fft(s))); %求取滤波器频谱特性

Spec2=Spec-max(Spec);

f=0:length(Spec)-1;

f=2*f/(length(Spec)-1); %对频率轴进行归一化处理M=5; %滤波器长度

b=ones(1,M);

delta=[1,zeros(1,1023)];

s1=filter(b,1,delta); %求取滤波器冲激响应

s2=filter(b,1,s1); %求取滤波器冲激响应

s3=filter(b,1,s2); %求取滤波器冲激响应

s4=filter(b,1,s3); %求取滤波器冲激响应

s=filter(b,1,s4); %求取滤波器冲激响应

Spec=20*log10(abs(fft(s))); %求取滤波器频谱特性

Spec5=Spec-max(Spec);M=7; %滤波器长度

b=ones(1,M);

delta=[1,zeros(1,1023)];

s1=filter(b,1,delta); %求取滤波器冲激响应

s2=filter(b,1,s1); %求取滤波器冲激响应

s3=filter(b,1,s2); %求取滤波器冲激响应

s4=filter(b,1,s3); %求取滤波器冲激响应

s=filter(b,1,s4); %求取滤波器冲激响应

Spec=20*log10(abs(fft(s))); %求取滤波器频谱特性

Spec7=Spec-max(Spec);M=8; %滤波器长度

b=ones(1,M);

delta=[1,zeros(1,1023)];

s1=filter(b,1,delta); %求取滤波器冲激响应

s2=filter(b,1,s1); %求取滤波器冲激响应

s3=filter(b,1,s2); %求取滤波器冲激响应

s4=filter(b,1,s3); %求取滤波器冲激响应

s=filter(b,1,s4); %求取滤波器冲激响应

Spec=20*log10(abs(fft(s))); %求取滤波器频谱特性

Spec8=Spec-max(Spec);% plot(f,Spec2,f,Spec5,f,Spec7,f,Spec8);axis([0 1 -50 0]);grid;

% xlabel('归一化频率');ylabel('幅度(dB)');

% legend('M=2','M=5','M=7','M=8');

% grid;

plot(f,Spec2,'-',f,Spec5,'.',f,Spec8,'--');axis([0 1 -200 0]);

xlabel('归一化频率');ylabel('幅度(dB)');

legend('M=2','M=5','M=8');

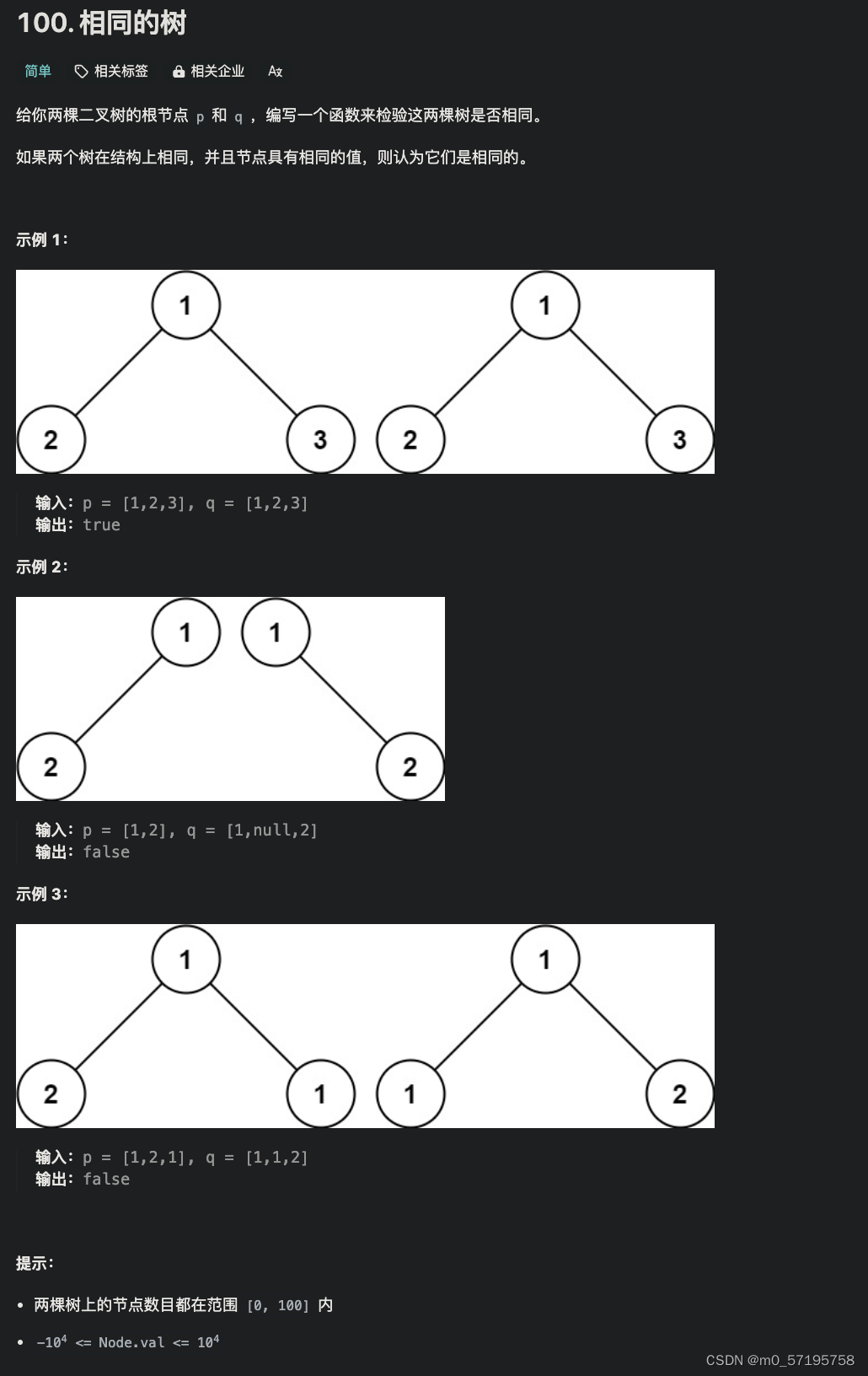

grid;3.CIC滤波器的应用条件

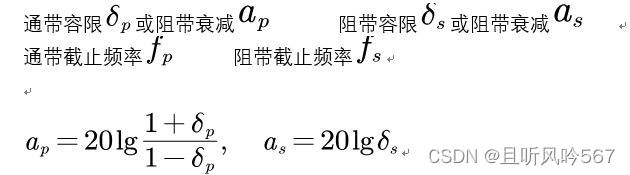

CIC滤波器的频谱形状是相似的,在给定过渡带的情况下,通带容限与阻带容限的取值只与CIC滤波器的阶数及级数有关。对于单级CIC滤波器来说,其对应关系为:

对于多级CIC滤波器(设级数为n)来说,各级CIC滤波器的误差容限与系统总误差容限的关系为;

4.单级CIC滤波器的FPGA设计

抽取倍数为5,采用5阶CIC滤波器

module SigCIC(input rst,input clk,input signed[9:0] din,output rdy,output signed[12:0] dout

);reg rdy_tem;reg[2:0] c;reg signed[12:0] tem;reg signed[12:0] dout_tem;always @(posedge clk or posedge rst) beginif (rst) beginc <= 3'd0;tem <= 13'd0;dout_tem <= 13'd0;rdy_tem <= 1'b0;endelsebeginif (c==4) beginrdy_tem <= 1'b1;dout_tem <= tem + din;c = 3'd0;tem = 13'd0;endelsebeginrdy_tem <= 1'b0;tem = tem + din;c = c + 1;endendendassign dout = dout_tem;assign rdy = rdy_tem;endmodule5.多级CIC滤波器的FPGA实现

(1)Noble恒等式

具体到多速率信号处理系统,如果线性系统后面紧跟着M倍抽取滤波器,则下列公式成立:

表明调换线性系统的抽取系统的处理顺序,即首先进行抽取,然后进行线性滤波,这样可以将线性滤波器的长度降低到1/M,即滤波器的抽头数为原来的1/M

(2)多级滤波器的输出字长

为输出数据位数,

为输入数据位数, N为滤波器阶数, D为滤波器级联数量

假设设计的滤波器为5阶3级CIC滤波器,输入数据位数为10bit。

则整个系统的输出数据位数为17bit,并且多级CIC滤波器的中间运算位数也为17bit。

(3)Verilog编写

将程序分成3个模块来进行编写:积分模块(Integrated)、抽取模块(Decimate)和梳状模块(Comb)和顶层模块。

积分模块(Integrated)

module Integrated(input rst,input clk,input signed[9:0] Xin,output signed[16:0] Intout

);wire signed[36:0] I1,I2,I3;reg signed[36:0] d1,d2,d3;//第一级积分器always @(posedge clk or posedge rst) beginif(rst)d1 <= 37'd0;elsed1 <= I1;endassign I1 = (rst ? 37'd0 : (d1+{{27{Xin[9]}},Xin}));//第二级积分器always @(posedge clk or posedge rst) beginif(rst)d2 <= 37'd0;elsed2 <= I2;endassign I2 = (rst ? 37'd0 : (I1+d2));//第三级积分器always @(posedge clk or posedge rst) beginif(rst)d3 <= 37'd0;elsed3 <= I3;endassign I3 = (rst ? 37'd0 : (I2+d3));assign Intout = I3[16:0];endmodule抽取模块(Decimate)

module Decimate(input rst,input clk,input signed[16:0] Iin,output signed[16:0] dout,output rdy

);reg[2:0] c;reg signed[16:0] dout_tem;reg rdy_tem;always @(posedge clk or posedge rst) beginif(rst)beginc = 3'd0;dout_tem <= 17'd0;rdy_tem <= 1'b0;endelsebeginif (c==4) beginrdy_tem <= 1'b1;dout_tem <= Iin;c = 3'd0;endelsebeginrdy_tem <= 1'b0;c = c+1;endendendassign dout = dout_tem;assign rdy = rdy_tem;endmodule梳状模块(Comb)

module Comb (input rst,input clk,input ND,input signed[16:0] Xin,output signed[16:0] Yout

);reg signed[16:0] d1,d2,d3,d4;wire signed[16:0] C1,C2;wire signed[16:0] Yout_tem;always @(posedge clk or posedge rst) beginif (rst) begind1 <= 17'd0;d2 <= 17'd0;d3 <= 17'd0;d4 <= 17'd0;endelsebeginif (ND) begind1 <= Xin;d2 <= d1;d3 <= C1;d4 <= C2;endendendassign C1 = (rst ? 17'd0:(d1-d2));assign C2 = (rst ? 17'd0:(C1-d3));assign Yout_tem = (rst ? 17'd0:(C2-d4));assign Yout = Yout_tem;endmodule顶层模块

module MultCIC (input rst,input clk,input [9:0] Xin,output [16:0] Yout,output rdy

);wire ND;wire signed[16:0] Intout;wire signed[16:0] dout;Integrated U1(.rst(rst),.clk(clk),.Xin(Xin),.Intout(Intout));Decimate U2(.rst(rst),.clk(clk),.Iin(Intout),.dout(dout),.rdy(ND));Comb U3(.rst(rst),.clk(clk),.ND(ND),.Xin(dout),.Yout(Yout));assign rdy = ND;endmodule参考资料

数字滤波器的FPGA与MATLAB实现