目录

一、前言

二、Datasheet配置选项说明

2.1 Options

2.2 Groups

2.3 Timer Settings

2.4 Common Options

三、Datasheet报告

3.1 General Information

3.2 Input Ports Setup/Hold

3.3 Output Ports Clock-to-out

3.4 Setup between Clocks

3.5 Combinational Delays

3.6 Setup/hold for Input buses

3.7 Max/Min Delays for Output Buses

四、分析路径查看

五、示例代码

六、参考文件

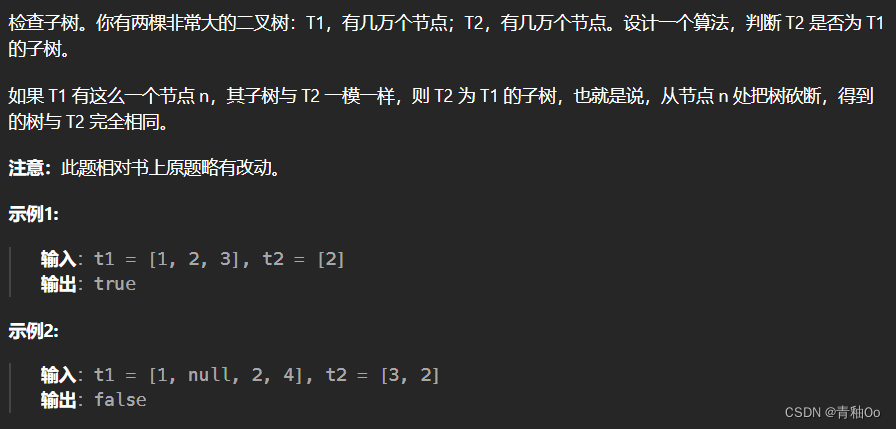

一、前言

时序报告中不仅包含对时序路径的详细信息,还有一类专门针对IO端口的时序报告分析,即“Report->Timing->”里面的Report Datasheet功能,下面将针对Datasheet的内容进行详解,注:本文示例的vivado版本为vivado2022.1,器件为xc7k480tffv1156-2L

二、Datasheet配置选项说明

在执行report datasheet时,会先弹出设置框,主要有三部分内容:Option,Groups,Timer Settings

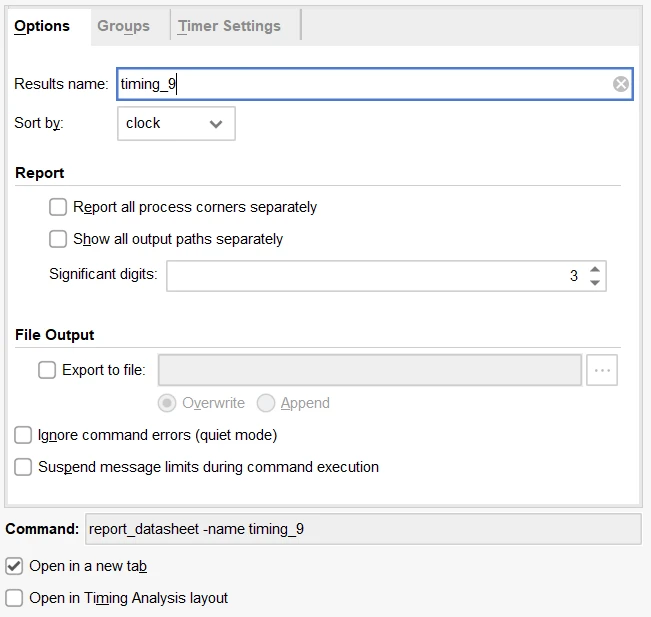

2.1 Options

Results name:设置生成报告的名称,默认格式是timing_id

Sort by:可选值为port,clock,设置报告结果根据端口还是时钟排序

Report all process corners separately:设置是否报告当前设计在所有工艺角下的数据,勾选了即表示允许,默认不勾选

Significant digits:设置报告中数值显示的有效小数位数,默认精度是显示小数点后三位

Write results to file:设置是否将报告结果导出到文件,文件为txt格式,在指定保存文件后,选择Overwrite则覆盖原有的内容,Append则是在文件现有内容后面进行添加,不覆盖原有内容

Ignore command errors:执行命令时忽略命令的错误,直接运行,无任何返回信息

Suspend message limits:勾选后则会忽略信息输出的限制,显示命令执行后所有的信息

2.2 Groups

通过Groups设置,用户可以根据自己的习惯通过指定端口进行分析,未设置时,软件自动地查找启动时钟上的输出端口组以及报告对应时钟上的偏斜

Reference:设置计算偏斜的参考端口,通常是源同步输出端口上的时钟端口

Ports:设置需要报告的端口,通过+或-对应的增加或减少报告的端口,+表示指定多个组,每一个有自己的参考时钟端口,允许用户定义一个新的端口组,-表示从需要的端口组中移除不想报告的端口

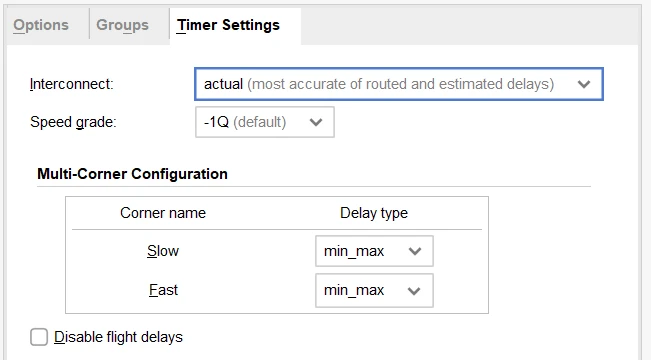

2.3 Timer Settings

Interconnect Setting: 用于设置线延时的计算是基于单元引脚的距离,还是实际布线的距离或者是时序分析时不考虑线延时,对应的选项分别为estimated,actual,none

estimated:对于未布局的单元,线延时值对应最有可能布局位置下的延时,对应的两个未布局单元间的线在时序路径报告中会添加未布局的标签

actual:对于已完成布线后的线,线延时对应实际的硬件线路延时

none:时序报告分析中不考虑连线延时

Speed grade: 设置速率等级

Multi-Corner Configuration Setting:指定时序角上路径延时分析的路径类型,可选值为none,max,min,min_max,设置none则对于指定corner下不进行时序分析

Disable flight delays:勾选后表示不考虑封装延时,封装延时是封装引脚到die pad间的延时

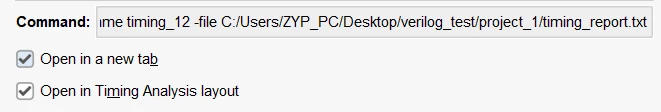

2.4 Common Options

Command:显示对应配置选项设置下的tcl命令

Open in a new tab: 执行一次报告分析时是否在新的tab窗口中打开

Open in Timing Analysis layout:在执行完时序分析后同步打开device窗口

三、Datasheet报告

3.1 General Information

general information主要是设计的基本信息,包括报告类型,设计名称,所属器件,vivado版本,工程运行时间信息与生成报告的命令。

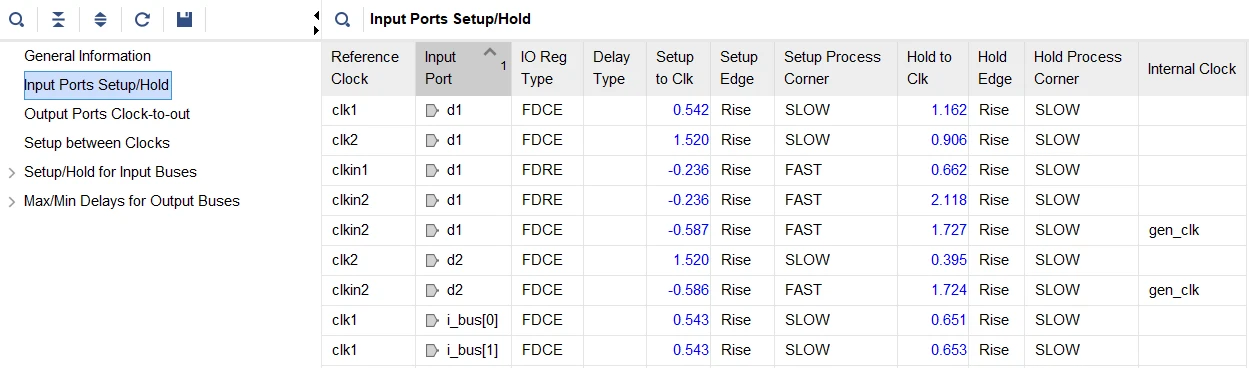

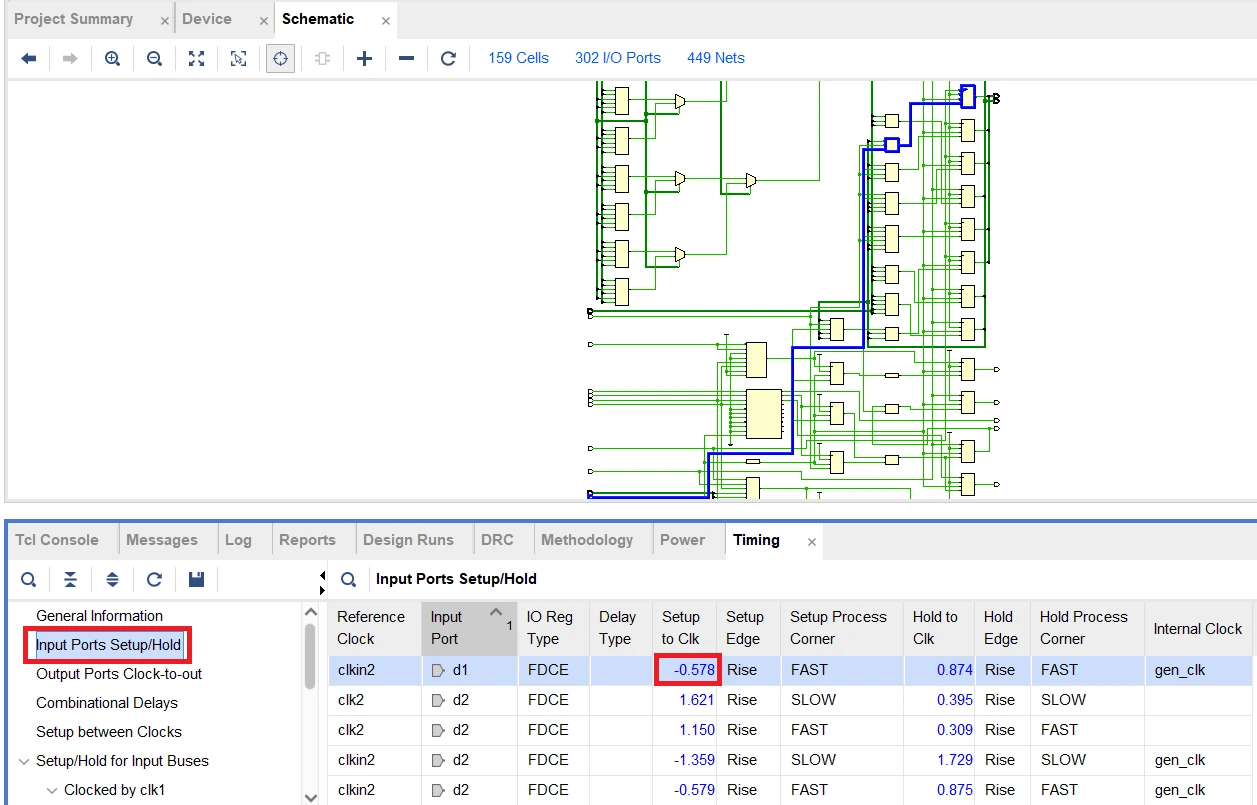

3.2 Input Ports Setup/Hold

Input Ports Setup/Hold显示了每个输入端口在对应的参考时钟下最差的setup,hold时间,用于捕获输入数据的内部时钟也会被分析,当两条或更多的路径存在数据输入端口时,并且和时钟输入相关,则会报告最差的setup/hold时间。

模型场景如下图,与普通的时序路径分析类似,区别是此处只考虑单个触发器内时钟输入与Input端口输入的分析

3.3 Output Ports Clock-to-out

显示每个输出端口在对应参考时钟下最差情况的最大和最小延迟。此外还可报告用于发送输出数据的内部时钟internal clock,也就是在xdc中进行了约束的时钟或者是PLL自动生成的时钟。

其中 IO Reg Type通常为触发器,也可以是PLL等,以触发器为例,分析模型如下图

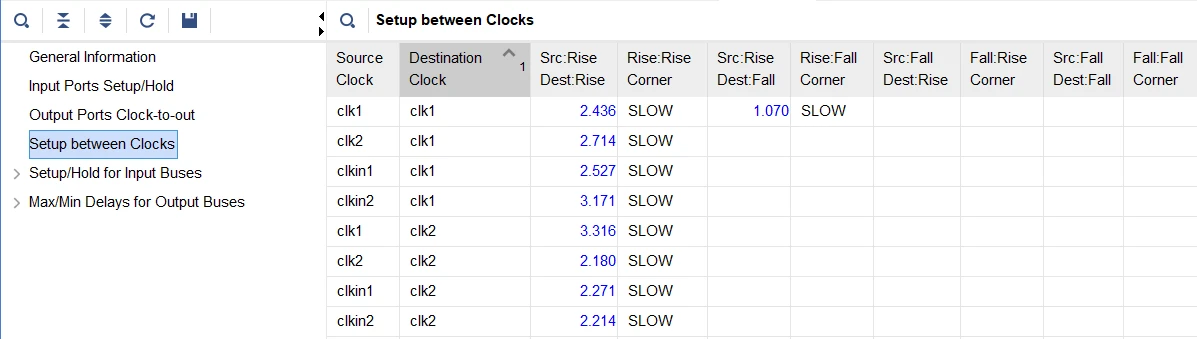

3.4 Setup between Clocks

针对每一对时钟,将报告所有时钟沿组合的最差情况建立时间要求。

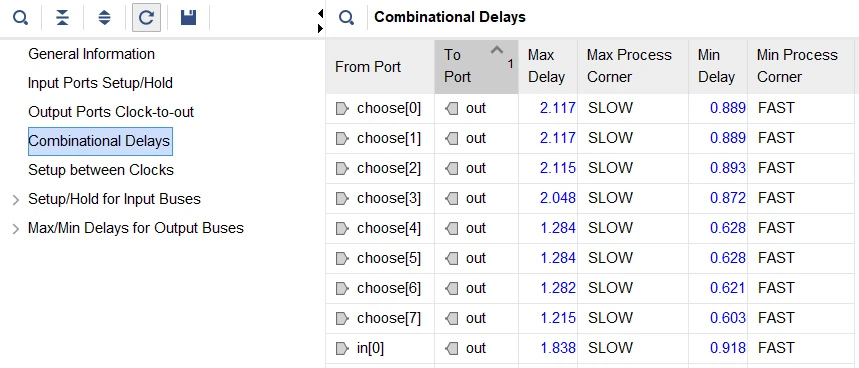

3.5 Combinational Delays

对于输入端口到输出端口间如果只有组合逻辑,无时序单元,在combinational delays中会分析不同corner的

3.6 Setup/hold for Input buses

和前面的Input Ports setup/hold类似,Setup/hold for Input buses的本质区别是输入端口为总线型。输入总线会自动被推断得到,并显示其最差情况下的建立时间和保持时间要求。整个总线的最差情况数据窗口是最大建立时间和保持时间值的总和。如果输入端口被约束了,则将同时报告slack值。

3.7 Max/Min Delays for Output Buses

与Output Ports Clock-to-out类似,Max/Min Delays for Output Buses也是输出端口与时钟的时序关系,只是输出端口为总线型。输出总线会自动推断得到,并显示其最差情况下的最大和最小延迟。总线偏差也将一并报告。针对计算总线偏斜,将 1 个bit视为参考位,其它每个bit的偏移都基于此参考bit来计算。

最下面fast corner/slow corner的Bus skew就是对应corner下最大延时减去最小延时,以slow corner为例,Vslow=1.547-1.528=0.019ns

四、分析路径查看

在第三章中,对datasheet报告的各部分进行了介绍,但报告只有不同corner下的值,如何查看具体的路径?这就需要借助Schematic,以打开implement阶段的schematic图为例,在Input ports setup/hold中选择“-0.578”,在schematic中会蓝色高亮显示对应路径。其他值的查看操作类似。

下图是对一条组合路径延时combinational delays的查看

五、示例代码

module all_timing(CLKIN1,CLKIN2,CLKINSEL,CLKFBIN,CLKFBOUT,clk1,clk2,rst,d1,d2,S,I0,I1,I2,i_bus,o_bus,bus_clk2,out_syn,out_asyn,and_out,o_case,out_sense,sel,O,in,choose,out);

input CLKIN1,CLKIN2,CLKINSEL,CLKFBIN,clk1,clk2,rst,d1,d2,S,I0,I1,I2;

input [4:0] i_bus;

output reg [4:0] o_bus,bus_clk2;

output out_syn,out_asyn,and_out,CLKFBOUT;

output out_sense;

input [1:0] sel;

reg ff1,ff2,ff_asyn,ff_syn,ff_and;

reg ff_case;

output reg o_case;

output O;

reg [4:0] bus;

wire sum12,and_c,CLKOUT0,CLKOUT1;

wire [4:0] bus_c;

wire o_bufgmux,ffcase_n;reg mux,ff_sense,ff2_sense;

wire mux_n;input [255:0] in;

input [7:0] choose;

output out;

assign out=in[choose];(*DONT_TOUCH="YES"*) LUT3 #(.INIT(8'h00) // Logic function)LUT3_inst (.O(O), // 1-bit output: LUT.I0(I0), // 1-bit input: LUT.I1(I1), // 1-bit input: LUT.I2(I2) // 1-bit input: LUT);PLLE2_ADV #(.BANDWIDTH("OPTIMIZED"), // OPTIMIZED, HIGH, LOW.CLKFBOUT_MULT(8), // Multiply value for all CLKOUT, (2-64).CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB, (-360.000-360.000).// CLKIN_PERIOD: Input clock period in nS to ps resolution (i.e. 33.333 is 30 MHz)..CLKIN1_PERIOD(0.0),.CLKIN2_PERIOD(0.0),// CLKOUT0_DIVIDE - CLKOUT5_DIVIDE: Divide amount for CLKOUT (1-128).CLKOUT0_DIVIDE(1),.CLKOUT1_DIVIDE(2),.CLKOUT2_DIVIDE(4),.CLKOUT3_DIVIDE(5),.CLKOUT4_DIVIDE(1),.CLKOUT5_DIVIDE(1),// CLKOUT0_DUTY_CYCLE - CLKOUT5_DUTY_CYCLE: Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT0_DUTY_CYCLE(0.4),.CLKOUT1_DUTY_CYCLE(0.5),.CLKOUT2_DUTY_CYCLE(0.5),.CLKOUT3_DUTY_CYCLE(0.5),.CLKOUT4_DUTY_CYCLE(0.5),.CLKOUT5_DUTY_CYCLE(0.5),// CLKOUT0_PHASE - CLKOUT5_PHASE: Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT0_PHASE(0.0),.CLKOUT1_PHASE(0.0),.CLKOUT2_PHASE(0.0),.CLKOUT3_PHASE(0.0),.CLKOUT4_PHASE(0.0),.CLKOUT5_PHASE(0.0),.COMPENSATION("INTERNAL"), // ZHOLD, BUF_IN, EXTERNAL, INTERNAL.DIVCLK_DIVIDE(1), // Master division value (1-56)// REF_JITTER: Reference input jitter in UI (0.000-0.999)..REF_JITTER1(0.0),.REF_JITTER2(0.0),.STARTUP_WAIT("FALSE") // Delay DONE until PLL Locks, ("TRUE"/"FALSE"))PLLE2_ADV_inst (// Clock Outputs: 1-bit (each) output: User configurable clock outputs.CLKOUT0(CLKOUT0), // 1-bit output: CLKOUT0.CLKOUT1(CLKOUT1), // 1-bit output: CLKOUT1.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2// Feedback Clocks: 1-bit (each) output: Clock feedback ports.CLKFBOUT(CLKFBOUT), // 1-bit output: Feedback clock// Clock Inputs: 1-bit (each) input: Clock inputs.CLKIN1(CLKIN1), // 1-bit input: Primary clock.CLKIN2(CLKIN2), // 1-bit input: Secondary clock// Control Ports: 1-bit (each) input: PLL control ports.CLKINSEL(CLKINSEL), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2.RST(rst), // 1-bit input: Reset// Feedback Clocks: 1-bit (each) input: Clock feedback ports.CLKFBIN(CLKFBIN) // 1-bit input: Feedback clock);// End of PLLE2_ADV_inst instantiation

always@(posedge CLKOUT0,negedge rst)if(!rst)beginff1<=1'b0;ff2<=1'b0;endelse beginff1<=d1;ff2<=d2;endassign sum12=ff1+ff2;

always@(posedge CLKOUT1,negedge rst)if(!rst)ff_syn<=1'b0;else beginff_syn<=sum12;end

assign out_syn=ff_syn;always@(posedge clk1,negedge rst)if(!rst)ff_asyn<=1'b0;else beginff_asyn<=sum12;end

assign out_asyn=ff_asyn;

assign and_c=ff_asyn&d1;always@(posedge clk1,negedge rst)if(!rst)ff_and<=1'b0;else beginff_and<=and_c;end

assign and_out=ff_and;always@(posedge clk1,negedge rst)if(!rst)bus<=5'b0;else beginbus<=i_bus+1'b1;end

assign bus_c=bus+d2;

always@(*)begino_bus=bus;end

always@(posedge clk2,negedge rst)if(!rst)bus_clk2<=5'b0;else beginbus_clk2<=bus_c+d1;end

//set_case_analysisBUFGMUX #()BUFGMUX_inst (.O(o_bufgmux), // 1-bit output: Clock output.I0(CLKIN1), // 1-bit input: Clock input (S=0).I1(CLKIN2), // 1-bit input: Clock input (S=1).S(S) // 1-bit input: Clock select);always@(posedge o_bufgmux,negedge rst)if(!rst)ff_case<=1'b0;else beginff_case<=d1;end

assign ffcase_n=!ff_case;always@(posedge o_bufgmux,negedge rst)if(!rst)o_case<=1'b0;else begino_case<=ffcase_n;end

//set_clock_sense

always@(sel)

begincase(sel)2'b00:mux<=clk1;2'b01:mux<=clk2;2'b10:mux<=CLKIN1;2'b11:mux<=CLKIN2;endcase

end

assign mux_n=mux;

always@(posedge mux_n)

begin

if(!rst)ff_sense<=1'b0;

elseff_sense<=d1;

end

always@(posedge mux_n)

begin

if(!rst)ff2_sense<=1'b0;

elseff2_sense<=ff_sense;

end

assign out_sense=ff2_sense;

endmodule约束文件

//创建主时钟和生成时钟

create_clock -period 10.000 -name clkin1 -waveform {0.000 5.000} -add [get_ports CLKIN1]

create_clock -period 5.000 -name clkin2 -waveform {0.000 2.500} -add [get_nets CLKIN2]

create_clock -period 4.000 -name clk2 -waveform {0.000 2.000} -add [get_ports clk2]

create_clock -period 4.000 -name clk1 -waveform {0.000 2.000} -add [get_ports clk1]

create_generated_clock -name gen_clk -source [get_pins PLLE2_ADV_inst/CLKOUT1] -multiply_by 2 -add -master_clock clkin2 [get_pins PLLE2_ADV_inst/CLKOUT0]

set_input_jitter [get_clocks clk2] 0.500

set_clock_latency -clock [get_clocks clk2] 0.333 [get_pins {bus_reg[1]/D}]

set_system_jitter 0.009

set_clock_uncertainty 0.500 [get_clocks clk1]//设置时钟组和总线偏斜

set_clock_groups -name clkin1_group -asynchronous -group [get_clocks clkin1]

set_bus_skew -from [get_cells {{bus_reg[0]} {bus_reg[1]} {bus_reg[2]} {bus_reg[3]} {bus_reg[4]}}] -to [get_cells {{bus_clk2_reg[0]} {bus_clk2_reg[1]} {bus_clk2_reg[2]} {bus_clk2_reg[3]} {bus_clk2_reg[4]}}] 0.550

set_input_delay -clock [get_clocks clk1] 1.111 [get_ports {d1 d2 {i_bus[0]} {i_bus[1]} {i_bus[2]} {i_bus[3]} {i_bus[4]} rst}]

set_output_delay -clock [get_clocks clk2] 0.222 [get_ports {and_out {o_bus[0]} {o_bus[1]} {o_bus[2]} {o_bus[3]} {o_bus[4]} out_asyn out_syn}]//设置时序例外分析

set_false_path -setup -from [get_pins {bus_reg[2]/C}] -to [get_pins {bus_clk2_reg[4]/D}]

set_max_delay -from [get_pins {bus_reg[1]/C}] 2.000

set_min_delay -from [get_pins {bus_reg[0]/C}] 0.500

set_multicycle_path -from [get_pins {bus_reg[0]/C}] -to [get_pins {bus_clk2_reg[2]/D}] 2

set_disable_timing [get_cells {bus_reg[3]}]//设置时序断言

set_case_analysis 1 [get_ports S]

set_data_check -from [get_pins {bus_reg[2]/C}] -to [get_pins {bus_reg[2]/Q}] 0.333 -clock [get_clocks clk2]

set_clock_sense -positive -clocks [get_clocks clk1] [get_pins ff_asyn_reg/C]

group_path -name {group_path} -weight 1.000 -from [get_ports {d1 d2}]六、参考文件

《ug906-vivado-design-analysis-en-us.pdf》