异构集成封装类型:2D、2.1D、2.3D、2.5D和3D封装详解

简介随着摩尔定律的放缓,半导体行业越来越多地采用芯片设计和异构集成封装来继续推动性能的提高。这种方法是将大型硅芯片分割成多个较小的芯片,分别进行设计、制造和优化,然后再集成到单个封装中。

本文将介绍芯片设计的基本原理、异构集成封装、优势和挑战,以及在大批量制造 (HVM) 中使用这些方法的产品示例。

片上系统(SoC)传统的片上系统 (SoC) 将 CPU、GPU、内存和其他专用处理器等组件集成到一个单片芯片中,如图 1 所示,苹果公司 A 系列应用处理器 (AP) 的晶体管数量不断增加。然而,单片 SoC 的扩展成本越来越高,效率也越来越低,令人望而却步。  图 1 苹果的 AP:晶体管与 A10-A17 处理技术和年份的对比Chiplet设计Chiplet设计不是单片 SoC,而是将各种计算芯片(如 CPU、GPU、AI 加速器)和内存分解到独立的硅芯片上。这些芯片可以利用优化的制造工艺,并采用先进的封装技术组装成单一封装。主要优势包括:

图 1 苹果的 AP:晶体管与 A10-A17 处理技术和年份的对比Chiplet设计Chiplet设计不是单片 SoC,而是将各种计算芯片(如 CPU、GPU、AI 加速器)和内存分解到独立的硅芯片上。这些芯片可以利用优化的制造工艺,并采用先进的封装技术组装成单一封装。主要优势包括:

- 通过隔离故障提高制造良率

- 能够混合不同的半导体工艺节点

- 扩展现有工艺节点的价值

- 独立扩展计算和内存

- 改进上市时间和产品生命周期管理

不过,Chiplet设计也面临着一些挑战,如芯片间通信开销、组装复杂性和潜在的热机械问题。

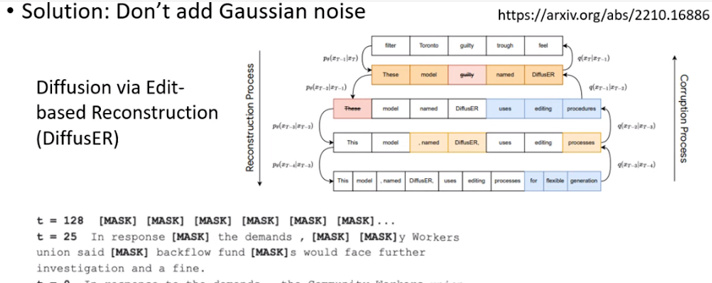

异构集成封装为了将独立的芯片组装成一个内聚封装,采用了异构集成封装技术,如 2D、2.1D、2.3D、2.5D 和 3D 集成,这些技术是根据其互连密度能力分类的(图 2)。我们将举例说明:  图 2 根据密度和性能划分的先进封装等级二维集成如图 3 和 4 所示,在二维集成中,芯片通过倒装芯片、线键或扇出式封装并排组装在同一封装基板上。这种方法广泛用于智能手机等消费类产品。

图 2 根据密度和性能划分的先进封装等级二维集成如图 3 和 4 所示,在二维集成中,芯片通过倒装芯片、线键或扇出式封装并排组装在同一封装基板上。这种方法广泛用于智能手机等消费类产品。  图 3 二维集成电路集成实例 a 一个封装基板上有两个倒装芯片。b 封装基板上的一个倒装芯片和一个带有线键的 MEMS

图 3 二维集成电路集成实例 a 一个封装基板上有两个倒装芯片。b 封装基板上的一个倒装芯片和一个带有线键的 MEMS 图 4 扇出 RDL 基底面上四个芯片的异构集成2.1D 集成2.1D 集成可直接在封装基板上制造细间距金属互连层,从而实现比 2D 更高的互连密度。图 5 显示了 Shinko 的集成薄膜高密度有机封装 (i-THOP),其线路/空间互连层为 2μm。JCET 的 uFOS(图 6)以及日立、日月光和 SPIL 的方法也采用了 2.1D 集成。

图 4 扇出 RDL 基底面上四个芯片的异构集成2.1D 集成2.1D 集成可直接在封装基板上制造细间距金属互连层,从而实现比 2D 更高的互连密度。图 5 显示了 Shinko 的集成薄膜高密度有机封装 (i-THOP),其线路/空间互连层为 2μm。JCET 的 uFOS(图 6)以及日立、日月光和 SPIL 的方法也采用了 2.1D 集成。

图5展示Shinko的2.1D集成电路:采用革新性的i-THOP技术,实现薄膜高密度有机封装,提升集成效率。

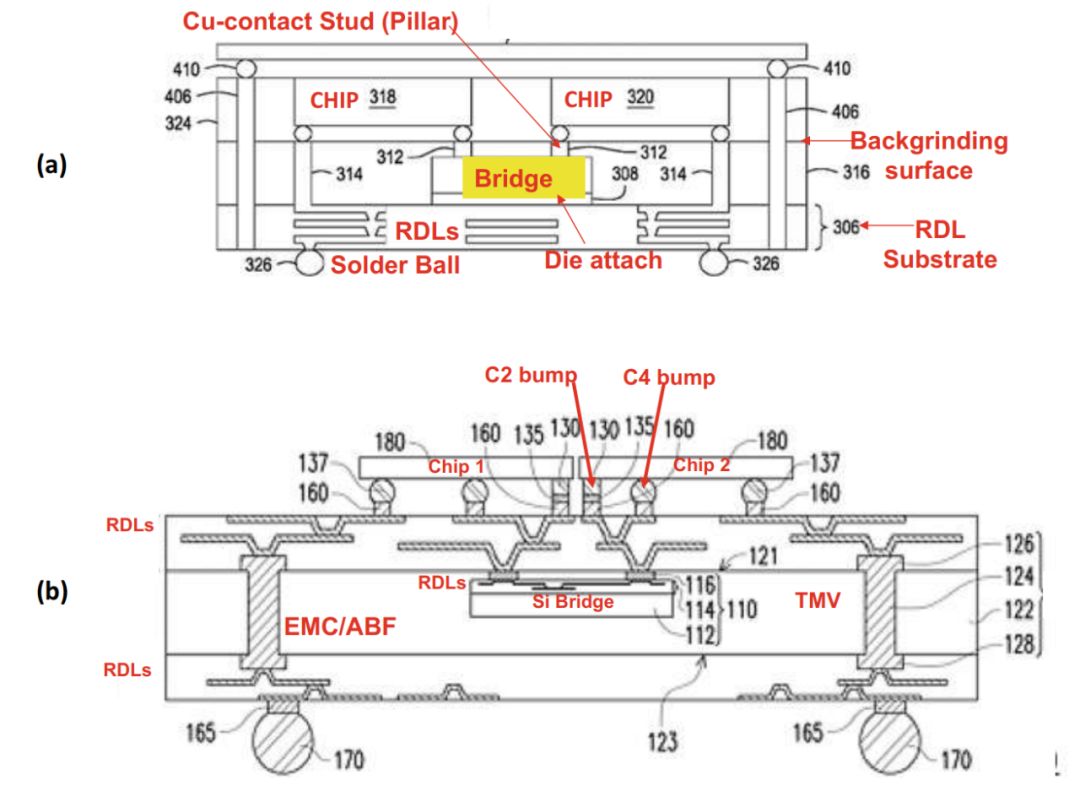

图 6 JCET 的 2.1.D 集成电路集成:uFOS(超格式有机基板)另一种 2.1D 方法是在封装中嵌入具有细间距 RDL 的硅桥,以实现芯片到芯片的通信,如英特尔的 EMIB(图 7)、IBM 的 DBHi(图 8),以及应用材料公司、台积电、硅品、Amkor、日月光和其他公司的嵌入式桥变体(图 9 和 10)。

图 6 JCET 的 2.1.D 集成电路集成:uFOS(超格式有机基板)另一种 2.1D 方法是在封装中嵌入具有细间距 RDL 的硅桥,以实现芯片到芯片的通信,如英特尔的 EMIB(图 7)、IBM 的 DBHi(图 8),以及应用材料公司、台积电、硅品、Amkor、日月光和其他公司的嵌入式桥变体(图 9 和 10)。  图 7 a 英特尔嵌入在有机封装基板和 Agilex FPGA 模块中的 EMIB(嵌入式多层互连桥接器)

图 7 a 英特尔嵌入在有机封装基板和 Agilex FPGA 模块中的 EMIB(嵌入式多层互连桥接器) 图 8 IBM 的 DBHi(直接粘合异质集成)

图 8 IBM 的 DBHi(直接粘合异质集成) 图 9 a Applied Materials 通过扇出芯片(桥接器)首模朝上工艺嵌入 EMC 的桥接器。b 欣兴电子公司通过扇出芯片(桥接器)首模朝下工艺在 EMC 中嵌入桥接器。2022 年,美国专利号:11,410,933。

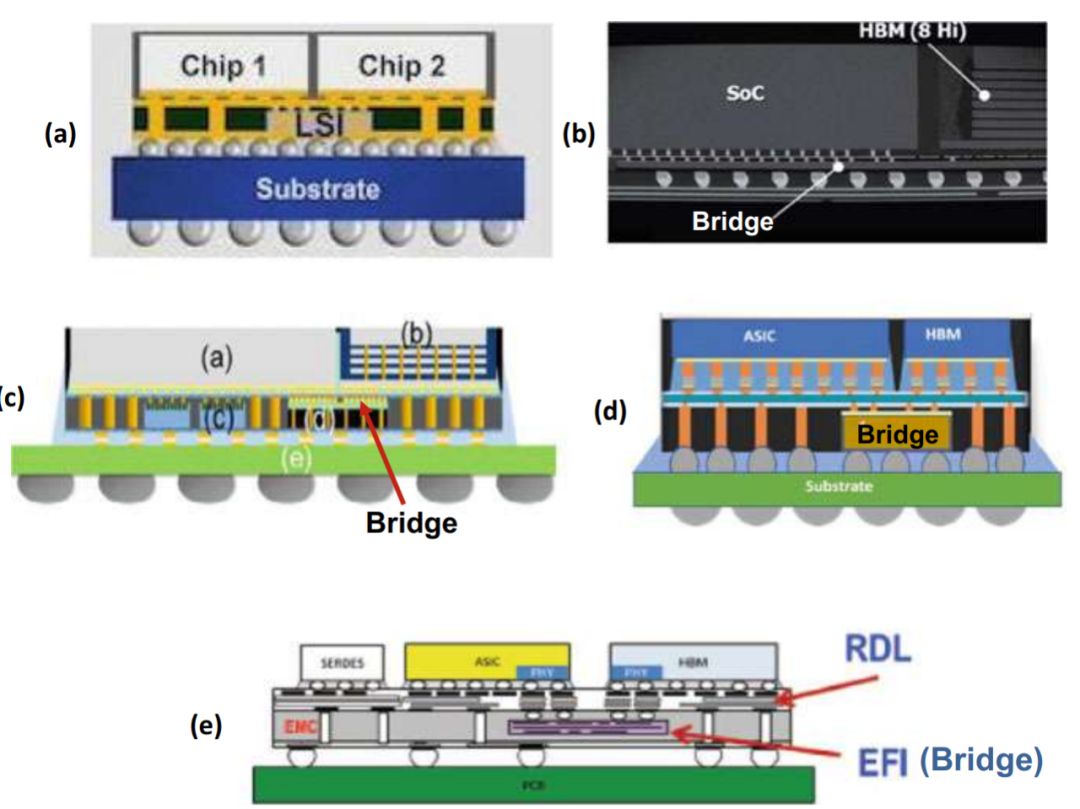

图 9 a Applied Materials 通过扇出芯片(桥接器)首模朝上工艺嵌入 EMC 的桥接器。b 欣兴电子公司通过扇出芯片(桥接器)首模朝下工艺在 EMC 中嵌入桥接器。2022 年,美国专利号:11,410,933。 图 10 a 嵌入 EMC 的电桥示例:台积电的 LSI(本地硅互连)。b SPIL 的 FO-EB(扇出嵌入式电桥)。c Amkor 的 S-Connect。d ASE 的 sFOCoS(堆叠硅桥扇出基底芯片)。

图 10 a 嵌入 EMC 的电桥示例:台积电的 LSI(本地硅互连)。b SPIL 的 FO-EB(扇出嵌入式电桥)。c Amkor 的 S-Connect。d ASE 的 sFOCoS(堆叠硅桥扇出基底芯片)。

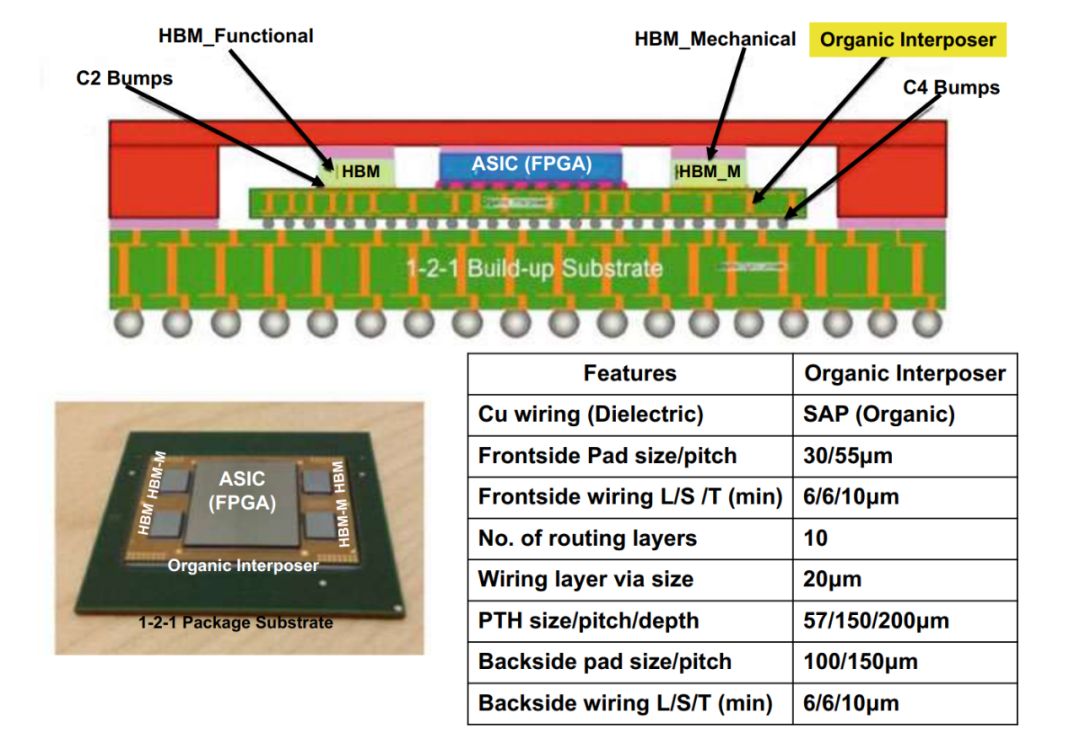

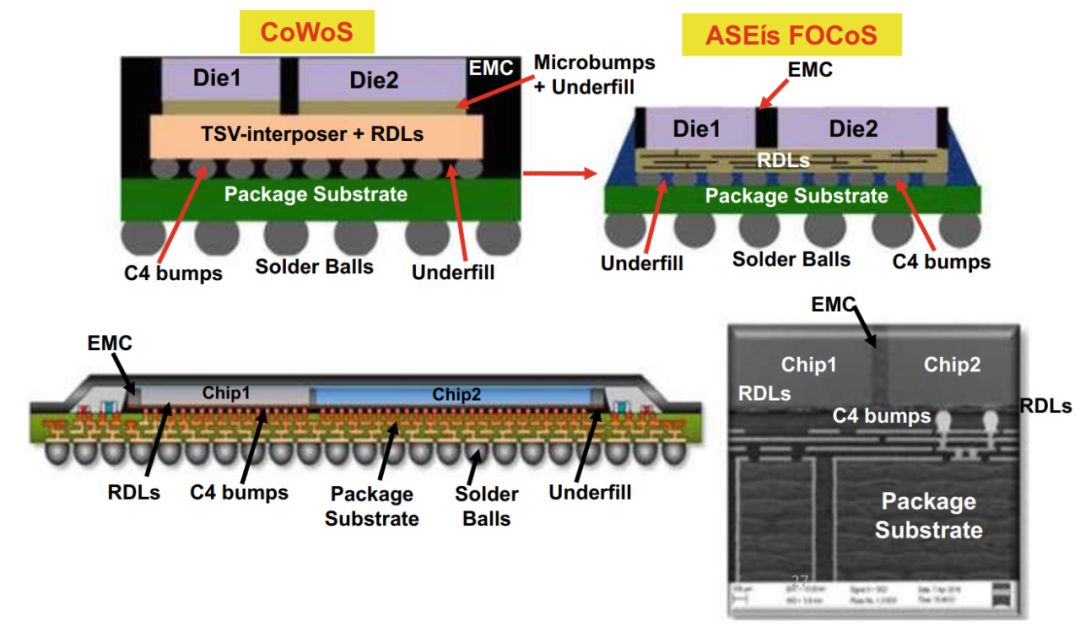

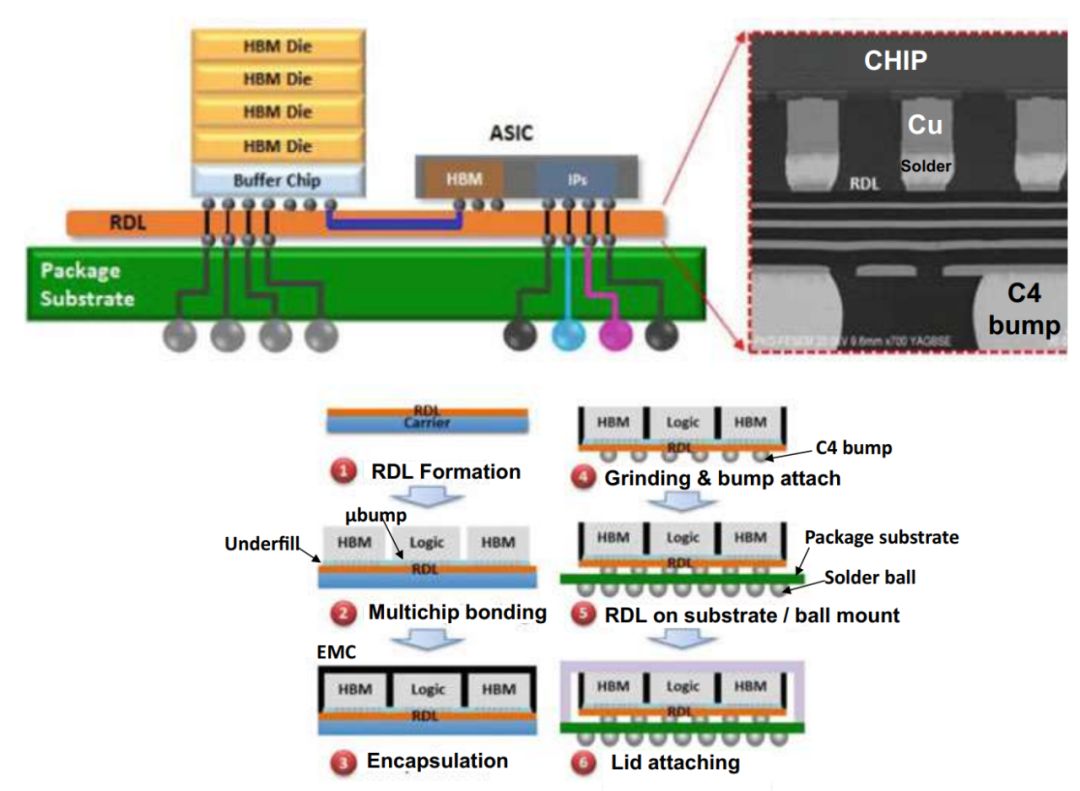

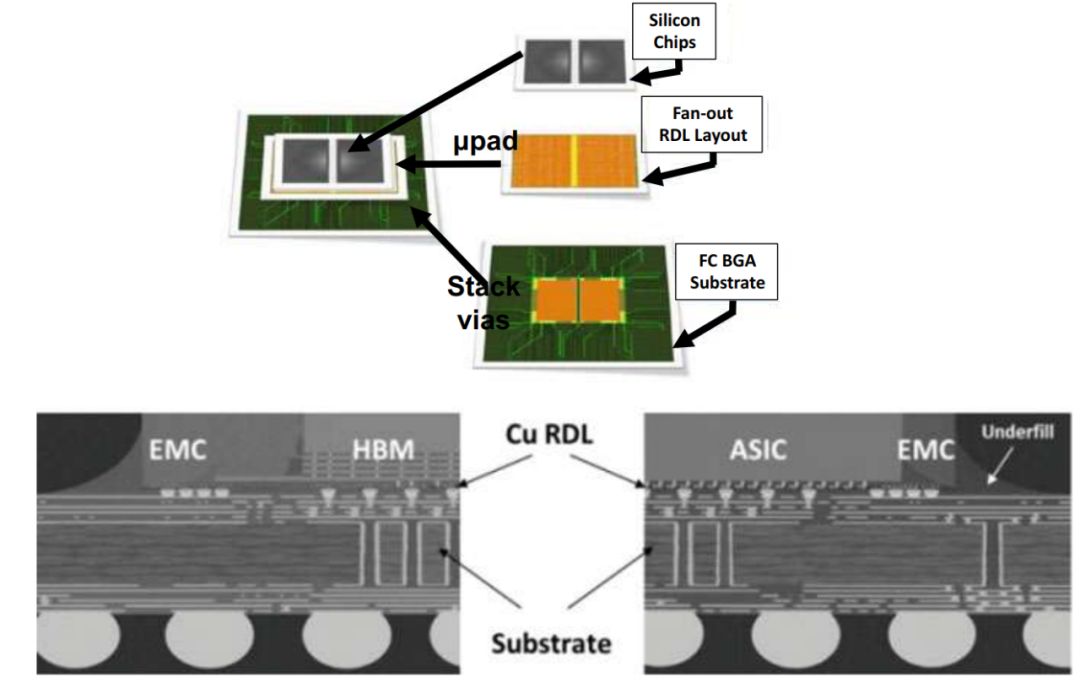

2.3D 集成2.3D 集成制造了一个与封装基板集成的独立细间距 RDL 基板(或有机interposer),实现了比 2.1D 更高的互连密度,思科的大型 12 层有机interposer就是一例(图 11)。  图 11 思科公司采用 SAP/PCB 方法将 2.3D 集成电路与积层有机interposer集成在一起制造 RDL 基底面的方法包括半加成 PCB 工艺、扇出芯片先导法(如图 12 中的日月光 FOCoS)和扇出芯片后/RDL 先导法(如图 13 中的三星、图 14 中的日月光、图 15-17 中的欣兴)。

图 11 思科公司采用 SAP/PCB 方法将 2.3D 集成电路与积层有机interposer集成在一起制造 RDL 基底面的方法包括半加成 PCB 工艺、扇出芯片先导法(如图 12 中的日月光 FOCoS)和扇出芯片后/RDL 先导法(如图 13 中的三星、图 14 中的日月光、图 15-17 中的欣兴)。  图 12 日月光采用扇出(芯片先导)RDL 基底面(中间膜)的 2.3D 集成电路集成电路

图 12 日月光采用扇出(芯片先导)RDL 基底面(中间膜)的 2.3D 集成电路集成电路 图 13 三星的 2.3D 集成电路与扇出式(芯片后置)RDL interposer的集成

图 13 三星的 2.3D 集成电路与扇出式(芯片后置)RDL interposer的集成 图 14 日月光的 2.3D 集成电路与在临时晶圆上制造的扇出型(芯片后置)RDL interposer的集成

图 14 日月光的 2.3D 集成电路与在临时晶圆上制造的扇出型(芯片后置)RDL interposer的集成 图 15 利用 PID(光成像电介质)制造的带有扇出(芯片末端)RDL interposer的欣兴电子 2.3D 集成电路集成电路

图 15 利用 PID(光成像电介质)制造的带有扇出(芯片末端)RDL interposer的欣兴电子 2.3D 集成电路集成电路 图 16 使用 ABF制造的 2.3D 集成电路扇出(芯片末端)RDL interposer

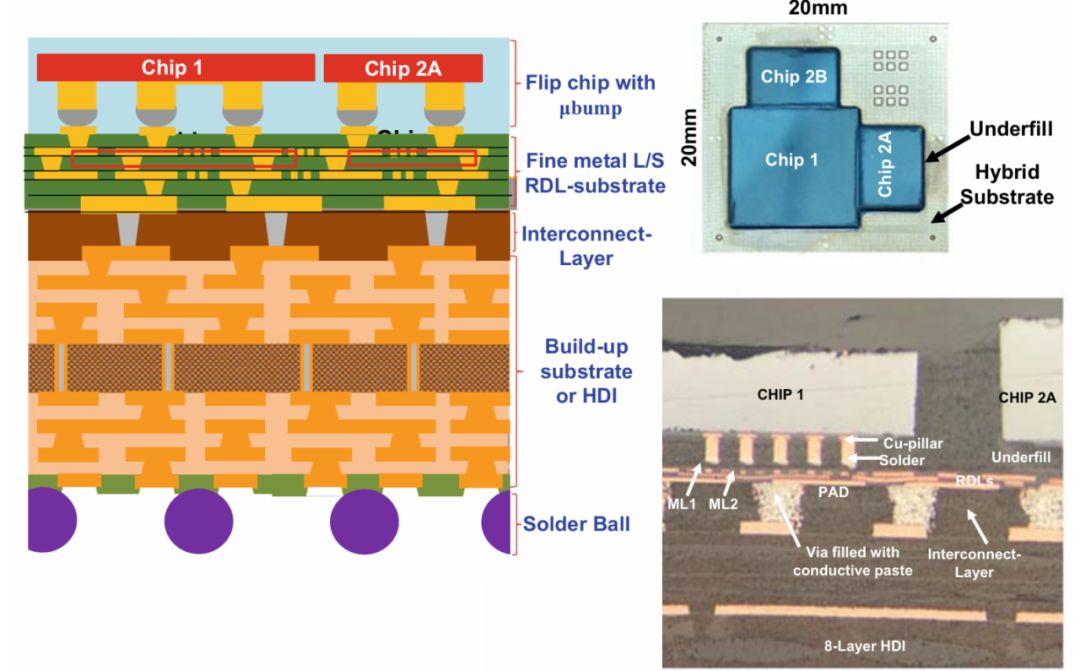

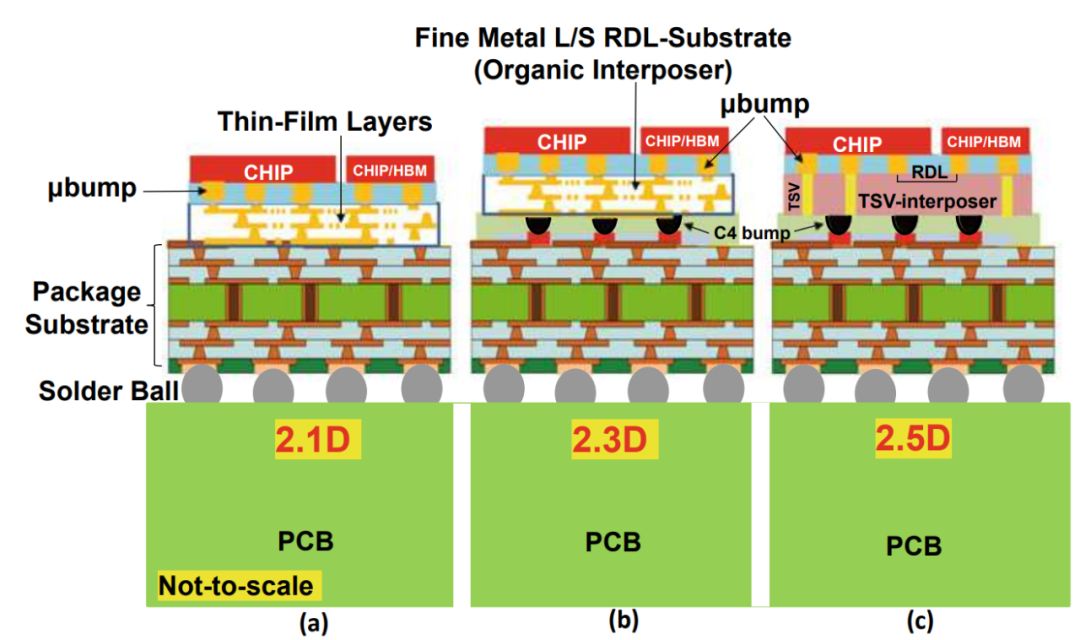

图 16 使用 ABF制造的 2.3D 集成电路扇出(芯片末端)RDL interposer 图 17 欣兴电子公司带有互连层的 2.3D 集成电路集成电路2.5D 集成在 2.5D 集成中,芯片组装在带有硅通孔(TSV)的硅中间膜上,然后安装在封装基板上,从而实现极高的互连密度(图 18)。这方面的例子包括 AMD/UMC 在 2.5D 夹层上采用 HBM 内存立方体的 GPU(图 19),以及 Nvidia 在台积电 CoWoS-2 夹层上采用 HBM2 的 GPU(图 20)。

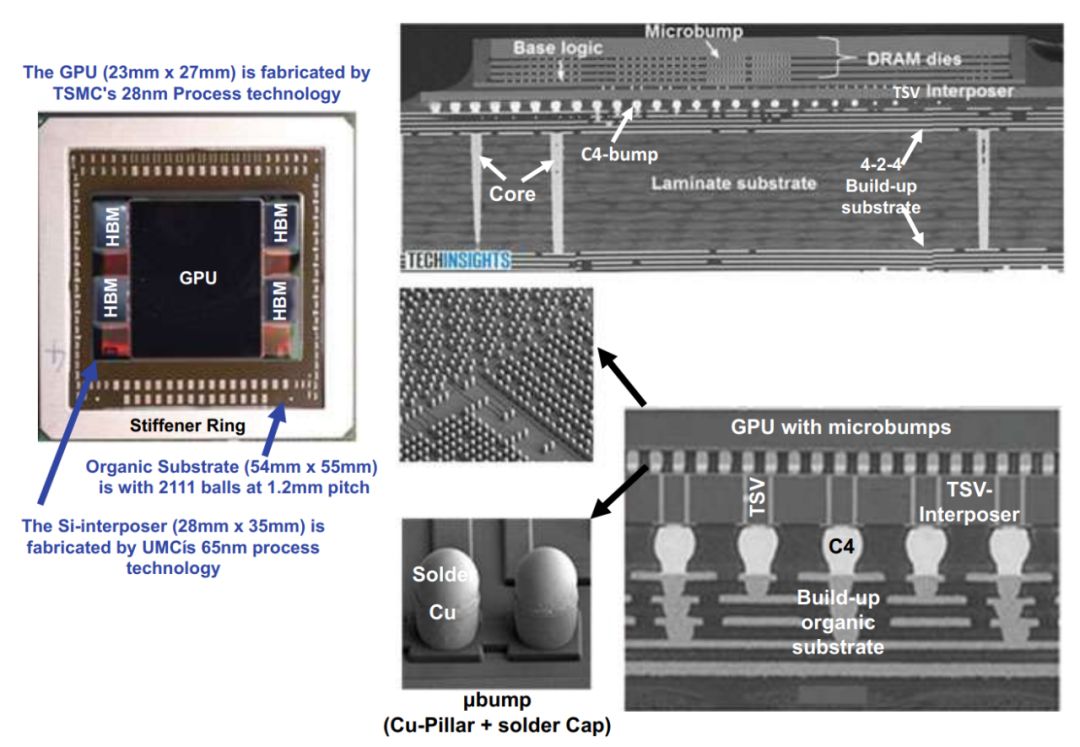

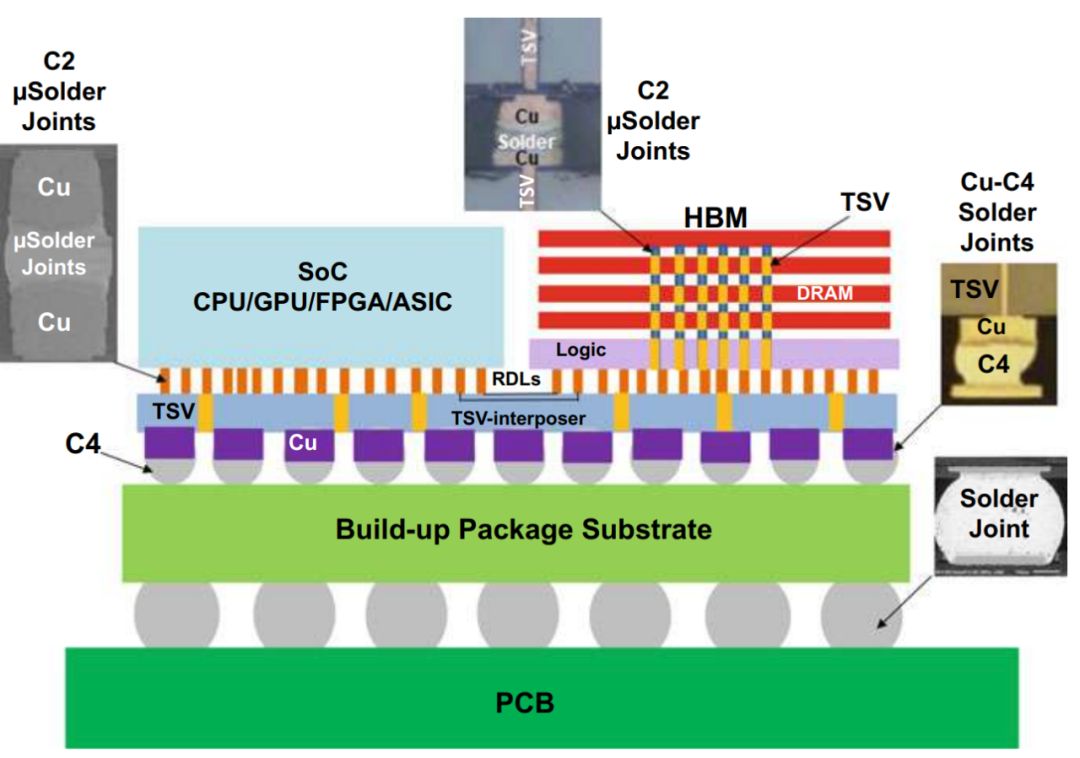

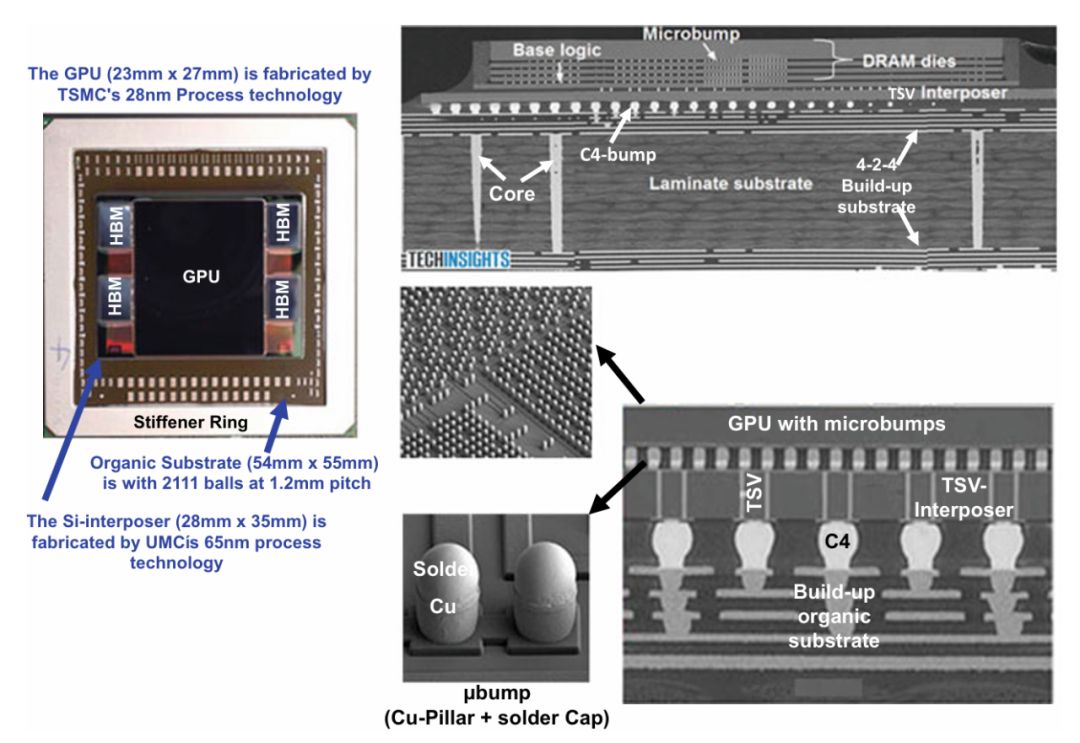

图 17 欣兴电子公司带有互连层的 2.3D 集成电路集成电路2.5D 集成在 2.5D 集成中,芯片组装在带有硅通孔(TSV)的硅中间膜上,然后安装在封装基板上,从而实现极高的互连密度(图 18)。这方面的例子包括 AMD/UMC 在 2.5D 夹层上采用 HBM 内存立方体的 GPU(图 19),以及 Nvidia 在台积电 CoWoS-2 夹层上采用 HBM2 的 GPU(图 20)。  图 18 a 2.1D、b 2.3D 和 c 2.5D/3D 集成电路集成示意图

图 18 a 2.1D、b 2.3D 和 c 2.5D/3D 集成电路集成示意图 图 19 AMD/UMC 的 2.5D 集成电路集成图

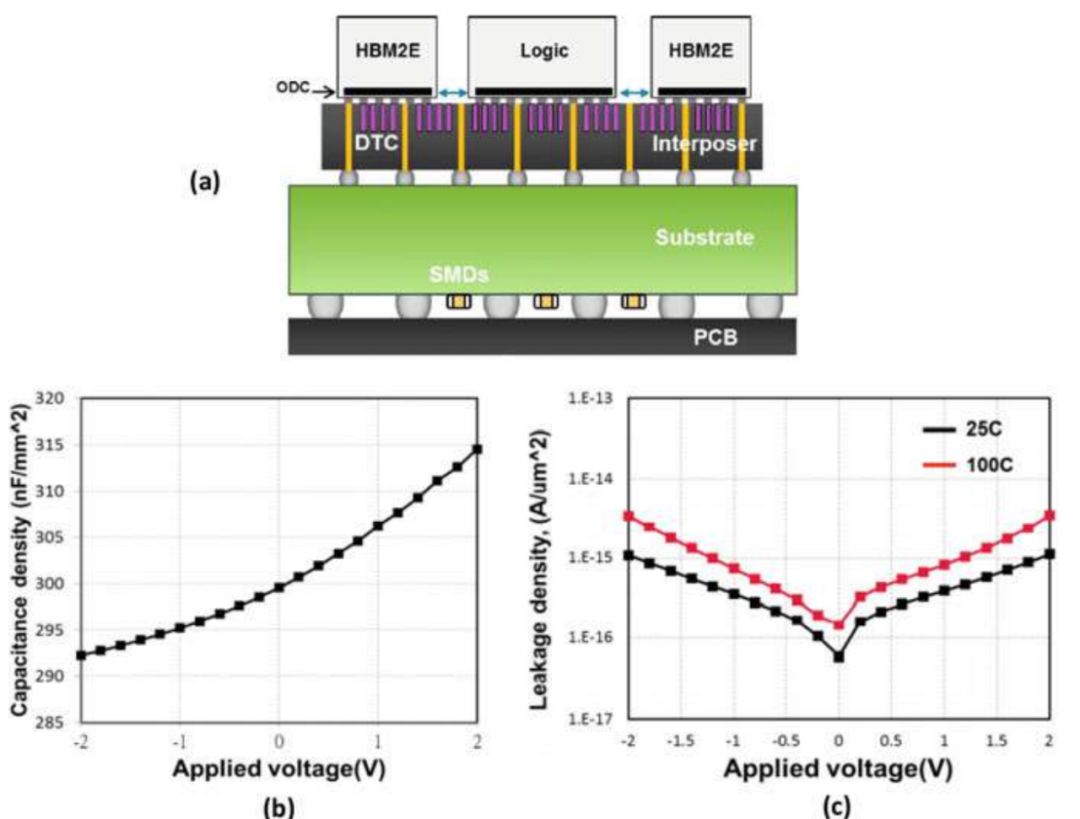

图 19 AMD/UMC 的 2.5D 集成电路集成图 图 20 NVidia/TSMC 的 2.5D 集成电路集成图台积电已在集成电路中开发出深沟槽电容器(图 21),而弗劳恩霍夫则展示了集成光学和电子器件的三维光子集成电路(图 22)。图 23 和图 24 展示了使用 2.5D interposer的光电共封装器件。

图 20 NVidia/TSMC 的 2.5D 集成电路集成图台积电已在集成电路中开发出深沟槽电容器(图 21),而弗劳恩霍夫则展示了集成光学和电子器件的三维光子集成电路(图 22)。图 23 和图 24 展示了使用 2.5D interposer的光电共封装器件。  图 21 台积电的 2.5D 集成电路与 ODC(片上电容)和 DTC(深沟电容)的集成。b 电容密度。

图 21 台积电的 2.5D 集成电路与 ODC(片上电容)和 DTC(深沟电容)的集成。b 电容密度。 图 22 用于 Tb/s 光互连的 Fraunhofer 3D 硅基光电子集成电路

图 22 用于 Tb/s 光互连的 Fraunhofer 3D 硅基光电子集成电路 图 23 高速 PIC(光子集成电路)和 EIC(电子集成电路)器件的封装

图 23 高速 PIC(光子集成电路)和 EIC(电子集成电路)器件的封装 图 24 用于 HPC 的 2.5D 集成电路集成。无源 TSV 夹层支持 SoC 和 HBM三维集成 三维集成利用硅通孔(TSV)垂直堆叠芯片,无硅通孔(三维封装,图 25)或有硅通孔(三维集成,图 26)。高带宽内存(HBM)是高性能计算的关键三维集成内存技术,可垂直堆叠多个 DRAM 芯片(图 27)。

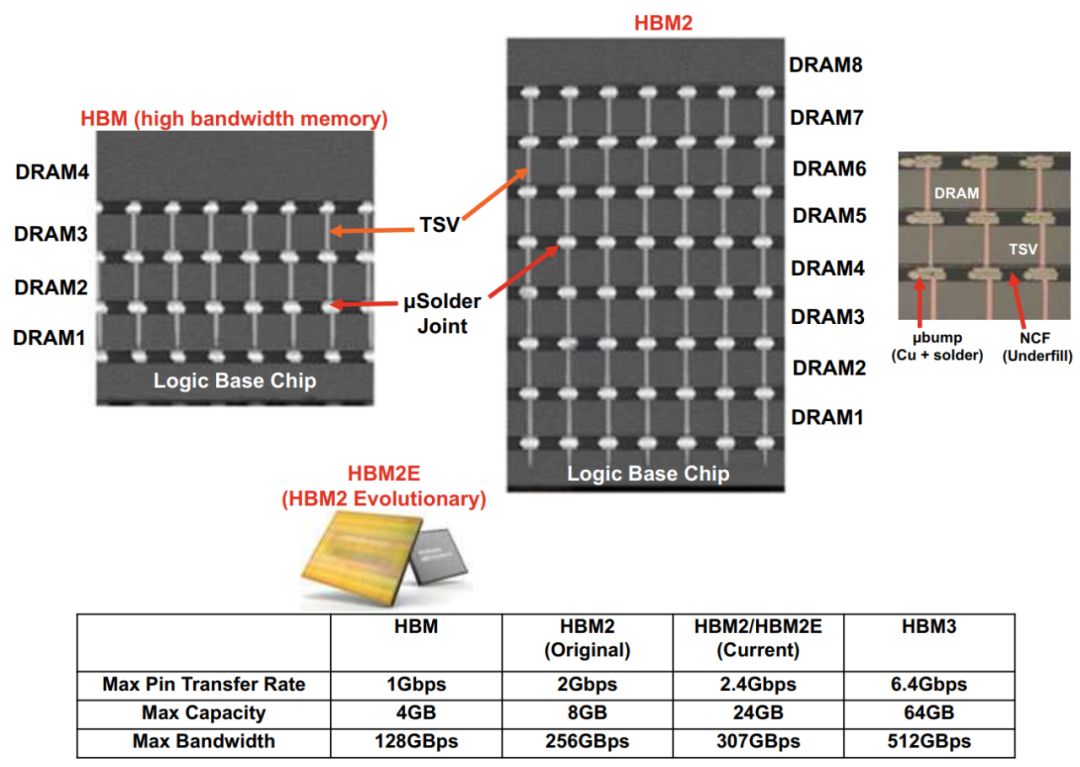

图 24 用于 HPC 的 2.5D 集成电路集成。无源 TSV 夹层支持 SoC 和 HBM三维集成 三维集成利用硅通孔(TSV)垂直堆叠芯片,无硅通孔(三维封装,图 25)或有硅通孔(三维集成,图 26)。高带宽内存(HBM)是高性能计算的关键三维集成内存技术,可垂直堆叠多个 DRAM 芯片(图 27)。  图 25 3D 集成电路封装(无 TSV)的几个示例。a 用接线键合堆叠的存储芯片。b 两个芯片面对面焊接凸点倒装芯片,然后用焊线键合到下一级互连。c 两个芯片背靠背粘接;底部芯片通过焊接凸块倒装芯片粘接到基板,顶部芯片通过焊线粘接到基板。d 两个芯片面对面焊接凸块粘接,顶部芯片通过焊球粘接到基板。e 应用处理器芯片组的倒装芯片 PoP。f 应用处理器芯片组的扇出 PoP。

图 25 3D 集成电路封装(无 TSV)的几个示例。a 用接线键合堆叠的存储芯片。b 两个芯片面对面焊接凸点倒装芯片,然后用焊线键合到下一级互连。c 两个芯片背靠背粘接;底部芯片通过焊接凸块倒装芯片粘接到基板,顶部芯片通过焊线粘接到基板。d 两个芯片面对面焊接凸块粘接,顶部芯片通过焊球粘接到基板。e 应用处理器芯片组的倒装芯片 PoP。f 应用处理器芯片组的扇出 PoP。 图 26 三维集成电路集成实例:a 带有微凸块和 TSV 的 HBM;b 带有 TSV 和微凸块的 CoC;c 带有 TSV 和无凸块的 CoC。

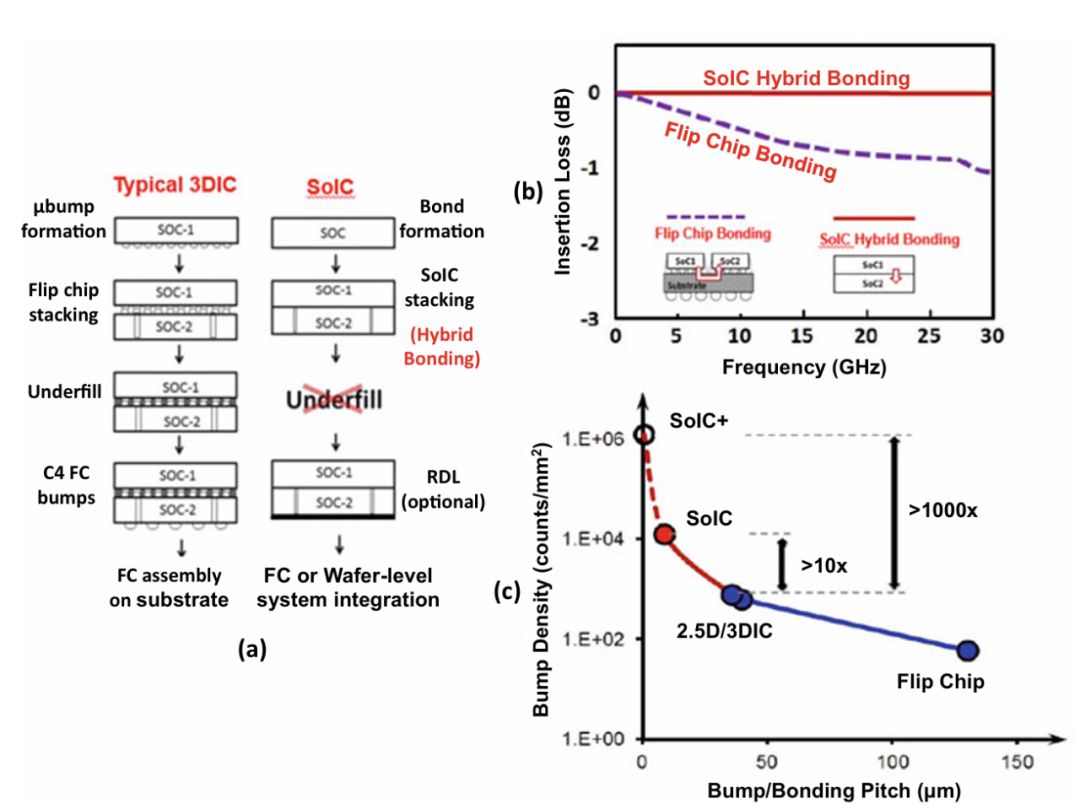

图 26 三维集成电路集成实例:a 带有微凸块和 TSV 的 HBM;b 带有 TSV 和微凸块的 CoC;c 带有 TSV 和无凸块的 CoC。 图 27 HBM、HBM2、HBM2E 和 HBM3例如,IME 使用 TSV 和微凸块的逻辑内存(图 28),以及英特尔使用 FOVEROS 技术和微凸块将计算芯片集成在有源插层上的 Lakefield 处理器(图 29)。台积电也展示了用于三维集成的无凸块混合键合技术(图 30、31)。

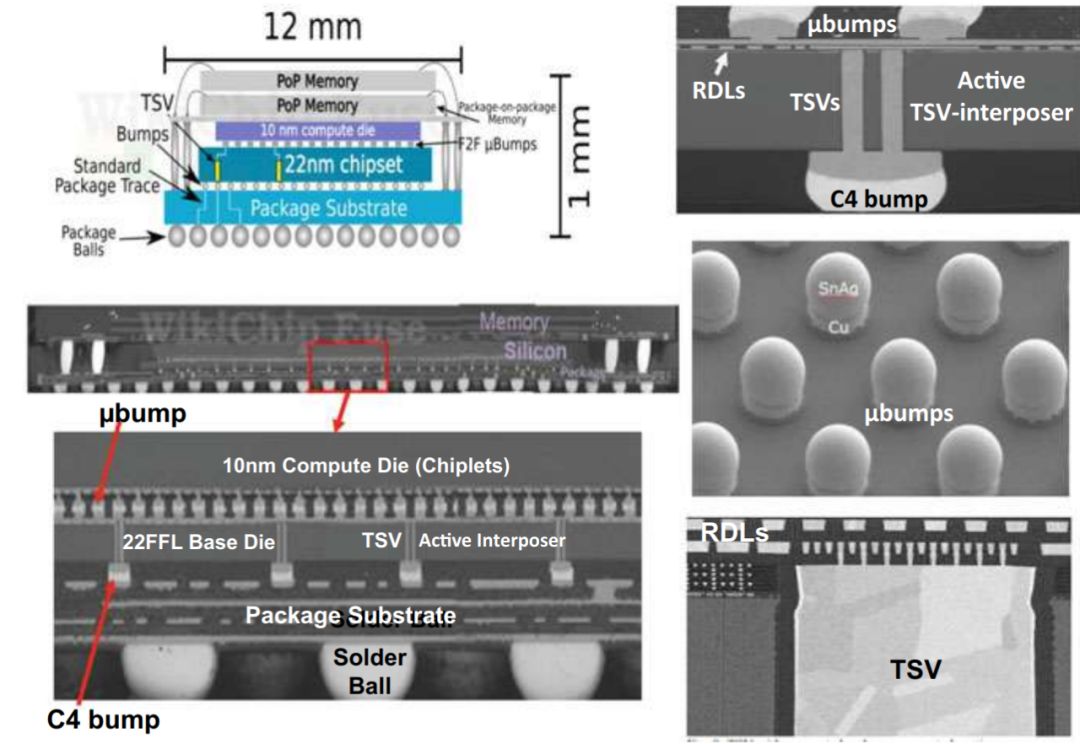

图 27 HBM、HBM2、HBM2E 和 HBM3例如,IME 使用 TSV 和微凸块的逻辑内存(图 28),以及英特尔使用 FOVEROS 技术和微凸块将计算芯片集成在有源插层上的 Lakefield 处理器(图 29)。台积电也展示了用于三维集成的无凸块混合键合技术(图 30、31)。  图 28 3D 集成电路集成:存储器芯片通过 TSV 微凸块集成在 ASIC 芯片上

图 28 3D 集成电路集成:存储器芯片通过 TSV 微凸块集成在 ASIC 芯片上 图 29 3D 集成电路集成: 英特尔芯片面对面微凸块在有源 TSV 互连器上

图 29 3D 集成电路集成: 英特尔芯片面对面微凸块在有源 TSV 互连器上 图 30 a 台积电通过混合接合实现的 SoIC。b 电气性能:SoIC 混合键合与传统倒装芯片键合的比较。c 凸点密度性能:SoIC 混合键合与传统倒装芯片键合

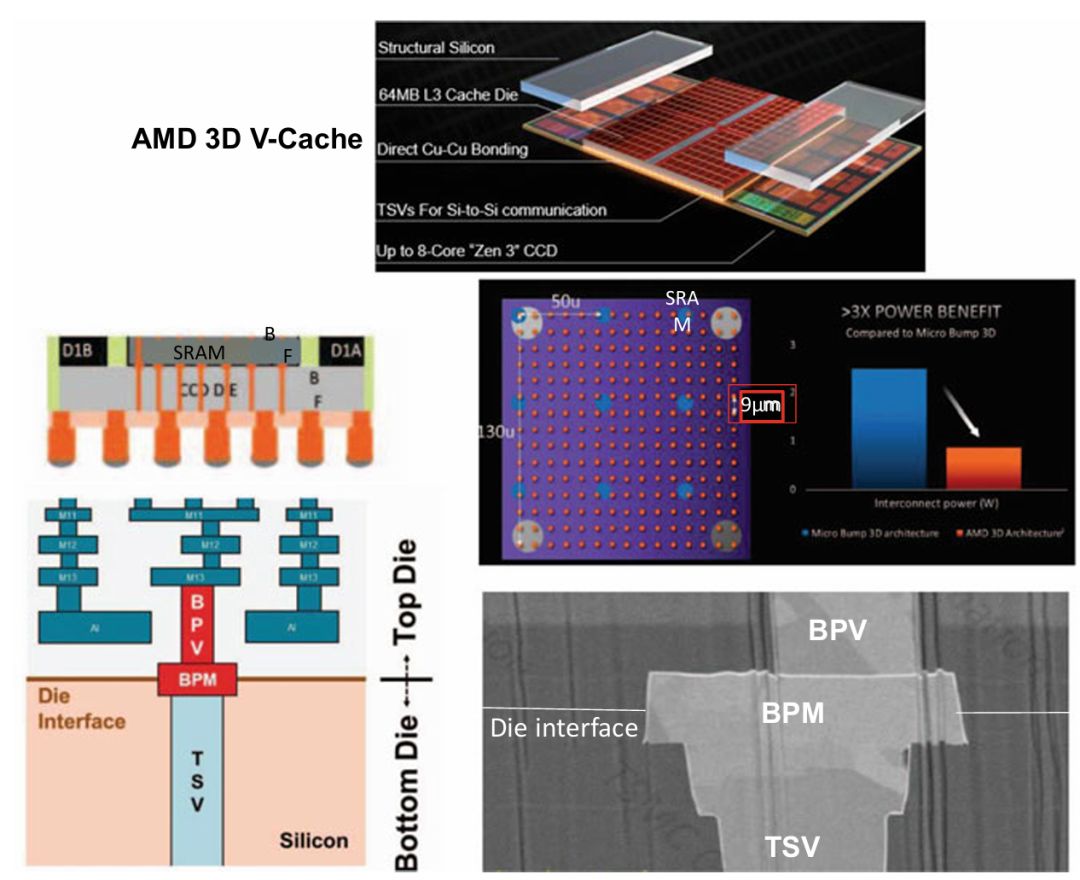

图 30 a 台积电通过混合接合实现的 SoIC。b 电气性能:SoIC 混合键合与传统倒装芯片键合的比较。c 凸点密度性能:SoIC 混合键合与传统倒装芯片键合 图 31 台积电用于 AMD 3D V-cache 的 SoIC 铜-铜混合键合技术HVM 中的芯片产品一些高性能计算产品已经开始采用芯片设计和异构集成封装制造:

图 31 台积电用于 AMD 3D V-cache 的 SoIC 铜-铜混合键合技术HVM 中的芯片产品一些高性能计算产品已经开始采用芯片设计和异构集成封装制造:

- 台积电CoWoS 2.5D封装技术赋能Xilinx/TSMC Virtex FPGA,2013年即实现出货,卓越性能引领行业潮流。

- AMD Radeon GPU搭载创新2.5D interposer技术的HBM,如2015年旗舰R9 Fury X所示,引领图形处理新纪元,强劲性能不容小觑。

- Nvidia Pascal与Volta GPU在2.5D插槽上搭载高效HBM2显存,如2016年推出的Pascal 100,引领行业革新,释放卓越性能。

- AMD EPYC 服务器 CPU,采用大型有机基板上的芯片(2019 年)

- 英特尔Lakefield移动处理器,采用创新的FOVEROS 3D封装技术,高效集成芯片,是2020年科技新品中的佼佼者(见图34)。

- 苹果A12/A16应用处理器,采用台积电InFO扇出封装PoP技术(自2016年起,图35),展现先进封装工艺。

- 使用扇出面板级封装集成的三星智能手表 SoC 和存储器(2018 年,图 36)

图 32 AMD/UMC 的 2.5D 集成电路集成

图 32 AMD/UMC 的 2.5D 集成电路集成 图 33 NVidia/TSMC 的 2.5D 集成电路集成

图 33 NVidia/TSMC 的 2.5D 集成电路集成 图 34 3D集成: 英特尔的芯片在有源 TSV interposer上,面对面的微凸块集成

图 34 3D集成: 英特尔的芯片在有源 TSV interposer上,面对面的微凸块集成 图 35 苹果/台积电为 iPhone 的 AP 芯片组采用 InFO 的 PoP

图 35 苹果/台积电为 iPhone 的 AP 芯片组采用 InFO 的 PoP 图 36 三星为其智能手表采用 FOPLP 的 PoP

图 36 三星为其智能手表采用 FOPLP 的 PoP

结论Chiplet设计和异质集成封装是半导体持续扩大规模和提高性能的关键因素。通过将大型单片 SoC 分解成使用 2D、2.1D、2.3D、2.5D 或 3D 封装技术组装的优化芯片,我们可以缓解制造问题,扩大工艺节点规模,集成异构技术,并推动新的系统架构。在计算、移动、人工智能、网络和其他领域,许多大批量产品已经在利用这些方法。

随着业界不断突破摩尔定律的极限,Chiplet设计和异构集成的重要性将与日俱增,并将推动半导体制造、封装和系统设计领域的创新。

-对此,您有什么看法见解?-

-欢迎在评论区留言探讨和分享。-

![[AIGC] python遍历以及字符串的切片](https://img-blog.csdnimg.cn/img_convert/8453f15dec8eb46ca9be3ebe56879611.jpeg)