文章目录

- GIC CPU Interface 介绍

- CPU Interface 主要寄存器

GIC CPU Interface 介绍

A 系列处理器提供 5个管脚来实现中断,分别是:

nIRQ:物理普通中断nFIQ:物理快速中断nVIRQ:虚拟普通中断nVFIQ:虚拟快速中断vNMI不可屏蔽中断

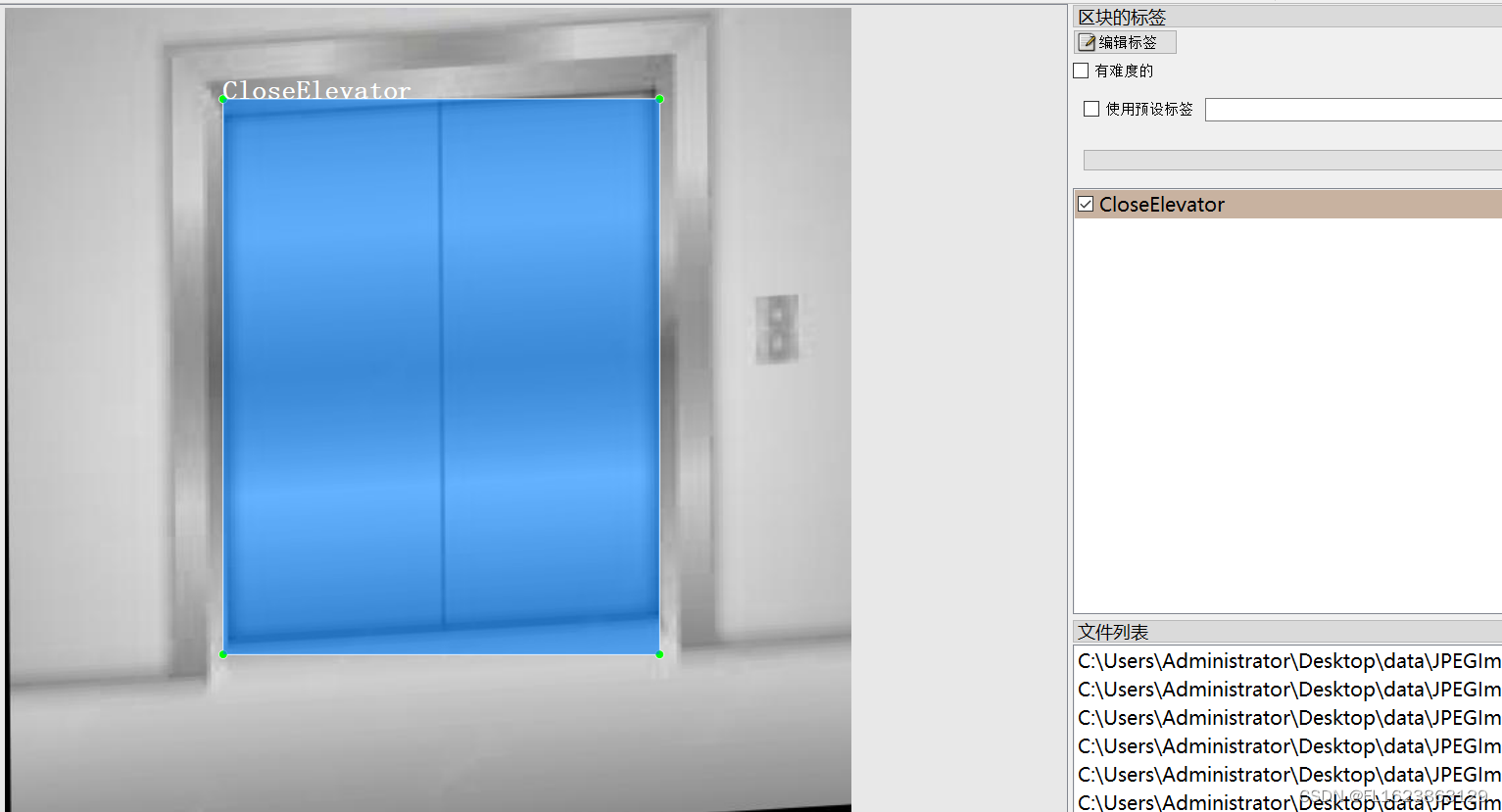

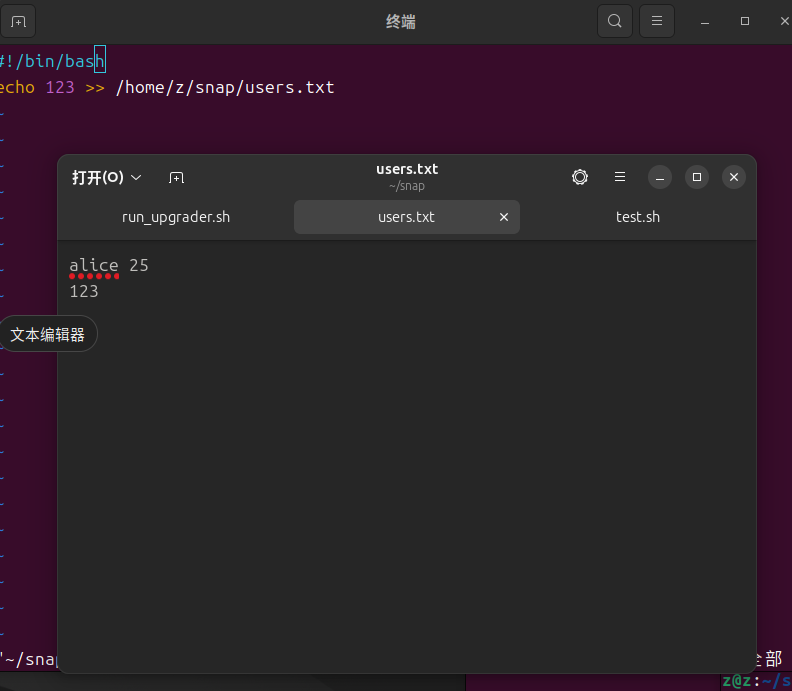

如下图所示:

其中虚拟中断是为了实现虚拟化而准备的,我们只看物理中断。

Core 提供给中断的物理管脚只有两个,中断会有成百上千个,GIC怎么把这些中断发送给core是一个问题。这时就需要 CPU interface了。CPU interface 将GIC发送的中断信息 通过IRQ/FIQ管脚发送给连接到 Core。

CPU interface 提供了以下的功能:

- 将中断请求发送给core

- 中断进行认可

- 中断完成识别

- 设置中断优先级屏蔽

- 定义中断抢占策略

- 决定当前处于pending状态最高优先级中断

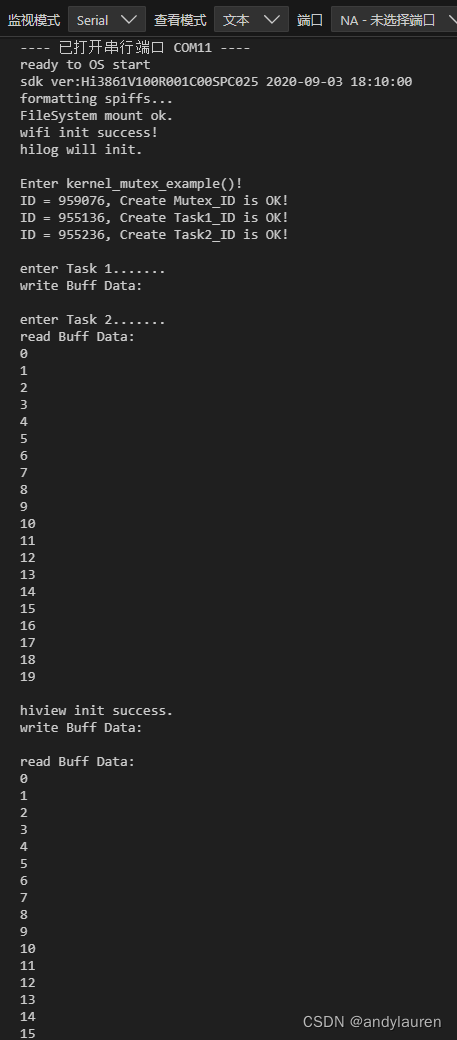

在GICv3架构中,CPU interface被抽离出来,实现在core内部的, 如下图所示

在GIC-600/GIC-700 中不包含CPU interface。这样做的好处是,可以减少中断响应的时间,并且减少系统总线的占用。对于众核SoC设计来说,其物理设计非常大,CPU interface 实现在core内部,也就意味着某些中断寄存器可以放在其内部,这样core就可以很快的访问到这些寄存器了。对于那些常用的寄存器,core不用跋山涉水的通过系统总线或片上网络去频繁访问GIC了。CPU interface与GIC之间,是通过专用的 AXI-stream 总线来传输信息的。

CPU Interface 主要寄存器

GIC-700 CPU接口包含多个控制和状态寄存器,用于配置和管理中断。以下是一些主要寄存器的简介:

- ICC_SRE_EL1/EL2/EL3(System Register Enable):用于控制系统寄存器接口与内存映射接口之间的选择。当启用系统寄存器接口时,可以通过系统寄存器访问GIC功能,而不是通过传统的内存映射方式。

- ICC_CTLR_EL1/EL3(CPU Interface Control Register):提供了控制CPU接口行为的配置选项,包含了如EOImode的设置,这影响了中断结束的信号方式。

- ICC_PMR_EL1(Priority Mask Register):定义了一个优先级阈值,只有高于此阈值的中断才能被送达给CPU。这允许操作系统或应用通过提高或降低该阈值来动态控制中断的处理。

- ICC_IAR0_EL1/ICC_IAR1_EL1(Interrupt Acknowledge Register):用于接收和确认当前待处理的最高优先级中断的ID,分别用于Group 0和Group 1的中断。

- ICC_EOIR0_EL1/ICC_EOIR1_EL1(End of Interrupt Register):用于表明一个中断已经被处理完成,分别用于结束Group 0和Group 1的中断。

- ICC_BPR0_EL1/ICC_BPR1_EL1(Binary Point Register):用于设置分组优先级的二进制点位置,决定了优先级字段的分组和子优先级的界限。

- ICC_IGRPEN0_EL1/ICC_IGRPEN1_EL1(Interrupt Group Enable Register):用于启用或禁用Group 0和Group 1中断的递送。

推荐阅读:

https://www.sohu.com/a/771753252_121124377

![[ARM-2D 专题]3. ##运算符](https://img-blog.csdnimg.cn/direct/20834e02c7a042aa9e5735c0e37deb9f.png#pic_center)