- The IJTAG Network Insertion Flow

- IJTAG Network Insertion Example

- Modification of the IJTAG Network Insertion Flow

- How to Edit or Modify a DftSpecification

- Edit or Modify Method

- DftSpecification Examples

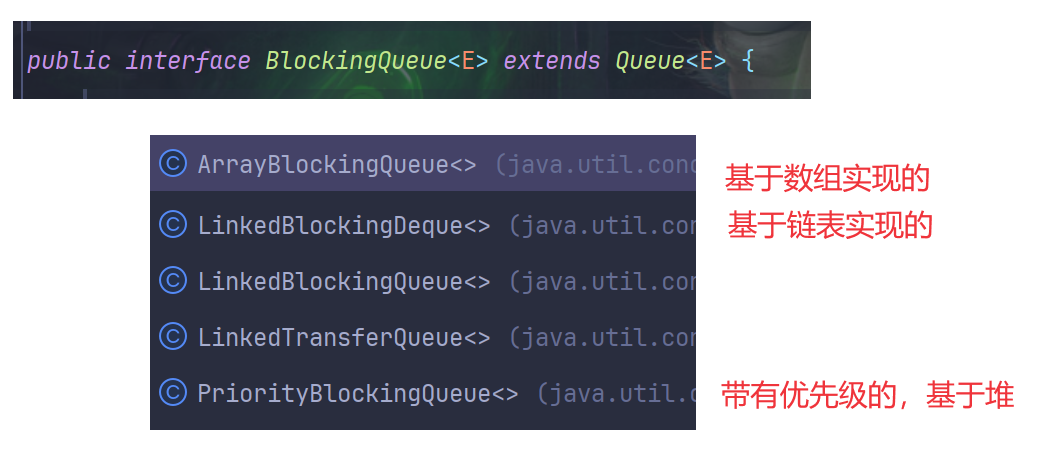

IJTAG Network Insertion 可以将已有的 instrument 连接起来,插入 SIBs、TDRs 和 ScanMuxes 等,以此来创建自己的 IJATG network。

IJTAG Network Insertion 可以将 network 连接到一个 TAP 控制器或者是设计中预先存在的 TAP 控制器。

IJTAG Network Insertion 的实现是直接使用 create_dft_specification 命令。工具会读取设计中所有 instrument 的 ICL 模型,然后根据 ICL 模型需要被如何访问来插入 SIB 或者是 TDR。

如果需要的话,可以对 IJATG network 网络进行编辑或者修改,以满足设计需求。

在完成设计编辑之后,可以使用 extract_icl 命令生成 IJATG 网络的 ICL 描述。IJATG network 插入之后,工具不会自动执行 ICL 提取,因为你可以在提取之前进行一些额外的编辑。

Tessent IJTAG 会生成并连接自己的TAP。如果 IJATG network 需要连接到已经存在的 TAP 控制器,需要提供该 TAP 控制器的 ICL 。

The IJTAG Network Insertion Flow

基本的 IJTAG Network Insertion 流程和对应的一些命令如下图所示:

如上图 5-1 所示,IJTAG Network Insertion Flow 是相对比较简单。因为你想要修改设计文件,所以就必须将工具的 context 设定为 dft,并且加载单元库、设计文件和需要使用的所有的 instrument 的 ICL (可自动加载)。

create_dft_specification 命令告诉工具创建 DftSpecification ;process_dft_specification 命令在生成或编辑设计文件之前会进行验证。

工具执行完 DftSpecification 中的内容之后,会输出一系列文件,这些文件中包含所有插入的 IJTAG network 对象(SIBs、TDRs 和 ScanMuxes)( ICL 和 verilog 两种格式)和所有修改后的设计文件。

虽然 IJTAG network 是使用 create_dft_specification 自动生成的,但是你可以使用编辑命令或者是display_specification命令打开 GUI 对生成的 DftSpecification 进行修改。

如前所示, IJTAG network 的 ICL 描述并不是自动生成的,因为你可能对其进行进一步的编辑。但是,因为所有的数据都保存在内存中,所以你可在后面使用 extract_icl命令执行 IJTAG Network 的提取过程。

IJTAG Network Insertion Example

IJTAG Network Insertion 的示例如下所述。

set context dft -no_rtl## Read the libraries

read_cell_library ./library/adk_complete.tcelllib

read_cell_library ./library/memory.atpglib## Read the netlist

read_verilog ./netlist/cpu_top_scan_tk.v

read_verilog ./generated/cpu_top_edt.v

read_verilog ./PLL/PLL.v -interface_only## Read ICL and PDL files before set_current_design

read_icl ./PLL/PLL.icl

dofile ./PLL/PLL.pdl

set_current_design cpu_top## set design level before running set_system_mode analysis

set_design_level chip## Specifiy the TAP pins using set_arrtibute_value

set_attribute_value tck_p -name function -value tck

set_attribute_value tdi_p -name function -value tdi

set_attribute_value tms_p -name function -value tms

set_attribute_value trst_p -name function -value trst

set_attribute_value tdo_p -name function -value tdoset_system_mode analysis

report_icl_modules## Automatically read any ICL from the directories that verilog is picked from

creat_dft_specification

report_config_data## Use display_specification to edit or modify the specification or use editing commands

## if neededprocess_dft_specification

extract_icl

exit

上述流程中,读入的 Verilog Netlist 已经插入了扫描链和带有 PLL 的 EDT IP。PLL 模块的 ICL 和 PDL 是在此之前单独生成并验证的。

因为 IJTAG network 是在 chip level 进行插入(set_design_level chip),所以在set_system_mode analysis之前需要指定 TAP pins。

使用 create_dft_specification 命令,PLL 和 EDT instruments 的 ICL 会被自动配置,然后插入到 IJTAG network 中。使用 report_config_data 可以报告该 network 中的内容。

如果 IJTAG network connection 是想要的,就可以使用 process_dft_specification 命令,否则可以使用编辑命令或者是打开 Configuration Data Visualizer 对其进行编辑。

最后一步就是使用 extract_icl 提取 set_current_design 所指定的 level 的 ICL。

【所以 DdfSpecification 是告诉工具如何进行 IJATG 插入,ICL 是在对完成插入的设计的 IJATG netwrok 的完整描述。如果当前设计是其他设计中的实例,在其他设计进行 IJATG netwrok 插入的时候,就可以使用当前设计的 ICL。ICL 中描述了当前设计中有哪些 Ijtag Instances(也可以叫 instrument) 以及它们之间的连接关系。】

Modification of the IJTAG Network Insertion Flow

大多数情况下,使用基本 IJTAG Network Insertion flow 即可,如果需要对其进行修改,可以使用如下内容。

How to Edit or Modify a DftSpecification

Edit or Modify Method

创建新的或者修改现有 DftSpecification 内容的两种方式:

- Configuration Data Visualizer

- ASCII text editor

- 命令行

1. 图形化界面

Configuration Data Visualizer 提供创建和修改 DftSpecification 内容的图形化界面。在打开窗口中,会以树状目录显示 DftSpecification 中已经定义的内容。

你可以查看 Specification 的层次结构,对其中的 elements 进行移动,创建新的 element,或者对现有的 elements 及进行修改。

如下图所示,左边是 DftSpecification 中的内容,右边是可配置的内容。

选中最顶层的 DftSpecification ,鼠标右键可以添加内容。因为每个 DftSpecification 中只能由 1 个 IjtagNetwork,当前设计中已经存在了,所有右键就不会有。

【这个 GUI 的字体好小】

使用下述命令可以创建一个新的 DftSpecification。

该命令会打开 Configuration Data Visualizer 并创建和 current design 相关联的 DftSpecification Wrapper。

如果想查看内存中的 DftSpecification,对其进行修改或者追加特定的 IJTAG network,也可以使用该命令。例如,使用该命令打开当前设计中一个 ID 为 good3 的 DftSpecification。

Tessent Shell 中和 IJTAG Network Insertion 相关命令的小结:

2. ASCII text editor

就是文本编辑器直接打开 DftSpecification 文件,然后按照规定的语法修改就行了。也没有什么好说的。

但是图形化界面和文本编辑器用的不是很多,刚开始学的时候,可以用一用,在实际的项目设计中,都是 flow,更多的是考虑在命令行或者脚本中对其进行修改。

3. 命令行修改

-

CMD1:

read_config_data -in $spec -from_sting {}这个命令可以将特定的字符串(

-from_sting后面{}中的内容,{}也可以是双引号)写入到 DftSepc 中,字符串需要遵循 DftSepc 的语法,字符串可以放在 Tcl 变量中。如果想在 IjtagNetwork 中的 SIB 下面新加入一个 tdr,就可以使用下述命令:

Tdr wrapper 中的所有内容都可以按照规定的语法在这里定义。

但是有一个问题是,双引号中的内容不能有变量,所有的变量都会当作普通字符串,如果想要使用变量,可以使用下述方式:

先将要插入的内容放到一个变量中,然后把变量给到命令。

-

CMD2:

add_config_element&set_config_value首先使用

add_config_element命令插入一个 wrapper :

然后在使用

set_config_value命令设定参数值。

该命令就是将一个 OCC wrapper 中的 clock_intercept_node 选项设置为$clk。使用

get_config_value -in_wrapper wrapper_object可以返回 wrapper 中那些内容可以通过set_config_value命令控制。set_config_value命令只能设计 wrapper 中已经存在的选项的值。如下图所示的 Tdr wrapper,绿色方框中的选型时默认存在的,可以直接设置,但是对于红色方框中的内容,如果是空的,就不能设置。如果有内容,如connection(0)已经存在了,那么是可以用该命令对其进行改的。也就是说,

set_config_value命令只能修改已经存在的内容,不能增加内容。

-

CMD3:

move_config_element、delete_config_element

具体用法:move_config_element object_spec [-in_wrapper wrapper_name_or_object]

就是移动 wrapper 的位置。【这里,可以移动和删除的内容可以是 wrapper 中的某一个配置】

DftSpecification Examples

这里给出了一些使用 DftSpecification 的 element 和 syntax 创建特殊的或者常用的 IJTAG Network Insertion 任务。【就是特定的需求在 IjtagNetwork中如何实现】

这里所有的示例都是基于使用 ASCII text editor 来创建 DftSpecification 。(就是直接在文本编辑器中对 DftSpec 文件进行修改。)

-----------------------------------------------------------------------

1. Connection of a Basic Scan Instrument to a SIB

-----------------------------------------------------------------------

在该示例中,有一个带有单一 scan interface 的 instrument ,你想要将其连接到 SIB。

Instrument

DftSpecification

使用 ID 为 S3 的 SIB wrapper,并在 SIB wrapper 中声明 instrument 的设计实例的路径。

不需要指定 scan-in、scan-out 等其他控制端口,因为工具会从 ICL 模型描述中找到这些信息。

instance path 必须存在于设计中,因为 Dftspecification 只是按照指定内容将其连接起来,而不会创建新的 design instance。

Result

IJTAG network 中会插入一个 SIB 。该 SIB 控制 instrument 实例 design2_I1/instrumentB_I1 的 SelectPort “sel” 。

该 instrument 的的端口连接关系:

- scan-out 被连接到 SIB 的第二个 scan-in;

- scan-in 连接到和 SIB 的第一个 scan-in 端口一样的 IJTAG scan chain;

类似的,instrument 的 scan-、capture- 和 update- 控制端口连接到 SIB 对应接收这些控制信号的端口上。Tck 也是也是如此。

---------------------------------------------------------------------------------------------------

2. Creation of a a Scan Instrument With More Than One ScanInterface

---------------------------------------------------------------------------------------------------

在该示例中,instrument 有两个 ScanInterface 定义。如果使用和示例1中一样的语法,工具不知道将 SIB 连接到哪一个 scan ports。因此,在这种情况下,必须声明所连接的 ScanInterface 的名字。

Instrument

DftSpecification

在该示例中,将 ScanInterface P2 连接到了 SIB “S3”,P1 连接到其他地方。

Sin(S3) {DesignInstance(design2_I1/instrumentC_I1) {scan_interface : P2 ;}

}

-------------------------------------------------------------

3. Connection of a Parallel Data Instrument

-------------------------------------------------------------

该示例展示如何将一个 instrument 的并行数据端口连接到 TDR。

Instrument

DftSpecification

将 instrument 连接到 TDR,使其成为 DftSpecification 的一部分。

Tdr(T3) {DataOutPorts {connection(6:0) : design2_I1/instrumentA_I1/INA[6:0] ;}DataInPorts {connection(7:0) : design2_I1/instrumentA_I1/OUT[7:0] ;}

}

Result

IJTAG network 中会有一个 8bit 的 TDR 寄存器。TDR 的 size 根据连接的需求自动确定确定。

TDR 包含 8 个数据输入端口,7 个数据输出端口和所有常用的控制信号端口。

instrument 的 7 个最低位(即 7 个数据输入端口)连接到 TDR 的 7 个数据输出端口;相似的,instrument 的 8 个数据输出端口连接到 TDR的 八个数据输入端口。8bit 的 TDR 寄存器从中捕获数据。

-------------------------------------------------------------------------------------

4. Connection of a Parallel Data Instrument to the Top Level

-------------------------------------------------------------------------------------

该示例展示如何将 instrument 的并行数据端口连接到 top level 的数据端口。

Instrument

DftSpecification

IjtagNetwork {DataOutPorts {connection(6:0) : design2_I1/instrumentA_I1/INA[6:0] ;}DataInPorts {connection(7:0) : design2_I1/instrumentA_I1/OUTA[7:0] ;}

}

如果 top-level 的输入端口已经连接到其他设计的端口,但是你还是希望保留上面定义的连接关系。

在这种情况下,工具会在 connected instrument pins 的 parent instance 中自动插入一个 mux ,在 DftSpecification 中描述与原始连接和新插入的连接之间的切换。

如果连接的引脚是 floating 或者 tied,或者连接到引脚的 net没有 fan-in (multiplexing : auto),工具则不会插入 mux。

所插入的 mux 的 select 连接到 top-level 创建的 DataInPort。

如果想要强制工具总是在 top-level 输入端口和 instrument 的引脚之间插入一个 mux,无论是否需要,需要使用 multiplexing 参数。当然,你也可以强制工具不插入 mux。

--------------------------------------------------------------------------

5. Connection of a Parallel Data Instrument to a TDR

--------------------------------------------------------------------------

该示例将 instrument 的并行数据端口连接到 TDR,这个 TDR 会在 specification processing 过程中插入。同时,也展示了 multiplexing 参数的使用。

和示例4一样,工具也会分析是否需要插入 mux。不同的是,这里插入的 mux 的 select 端口是连接到插入的 TDR 上的一个额外的 DataOutPort。

DftSpecification

Result

TDR 的 size 根据连接关系的需求自动确定。在该示例中,IJTAG network 网络中会包含一个 9bit 的 TDR 寄存器:8 个数据输入端口、8 个数据输出端口和所有的控制信号端口。

TDR register 的低 7 位连接到 TDR 的低 7 位数据输出端口,然后连接到 instrument 的 7 个数据输入端口。

相似的, instrument 的 8 个数据输出端口连接到 TDR 的 8 个数据输入端口,然后有 TDR register 的低 8 位来捕获数据。

TDR register 的第 9bit 和第 8 个数据输出端口用于 mux 的 select line。

6. Creation of a TDR With More Bits Than Needed for the Current Specification

基于示例 5,该示例说明当 specification processing 中连接关系未知时,如何在 TDR 中保留额外的 bits。

可以使用参数 length 来指定 TDR register 的 bits 数,但是该数不能小于满足连接关系所需要的最小 bit 数。

DftSpecification

--------------------------------------------------

7. Connection of an EDT Controller

--------------------------------------------------

------------------------------------------------

8. Connection to a TAP Controller

------------------------------------------------

------------------------------------------------

9. Creation of a Hierarchy of SIBs

------------------------------------------------

-----------------------------------

10. Usage of a ScanMux

-----------------------------------

----------------------------------------------------------------------------------------------------

11. Move of a SIB, TDR, or ScanMux Deeper Into the Design Hierarchy

----------------------------------------------------------------------------------------------------

-------------------------------------------------------------------------------------

12. Change of the Instance Name of a SIB, TDR, or ScanMux

--------------------------------------------------------------------------------------

--------------------------------------------------------------------------------------------------------

13. Change of the Design and ICL Port Names of a SIB, TDR, or ScanMux

--------------------------------------------------------------------------------------------------------