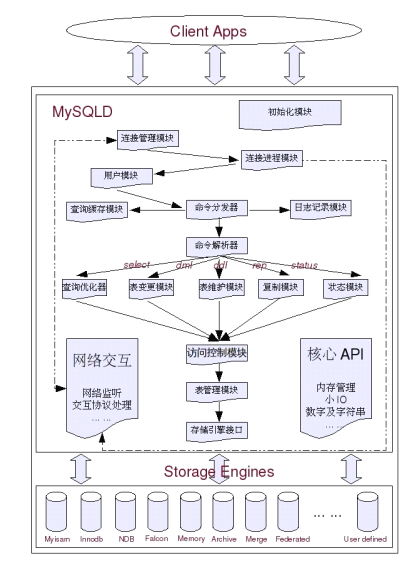

JESD204B基础概念

204B包含传输层,链路层,物理层。

应用层是对 JESD204B 进行配置的接口,在标准协议中是不含此层,只是为了便于理解,添加的一个层。

协议层指工程中生成的IP核JESD204B,负责处理输入的用户数据。

传输层:采样数据映射为数据帧,将数据封装组包。在IP核JESD204B中实现

链路层:传输数据链路建立。IP核JESD204B与IP核JESDPHY之间的数据传输可以认为是链路建立

物理层(PHY):数据发送与接收。一端连接IP核JESD204B,另一端直接与AD/DA芯片相连接的物理端口

AD/DA采样率与信号频率关系

DAC:

ADC:

同步方式

子类1与子类2使用SYSREF(参考时钟)与SYNC(同步信号)进行数据同步,子类1与0支持确定性延迟。

SYSREF上升沿同时,发送一个或多个多帧。

子类1与子类2模式下的工作时钟如图所示(SYSREF_CLK为参考时钟,DEVICE_CLK为工作时钟,SYNC为同步信号):

SYNC信号为低表示正在同步(同步码),为高表示同步完成。当SYSREF_CLK信号在上升沿时,发送一个或多个多帧。

物理层

在工程中指生成的JESD204B_PHY的IP核,该IP核用来连接DAC的物理接口,配合JESD204B的IP核使用。如图所示:

传输层

在使用204B接口进行数据传输之前需要确定参数,如图所示:

主要参数意义

F

每一帧数据中的字节个数,如图所示,F=7时,表示7列数据,每一列为8位宽数据。如图所示。(CCCC表示控制码)

N

AD/DA转换器分辨率。N=16时,表示一个采样点16bit。

M

AD/DA转换器中单元个数,M 个转换单元一共 M 个采样点,每一个采样点有 N 位数据,将 M 个采样点线性的排列在一横排高位在前,低位在后。一个AD/DA芯片转换M个通道。M=1表示一个芯片一个通道。

如图所示,M=16时,16个采样点Cr0~Cr15。

CS

控制位数,控制数据是几位。cs=2时,图中c1与c0即为控制位。

T

tail bit,单帧中每一个采样点的数据不满足8位时,在每个采样点后填充数据。

N’

N’=N+CS+T;多位数据扩展多个无效/封装位的位宽。若无封装和无效位,N=N’。实际传输的采样率为N’。

HD

HD=0低密度模式,一个采样点在一条链路Lane传输。HD=1高密度模式,一个采样点在多条链路Lane传输。 HD 的值决定了一个采样点最后是映射到一个单独的 LANE,还是映射到多个 LANE。

如下图所示,HD=0时,Cr0~Cr15共16个采样点每个点在一条线传输。

HD=1,采样点Cr2与Cr10在两条Lane线传输。

L个链路通道分为CF个组,每个组包含L/CF条链路通道,每组传输 M*S/CF 个采样点。

L

数据传输通道。(链路)设置Lane个数。(L个SERDES传输接口 )

S

每帧数据中的采样点数。JESD204B 数据映射按照 S 的取值分为两种情况:正常采样情况下的数据映射和过采样情况下的数据映射。当 S=1,是正常采样情况下的数据映射;当 S>1,是过采样情况下的数据映射。正常采样情况下,帧时钟等于采样时钟;过采样情况下,采样时钟是帧时钟的 S 倍。(一帧中包含S个采样点数)

CF

控制字个数,一个控制字8位。如上图所示,CF=1表示一列中一个8位宽控制字Cr0:3[c1:c0]。

如下图所示。CF=2表示一列中两个8位宽控制字Cr0:3[c1:c0]、Cr8:11[c1:c0]。

控制字的位数: MSCS/CF

![[外链图片转存中...(img-CVpJ4Fpl-1663312811322)]](https://i-blog.csdnimg.cn/blog_migrate/ad5f2b1625cd6379a134faed4283116f.png)

K

每个多帧的帧数, 1 到 32 之间的整数。(S个采样点组成一帧,K个帧组成多帧)。当SYSREF_CLK信号在上升沿时,发送一个或多个多帧(单位)。

F

将所有的数据按 8 位一个字节划分,共得到 F 个字节。这F字节的数据在通道内传输。

链路层

链路层包括扰码器加扰,链路建立, 8b/10b 编码。

码器加扰

可选,对数据进行0/1均衡。

链路建立

链路建立包含代码组同步,初始通道对齐,用户数据传输。此部分IP核做好直接使用即可。Sync信号为低(发送端发送同步码),接收端Sync为高表示同步完成。

代码组同步

使用 CDR 技术恢复位时钟,对每一个链路上的数据进行位同步和帧同步。

初始通道对齐

识别出每一个链路上数据的多帧开始,并使用缓存器对所有链路的数据进行缓存,使所有链路上的数据对齐。

JESD204B应用

信号时钟之间的关系。如图所示。

以下数据有点不对,仅供参考。

接口工作内核时钟 X 接口位宽 == FPGA内部数据处理时钟 X 存储位宽

查看AD/DA芯片手册,确定mode,如图所示。假设选择mode11。

假设设置DAC输出信号F: F=250M

采样率=信号周期点数*信号F: 输出信号采样率=16*250M=4G

设置转化单元个数M,几个DAC单元: M=2。

设置Lane通道个数: Lane=8

设置子类模式: 子类1

设置DAC插值interpolation个数 interpolation=2 (设置信号周期点数减半,输入信号周期点数=8,插值后DAC输出信号周期点数=16)

设置Link(AD/DA芯片手册设置)

确定Lane速率(求DAC每秒传多个bit)(FPGA输出数字信号传给DAC):Tx与PHY两个IP设置中LineRate速率一致。

假设DAC输出信号频率F=250M,DAC输出周期点数16个点。DAC芯片使用M=2个DAC转换单元,内插为2.

204B接口每秒传输给DAC点数:F*N/2个点(interpolation=2,F*N为实际采样率 )。(250M*8=2G)

DAC分辨率16bit,接口每秒传输F*N/2*16 bit。(2G*16bit=32Gbit)

M个DAC转换器,接口每秒传输M*[F*N/2*16 ]bit。(32Gbit*2=64Gbit)

数据通过接口传输前使用8b/10b编码,每秒传输{M*[F*N/2*16 ]}*10/8bit。(64G*10/8=80G)

mode11使用Lane=8条线路传输数据。每条线路每秒传输的数据量:10/8*{M*[F*N/2*16 ]}/8bit。(80G/8=10G)

可得物理LineRate=10G。

JESD204IP与PHY_IP(内核时钟tx_core_clk):lane速率/40。(10G/40=250M)

Device clock():204B工作时钟 时钟芯片输入

SYSREF:参考时钟 上升沿同步发数据 时钟芯片输入

Sync:同步完成信号 是否同步完成

JESD204B同步过程

配置204BIP: CPLL(线速率小于8G),QPLL(线速率大于8G)

这些同步阶段中的每一个都是使用32位同步字实现

没有码组同步(CGS)或初始通道对齐序列(ILAS)

传输层:帧边界会不与块边界对齐,存在帧不是恰好包括8个八位字的可能

参考添加链接描述

参考添加链接描述

同步报头同步

扩展多块同步

扩展多块对齐

AXI协议应用

主机(master)从机(slave)

AXI4:支持突发256长度传输。

AXI4-Lite:简单通信,低吞吐量,接口较少。不支持突发。

AXI4-Stream:高速流数据。不要地址,可以无限突发长度。

AXI4和AXI4-Lite有五个通道:

读写地址通道,读写数据通道,写响应通道。

基本示例参考:三个示例

接口参考:接口描述

JESD204C简单环回实验

JESD204C协议发送tx数据,rx解码恢复数据。

系统框图

txjesd_init: 初始化模块

JESD204_TxInitcode/JESD204_RxInitcode:初始化控制模块

JESD204_Interface_Axi : AXI接口转化模块

jesd204c_tx/jesd204c_rx : 例化两个JESD204C和JESD204PHY IP核

txinitcode_save/rxinitcode_save: 查找表;通过AXI协议读写JESD204C IP核地址完成初始化

初始化过程

JESD204_TxInitcode/JESD204_RxInitcode模块状态机

TX初始化过程

1:读操作:读AXI4-Lite Address 0X020 读IP核是否复位完成(或者jesd204c_0 IP核输出tx_aresetn高电平表示可以读写操作)

2:读操作:读AXI4-Lite Address 0X000 读IP核版本

3:写操作:写AXI4-Lite Address 0X030 设置扩展多块的E值

4:写操作:写AXI4-Lite Address 0X020 bit[0]位写1,使能IP核复位

5:写操作:写AXI4-Lite Address 0X020 bit[0]位写0,使能IP核复位恢复

6:读操作:读AXI4-Lite Address 0X020 读IP核是否复位完成

7:写操作:写AXI4-Lite Address 0X024 bit[0]位写1表示使能AXI4-Stream CMD接口 bit[1]位写1表示使能AXI4-Stream data接口

8:jesd204c_0 IP核tx_tready端口输出高电平表示可以发送数据

Rx初始化过程

1:读操作:读AXI4-Lite Address 0X020 读IP核是否复位完成(或者jesd204c_1 IP核输出rx_aresetn高电平表示可以读写操作)

2:读操作:读AXI4-Lite Address 0X000 读IP核版本

3:写操作:写AXI4-Lite Address 0X030 设置扩展多块的E值

4:写操作:写AXI4-Lite Address 0X044 设置接收buffer提前释放个数

5:写操作:写AXI4-Lite Address 0X020 bit[0]位写1,使能IP核复位

6:写操作:写AXI4-Lite Address 0X020 bit[0]位写0,使能IP核复位恢复

7:读操作:读AXI4-Lite Address 0X060 寄存器值h0x02 h0x12 h0x32

读到h0x32表示同步成功

8: 写操作:写AXI4-Lite Address 0X024 bit[0]位写1表示使能AXI4-Stream CMD接口 bit[1]位写1表示使能AXI4-Stream data接口 jesd204c_1 IP核rx_tvalid端口输出高电平表示可以接收数据

9:读操作:读AXI4-Lite Address 0X400 查看lan0 rx buffer缓冲区数据个数

读AXI4-Lite Address 0X480 查看lan1 rx buffer缓冲区数据个数

读AXI4-Lite Address 0X500 查看lan2 rx buffer缓冲区数据个数

读AXI4-Lite Address 0X580 查看lan3 rx buffer缓冲区数据个数

读AXI4-Lite Address 0X600 查看lan4 rx buffer缓冲区数据个数

读AXI4-Lite Address 0X680 查看lan5 rx buffer缓冲区数据个数

读AXI4-Lite Address 0X700 查看lan6 rx buffer缓冲区数据个数

读AXI4-Lite Address 0X780 查看lan7 rx buffer缓冲区数据个数

仿真

仿真文件

根据仿真过程编写仿真文件

`timescale 1ns/1ns

`define CLK_PER 10module jesd204txrx_tb();reg rst_n ;

reg clk ;

wire clk_out1 ;

wire clk_out2 ;

wire locked0 ;

wire locked1 ;

wire locked2 ;

wire clk_out3 ;

wire clk_out4 ;

wire ok ;

// wire tx_init_done ;

wire tx_tready ;

wire [511:0] rx_tdata ;

wire rx_tvalid ;

wire rx_soemb ;

wire rx_crc_err ;

wire rx_emb_err ;

wire [255 : 0]rx_cmd_tdata ;

wire rx_cmd_tvalid ;

wire [7 : 0] rx_cmd_tuser ;

// wire rx_inter_error ;

// wire rx_init_done ;

wire [7:0] txp_out ;

wire [7:0] txn_out ;

reg [511:0] tx_tdata ;

wire tx_soemb ;

wire tx_wr_done ;

wire rx_wr_done ;

wire [31:0] tx_rd_data ;

wire [31:0] rx_rd_data ;

reg tx_wr_op ;

reg tx_rd_op ;

reg rx_wr_op ;

reg rx_rd_op ;

reg [15:0] tx_wrsa_addr ;

reg [15:0] tx_rdsa_addr ;

reg [15:0] rx_wrsa_addr ;

reg [15:0] rx_rdsa_addr ;

wire rx_idle_signal ;

wire tx_idle_signal ;

wire rx_init_start ;

wire tx_init_start ;

reg [511:0] rxrd_baladata ;

reg rxrd_corrt ;

reg correct;

reg [15:0] cnt ;assign ok = locked0 && locked1 && locked2;

initial clk = 1;

always #(`CLK_PER/2) clk = ~clk;/*****************************inst*********************************/clk_wiz_0 clk_wiz_0_inst(.clk_in1(clk), //100M.clk_out1(clk_out1), //187.5M.clk_out2(clk_out2), //10M.locked(locked0)); clk_wiz_1 clk_wiz_1_inst(.clk_in1(clk),.clk_out1(clk_out3), // 82.5M.locked(locked1) // output locked); clk_wiz_2 clk_wiz_2_inst(.clk_in1(clk),.clk_out1(clk_out4), // 82.5M 140M?? 300M??NO 160M?? 200M??.locked(locked2) // output locked); jesd204c_tx #(.C_M_AXI_ADDR_WIDTH(12), //12.C_M_AXI_DATA_WIDTH(32) //32)jesd204c_tx_inst(.tx_wr_op(tx_wr_op) , .tx_rd_op(tx_rd_op) ,.tx_wrsa_addr(tx_wrsa_addr) ,.tx_rdsa_addr(tx_rdsa_addr) ,.tx_wr_done(tx_wr_done) ,.tx_rd_data(tx_rd_data) ,.tx_idle_signal(tx_idle_signal) ,.tx_init_start(tx_init_start) ,.tx_core_reset (~rst_n), .tx_core_clk (clk_out1), //187.5M.tx_sysref (clk_out3), //82.5M.axi_clk (clk), //100.rst (~rst_n),.tx_tdata (tx_tdata),.tx_cmd_tdata (256'b0),.tx_cmd_tvalid (1'b0),.refclk (clk_out4), //82.5M .drpclk (clk), //100// .tx_init_done (tx_init_done),.tx_soemb (tx_soemb),.tx_tready (tx_tready),.txp_out (txp_out),.txn_out (txn_out));jesd204c_rx #(.C_M_AXI_ADDR_WIDTH(12), //12.C_M_AXI_DATA_WIDTH(32) //32) jesd204c_rx_inst(.rx_wr_op(rx_wr_op) ,.rx_rd_op(rx_rd_op) ,.rx_wrsa_addr(rx_wrsa_addr) ,.rx_rdsa_addr(rx_rdsa_addr) ,.rx_wr_done(rx_wr_done) ,.rx_rd_data(rx_rd_data) ,.rx_idle_signal(rx_idle_signal) ,.rx_init_start(rx_init_start) ,.rx_sysref (clk_out3), //82.5M.rx_core_clk (clk_out1), //187.5.axi_clk (clk), //100.rst (~rst_n),.refclk (clk_out4), //82.5M.drpclk (clk), //100.rxp_in (txp_out), .rxn_in (txn_out), .rx_tdata (rx_tdata), .rx_tvalid (rx_tvalid ), .rx_soemb (rx_soemb ), .rx_crc_err (rx_crc_err ), .rx_emb_err (rx_emb_err ), .rx_cmd_tdata (rx_cmd_tdata ), .rx_cmd_tvalid (rx_cmd_tvalid ),.rx_cmd_tuser (rx_cmd_tuser ),.rx_cmd_tready (1'b0)// .rx_inter_error (rx_inter_error ),// .rx_init_done (rx_init_done ) );/*****************************************************************/

always @(posedge clk_out1 or negedge rst_n)if(!rst_n)tx_tdata <= 512'b0;else if(tx_tready && rx_tvalid)tx_tdata <= tx_tdata + 'd1000;//同步之后固定延迟

always @(posedge clk_out1 or negedge rst_n)if(!rst_n)rxrd_baladata <= 512'b0;else if(cnt == 16'd36)rxrd_baladata <= rxrd_baladata + 'd1000; always @(posedge clk_out1 or negedge rst_n)if(!rst_n)cnt <= 16'b0;else if(tx_tready && rx_tvalid)beginif(cnt == 'd36)cnt <= cnt;elsecnt <= cnt + 'b1 ; endelsecnt <= 16'b0;always @(posedge clk_out1 or negedge rst_n)if(!rst_n) correct <= 1'b0;else if(rxrd_baladata == rx_tdata)correct <= 1'b0;elsecorrect <= 1'b1;always @(posedge clk_out1 or negedge rst_n) if(!rst_n)rxrd_corrt <= 1'b0;else if(rx_rd_data == 32'h32)rxrd_corrt <= 1'b1;elserxrd_corrt <= rxrd_corrt;initial

beginrst_n = 0;#(`CLK_PER*5 + 1);@(posedge ok)rst_n = 1;rx_wr_op = 0;rx_rd_op = 0;rx_wrsa_addr = 0;rx_rdsa_addr = 0;@(posedge rx_init_start) #(`CLK_PER + 5); rx_wr_op = 1; //写E值rx_wrsa_addr = 1;#(`CLK_PER); rx_wr_op = 0;@(posedge rx_idle_signal) #(`CLK_PER*2); rx_wr_op = 1; //写接收缓冲区0rx_wrsa_addr = 5;#(`CLK_PER); rx_wr_op = 0;@(posedge rx_idle_signal) #(`CLK_PER*2); rx_wr_op = 1; //复位rx_wrsa_addr = 42;#(`CLK_PER); rx_wr_op = 0;@(posedge rx_idle_signal) #(`CLK_PER*2); rx_wr_op = 1; //复位恢复rx_wrsa_addr = 43;#(`CLK_PER); rx_wr_op = 0;@(posedge rx_init_start) #(`CLK_PER*2); rx_rd_op = 1; //读通道状态 等待同步完成rx_rdsa_addr = 13;@(posedge rxrd_corrt)#(`CLK_PER); rx_rd_op = 0; // @(posedge tx_tready) // test#(`CLK_PER*20); rx_wr_op = 1; //使能读通道rx_wrsa_addr = 0;#(`CLK_PER); rx_wr_op = 0; @(posedge rx_idle_signal) #(`CLK_PER*2); rx_rd_op = 1; //读每个通道接收缓冲器数据量lane0rx_rdsa_addr = 16;#(`CLK_PER); rx_rd_op = 0;@(posedge rx_idle_signal) #(`CLK_PER*2); rx_rd_op = 1; //读每个通道接收缓冲器数据量lane1rx_rdsa_addr = 23;#(`CLK_PER); rx_rd_op = 0;@(posedge rx_idle_signal) #(`CLK_PER*2); rx_rd_op = 1; //读每个通道接收缓冲器数据量lane2rx_rdsa_addr = 30;#(`CLK_PER); rx_rd_op = 0;@(posedge rx_idle_signal) #(`CLK_PER*2); rx_rd_op = 1; //读每个通道接收缓冲器数据量lane3rx_rdsa_addr = 37;#(`CLK_PER); rx_rd_op = 0;@(posedge rx_idle_signal) #(`CLK_PER*2); rx_rd_op = 1; //读每个通道接收缓冲器数据量lane4rx_rdsa_addr = 44;#(`CLK_PER); rx_rd_op = 0;@(posedge rx_idle_signal) #(`CLK_PER*2); rx_rd_op = 1; //读每个通道接收缓冲器数据量lane5rx_rdsa_addr = 51;#(`CLK_PER); rx_rd_op = 0;@(posedge rx_idle_signal)#(`CLK_PER*2); rx_rd_op = 1; //读每个通道接收缓冲器数据量lane6rx_rdsa_addr = 58;#(`CLK_PER); rx_rd_op = 0;@(posedge rx_idle_signal)#(`CLK_PER*2); rx_rd_op = 1; //读每个通道接收缓冲器数据量lane7rx_rdsa_addr = 65;#(`CLK_PER); rx_rd_op = 0;@(posedge rx_idle_signal)#(`CLK_PER*200);$stop;end

initial

begintx_rd_op = 0;tx_wr_op = 0;tx_rdsa_addr = 0;tx_wrsa_addr = 0;@(posedge tx_init_start)#(`CLK_PER + 5); tx_rd_op = 1; //读版本tx_rdsa_addr = 0 ;#(`CLK_PER);tx_rd_op = 0;@(posedge tx_idle_signal) #(`CLK_PER*10); tx_wr_op = 1; //配置E值tx_wrsa_addr = 1 ; #(`CLK_PER);tx_wr_op = 0;@(posedge tx_idle_signal) #(`CLK_PER*10);tx_wr_op = 1; //复位tx_wrsa_addr = 40 ; #(`CLK_PER);tx_wr_op = 0;@(posedge tx_idle_signal) #(`CLK_PER*2);tx_wr_op = 1; //复位恢复tx_wrsa_addr = 41 ; #(`CLK_PER);tx_wr_op = 0;@(posedge tx_init_start) #(`CLK_PER*20);//等待rx同步完成@(posedge rxrd_corrt) #(`CLK_PER*50);tx_wr_op = 1; //使能AXI stramtx_wrsa_addr = 0 ; #(`CLK_PER);tx_wr_op = 0;#(`CLK_PER*200);$stop;endendmodule

TX初始化主状态机文件

`timescale 1ns / 1psmodule JESD204_TxInitcode#(parameter integer M_AXI_ADDR_WIDTH = 32,parameter integer M_AXI_DATA_WIDTH = 32)

(input rst ,input clk ,//user interfaceinput wr_op ,input [15:0] tx_wrsa_addr ,input rd_op ,input [15:0] tx_rdsa_addr ,output wr_done ,output reg [M_AXI_DATA_WIDTH - 1 : 0] tx_rd_data , //axi interfaceoutput reg [M_AXI_DATA_WIDTH - 1 : 0] wr_data ,output reg [M_AXI_ADDR_WIDTH - 1 : 0] wr_addr ,output reg waddate_valid ,input wr_ok ,output reg [M_AXI_ADDR_WIDTH - 1 : 0] rd_addr ,output reg rdaddr_valid ,input [M_AXI_DATA_WIDTH - 1 : 0] rd_data ,input rdata_valid ,output reg idle_signal );localparamidle = 5'b0_0000,wrdata = 5'b0_0001,waitwrdata = 5'b0_0010,rdrdy = 5'b0_0100,rddata = 5'b0_1000,waitrddata = 5'b1_0000;reg [4:0] state ;reg [15:0] wr_sa_addr ;reg [15:0] rd_sa_addr ;reg sa_enable ;wire initata_valid ;wire [M_AXI_DATA_WIDTH-1 : 0] initwr_data;wire [M_AXI_ADDR_WIDTH-1 : 0] initwr_addr;wire [M_AXI_ADDR_WIDTH-1 : 0] initrd_addr;reg wr_op_reg ;reg rd_op_reg ;assign wr_done = wr_ok ;always @(posedge clk or posedge rst)if(rst)wr_op_reg <= 1'b0;else wr_op_reg <= wr_op;always @(posedge clk or posedge rst)if(rst)rd_op_reg <= 1'b0;else rd_op_reg <= rd_op; always @(posedge clk or posedge rst)beginif(rst)beginstate <= idle ;wr_data <= 'b0;wr_addr <= 'b0;waddate_valid <= 1'b0;rd_addr <= 'b0;rdaddr_valid <= 1'b0;idle_signal <= 1'b0;sa_enable <= 1'b0;wr_sa_addr <= 16'b0;rd_sa_addr <= 16'b0;endelsebegincase(state)idle :beginwr_data <= wr_data;wr_addr <= wr_addr;waddate_valid <= 1'b0;rd_addr <= rd_addr;rdaddr_valid <= 1'b0;idle_signal <= 1'b1;sa_enable <= 1'b0;wr_sa_addr <= 16'b0;rd_sa_addr <= 16'b0;if(wr_op_reg)state <= wrdata;else if(rd_op_reg)state <= rdrdy;elsestate <= idle ;endwrdata :beginidle_signal <= 1'b0;sa_enable <= 1'b1;wr_sa_addr <= tx_wrsa_addr ; state <= waitwrdata;endwaitwrdata :beginif(wr_ok)beginstate <= idle;endelsebeginsa_enable <= 1'b0;wr_sa_addr <= wr_sa_addr;waddate_valid <= initata_valid;wr_data <= initwr_data;wr_addr <= initwr_addr; endendrdrdy :beginidle_signal <= 1'b0;sa_enable <= 1'b1;rd_sa_addr <= tx_rdsa_addr;state <= rddata;endrddata :beginrd_sa_addr <= rd_sa_addr ;sa_enable <= 1'b0;if(initata_valid)beginrd_addr <= initrd_addr;rdaddr_valid <= 1'b1;state <= waitrddata;endelsestate <= rddata;endwaitrddata :beginif(rdata_valid)begintx_rd_data <= rd_data ;state <= idle;endelserdaddr_valid <= 1'b0;enddefault :beginstate <= idle ; endendcaseendendtxinitcode_save#(.M_AXI_ADDR_WIDTH(M_AXI_ADDR_WIDTH),.M_AXI_DATA_WIDTH(M_AXI_DATA_WIDTH))txinitcode_save_inst(.clk (clk),.rst (rst),.wr_sa_addr (wr_sa_addr),.rd_sa_addr (rd_sa_addr),.sa_enable (sa_enable),.initwr_data (initwr_data),.initwr_addr (initwr_addr),.initrd_addr (initrd_addr),.initata_valid (initata_valid)); endmodule初始化接口文件

将AXI接口简化对接初始化控制状态机

`timescale 1 ns / 1 psmodule JESD204_Interface_Axi #(//读写事务初始地址位宽parameter integer C_M_AXI_ADDR_WIDTH = 32,// 主机读写数据位宽parameter integer C_M_AXI_DATA_WIDTH = 32)(//wr address channelinput [C_M_AXI_ADDR_WIDTH - 1 : 0] wr_addr,//wr data channelinput [C_M_AXI_DATA_WIDTH - 1 : 0] wr_data,input waddate_valid ,//wr ack one clock cycleoutput wr_ok ,//rd address channelinput [C_M_AXI_ADDR_WIDTH - 1 : 0] rd_addr,input rdaddr_valid ,//rd data channel output reg [C_M_AXI_DATA_WIDTH-1 : 0] rd_data,output rdata_valid , //one clock cycleoutput reg error_reg ,input wire M_AXI_ACLK,input wire M_AXI_ARESETN,///写地址通道//主机发出的写地址通道端口output reg [C_M_AXI_ADDR_WIDTH-1 : 0] M_AXI_AWADDR,//写入通道保护类型。//该信号指示事务的特权和安全级别,以及事务是数据访问还是指令访问。0output wire [2 : 0] M_AXI_AWPROT,// 写地址通道有效 output wire M_AXI_AWVALID,//写地址通道input wire M_AXI_AWREADY,// 写数据通道output reg [C_M_AXI_DATA_WIDTH-1 : 0] M_AXI_WDATA,// 写入选通 all 1output wire [C_M_AXI_DATA_WIDTH/8-1 : 0] M_AXI_WSTRB, // 写数据有效output wire M_AXI_WVALID,// 写数据应答信号input wire M_AXI_WREADY,//写响应通道 表示写传输状态0input wire [1 : 0] M_AXI_BRESP,//写响应有效input wire M_AXI_BVALID,// 主机接收写响应信号后应答output wire M_AXI_BREADY,//读地址通道output reg [C_M_AXI_ADDR_WIDTH-1 : 0] M_AXI_ARADDR,// 保护类型。该信号指示事务的特权和安全级别,以及事务是数据访问还是指令访问。output wire [2 : 0] M_AXI_ARPROT,//读地址有效output wire M_AXI_ARVALID,//读地址应答信号input wire M_AXI_ARREADY,// 读数据通道input wire [C_M_AXI_DATA_WIDTH-1 : 0] M_AXI_RDATA,// 读响应读状态input wire [1 : 0] M_AXI_RRESP,// 读数据有效input wire M_AXI_RVALID,// 读数据应答output wire M_AXI_RREADY);//write address validreg axi_awvalid;//write data validreg axi_wvalid;//read address validreg axi_arvalid;//read data acceptancereg axi_rready;//write response acceptancereg axi_bready;wire write_resp_error;wire read_resp_error;assign M_AXI_AWPROT = 3'b000;assign M_AXI_AWVALID = axi_awvalid;//Write Data(W)assign M_AXI_WVALID = axi_wvalid;//Set all byte strobes in this exampleassign M_AXI_WSTRB = 4'b1111;//Write Response (B)assign M_AXI_BREADY = axi_bready;assign wr_ok = axi_bready;//Read Address (AR)assign M_AXI_ARVALID = axi_arvalid;assign M_AXI_ARPROT = 3'b001;//Read and Read Response (R)assign M_AXI_RREADY = axi_rready;assign rdata_valid = axi_rready;always @(posedge M_AXI_ACLK) if (M_AXI_ARESETN == 0) error_reg <= 1'b0;else if(write_resp_error || read_resp_error)error_reg <= 1'b1;elseerror_reg <= 1'b0;//--------------------//Write Address Channel//--------------------always @(posedge M_AXI_ACLK) begin if (M_AXI_ARESETN == 0) begin axi_awvalid <= 1'b0; end else begin if (waddate_valid) begin axi_awvalid <= 1'b1; end else if (M_AXI_AWREADY && axi_awvalid) begin axi_awvalid <= 1'b0; end end end always @(posedge M_AXI_ACLK) begin if (M_AXI_ARESETN == 0) begin M_AXI_AWADDR <= 0; end else if (waddate_valid) begin M_AXI_AWADDR <= wr_addr ; end end //--------------------//Write Data Channel//--------------------always @(posedge M_AXI_ACLK) begin if (M_AXI_ARESETN == 0) begin axi_wvalid <= 1'b0; end else if (waddate_valid) begin axi_wvalid <= 1'b1; end else if (M_AXI_WREADY && axi_wvalid) begin axi_wvalid <= 1'b0; end end always @(posedge M_AXI_ACLK) begin if (M_AXI_ARESETN == 0) begin M_AXI_WDATA <= 'b0; end else if(waddate_valid)M_AXI_WDATA <= wr_data; end//----------------------------//Write Response (B) Channel//----------------------------always @(posedge M_AXI_ACLK) begin if (M_AXI_ARESETN == 0) begin axi_bready <= 1'b0; end else if (M_AXI_BVALID && ~axi_bready) begin axi_bready <= 1'b1; end // deassert after one clock cycle else if (axi_bready) begin axi_bready <= 1'b0; end else axi_bready <= axi_bready; end //Flag write errors assign write_resp_error = (axi_bready & M_AXI_BVALID & M_AXI_BRESP[1]);//----------------------------//Read Address Channel//----------------------------always @(posedge M_AXI_ACLK) begin if (M_AXI_ARESETN == 0) begin M_AXI_ARADDR <= 0; end else if (rdaddr_valid) begin M_AXI_ARADDR <= rd_addr ; end end always @(posedge M_AXI_ACLK) begin if (M_AXI_ARESETN == 0) begin axi_arvalid <= 1'b0; end else if (rdaddr_valid) begin axi_arvalid <= 1'b1; end else if (M_AXI_ARREADY && axi_arvalid) begin axi_arvalid <= 1'b0; end end //--------------------------------//Read Data (and Response) Channel//--------------------------------always @(posedge M_AXI_ACLK) begin if (M_AXI_ARESETN == 0) begin axi_rready <= 1'b0; end else if (M_AXI_RVALID && ~axi_rready) begin axi_rready <= 1'b1; end // deassert after one clock cycle else if (axi_rready) begin axi_rready <= 1'b0; end // retain the previous value end always @(posedge M_AXI_ACLK) begin if (M_AXI_ARESETN == 0) begin rd_data <= 'b0;endelse if(M_AXI_RVALID)beginrd_data <= M_AXI_RDATA;endelserd_data <= 'b0;end//Flag write errors assign read_resp_error = (axi_rready & M_AXI_RVALID & M_AXI_RRESP[1]); endmoduleTX查找表

读写操作需要读写寄存器地址和数据表。

module txinitcode_save#(parameter integer M_AXI_ADDR_WIDTH = 32,parameter integer M_AXI_DATA_WIDTH = 32)(input clk,input rst,input [15:0] wr_sa_addr,input [15:0] rd_sa_addr,input sa_enable,output reg [M_AXI_DATA_WIDTH-1 : 0] initwr_data,output reg [M_AXI_ADDR_WIDTH-1 : 0] initwr_addr,output reg [M_AXI_ADDR_WIDTH-1 : 0] initrd_addr,output reg initata_valid);always @(posedge clk) initata_valid <= sa_enable;always @(posedge clk)if(rst)initwr_data <= 32'h0000_0000;elseif(sa_enable)begincase(wr_sa_addr)// 16'd0: initwr_data <= 32'h0000_0000; //复位 16'd0: initwr_data <= 32'h0000_0002; // AXI4 stream data yes16'd1: initwr_data <= 32'h0000_0001; //扩展多块E = 116'd2: initwr_data <= 32'h0000_0001; //子类116'd3: initwr_data <= 32'h0000_0001; //Meta Mode N/A16'd4: initwr_data <= 32'h0000_0008; //通道数16'd5: initwr_data <= 32'h0000_0000; //GT loopback TEST_MODE16'd6: initwr_data <= 32'h0000_0000; //SYSREF always and ......16'd7: initwr_data <= 32'h0000_0000; //中断NO 16'd8: initwr_data <= 32'h0000_0000; //静止传输 空闲信号 TX断电 TX极性反转 NO lan016'd9: initwr_data <= 32'h0000_0000; //rx极性反转NO16'd10:initwr_data <= 32'h0000_0000; //lan016'd11:initwr_data <= 32'h0000_0000; //lan016'd12:initwr_data <= 32'h0000_0000; 16'd13:initwr_data <= 32'h0000_0000;16'd14:initwr_data <= 32'h0000_0000;16'd15:initwr_data <= 32'h0000_0000;16'd16:initwr_data <= 32'h0000_0000;16'd17:initwr_data <= 32'h0000_0000;16'd18:initwr_data <= 32'h0000_0000;16'd19:initwr_data <= 32'h0000_0000;16'd20:initwr_data <= 32'h0000_0000;16'd21:initwr_data <= 32'h0000_0000;16'd22:initwr_data <= 32'h0000_0000;16'd23:initwr_data <= 32'h0000_0000;16'd24:initwr_data <= 32'h0000_0000;16'd25:initwr_data <= 32'h0000_0000;16'd26:initwr_data <= 32'h0000_0000;16'd27:initwr_data <= 32'h0000_0000;16'd28:initwr_data <= 32'h0000_0000;16'd29:initwr_data <= 32'h0000_0000;16'd30:initwr_data <= 32'h0000_0000;16'd31:initwr_data <= 32'h0000_0000;16'd32:initwr_data <= 32'h0000_0000;16'd33:initwr_data <= 32'h0000_0000;16'd34:initwr_data <= 32'h0000_0000;16'd35:initwr_data <= 32'h0000_0000;16'd36:initwr_data <= 32'h0000_0000;16'd37:initwr_data <= 32'h0000_0000;16'd38:initwr_data <= 32'h0000_0000;16'd39:initwr_data <= 32'h0000_0000;16'd40:initwr_data <= 32'h0000_0001; //复位IP16'd41:initwr_data <= 32'h0000_0000; //复位IPdefault : initwr_data <= 'd0;endcaseendalways @(posedge clk)if(rst)initwr_addr <= 32'h0000_0000;elseif(sa_enable)begincase(wr_sa_addr)// 16'd0: initwr_addr <= 32'h0000_0020;16'd0: initwr_addr <= 32'h0000_0024;16'd1: initwr_addr <= 32'h0000_0030;16'd2: initwr_addr <= 32'h0000_0034;16'd3: initwr_addr <= 32'h0000_0038;16'd4: initwr_addr <= 32'h0000_0040;16'd5: initwr_addr <= 32'h0000_0048;16'd6: initwr_addr <= 32'h0000_0050;16'd7: initwr_addr <= 32'h0000_0064;16'd8: initwr_addr <= 32'h0000_0460; //lan016'd9: initwr_addr <= 32'h0000_0464; //lan016'd10:initwr_addr <= 32'h0000_0468; //lan016'd11:initwr_addr <= 32'h0000_046C; //lan016'd12:initwr_addr <= 32'h0000_04E0; //lan116'd13:initwr_addr <= 32'h0000_04E4; //lan116'd14:initwr_addr <= 32'h0000_04E8; //lan116'd15:initwr_addr <= 32'h0000_04FC; //lan116'd16:initwr_addr <= 32'h0000_0560; //lan216'd17:initwr_addr <= 32'h0000_0564; //lan216'd18:initwr_addr <= 32'h0000_0568; //lan216'd19:initwr_addr <= 32'h0000_056C; //lan216'd20:initwr_addr <= 32'h0000_05E0; //lan316'd21:initwr_addr <= 32'h0000_05E4; //lan316'd22:initwr_addr <= 32'h0000_05E8; //lan316'd23:initwr_addr <= 32'h0000_05EC; //lan316'd24:initwr_addr <= 32'h0000_0660; //lan416'd25:initwr_addr <= 32'h0000_0664; //lan416'd26:initwr_addr <= 32'h0000_0668; //lan416'd27:initwr_addr <= 32'h0000_066C; //lan416'd28:initwr_addr <= 32'h0000_06E0; //lan516'd29:initwr_addr <= 32'h0000_06E4; //lan516'd30:initwr_addr <= 32'h0000_06E8; //lan516'd31:initwr_addr <= 32'h0000_06EC; //lan516'd32:initwr_addr <= 32'h0000_0760; //lan616'd33:initwr_addr <= 32'h0000_0764; //lan616'd34:initwr_addr <= 32'h0000_0768; //lan616'd35:initwr_addr <= 32'h0000_076C; //lan616'd36:initwr_addr <= 32'h0000_07E0; //lan716'd37:initwr_addr <= 32'h0000_07E4; //lan716'd38:initwr_addr <= 32'h0000_07E8; //lan716'd39:initwr_addr <= 32'h0000_07EC; //lan716'd40:initwr_addr <= 32'h0000_0020; //复位IP16'd41:initwr_addr <= 32'h0000_0020; //复位IPdefault : initwr_addr <= 'd0;endcaseendalways @(posedge clk)if(rst)initrd_addr <= 32'h0000_0000;elseif(sa_enable)begincase(rd_sa_addr)// 16'd0: initwr_addr <= 32'h0000_0020;16'd0: initrd_addr <= 32'h0000_0000;16'd1: initrd_addr <= 32'h0000_0004;16'd2: initrd_addr <= 32'h0000_0020;16'd3: initrd_addr <= 32'h0000_0024;16'd4: initrd_addr <= 32'h0000_0030;16'd5: initrd_addr <= 32'h0000_0034;16'd6: initrd_addr <= 32'h0000_0038;16'd7: initrd_addr <= 32'h0000_0040;16'd8: initrd_addr <= 32'h0000_0048;16'd9: initrd_addr <= 32'h0000_0050;16'd10:initrd_addr <= 32'h0000_0060;16'd11:initrd_addr <= 32'h0000_0064;16'd12:initrd_addr <= 32'h0000_0068;16'd13:initrd_addr <= 32'h0000_0460; //lan016'd14:initrd_addr <= 32'h0000_0464; //lan016'd15:initrd_addr <= 32'h0000_0468; //lan016'd16:initrd_addr <= 32'h0000_046C; //lan016'd17:initrd_addr <= 32'h0000_04E0; //lan116'd18:initrd_addr <= 32'h0000_04E4; //lan116'd19:initrd_addr <= 32'h0000_04E8; //lan116'd20:initrd_addr <= 32'h0000_04FC; //lan116'd21:initrd_addr <= 32'h0000_0560; //lan216'd22:initrd_addr <= 32'h0000_0564; //lan216'd23:initrd_addr <= 32'h0000_0568; //lan216'd24:initrd_addr <= 32'h0000_056C; //lan216'd25:initrd_addr <= 32'h0000_05E0; //lan316'd26:initrd_addr <= 32'h0000_05E4; //lan316'd27:initrd_addr <= 32'h0000_05E8; //lan316'd28:initrd_addr <= 32'h0000_05EC; //lan316'd29:initrd_addr <= 32'h0000_0660; //lan416'd30:initrd_addr <= 32'h0000_0664; //lan416'd31:initrd_addr <= 32'h0000_0668; //lan416'd32:initrd_addr <= 32'h0000_066C; //lan416'd33:initrd_addr <= 32'h0000_06E0; //lan516'd34:initrd_addr <= 32'h0000_06E4; //lan516'd35:initrd_addr <= 32'h0000_06E8; //lan516'd36:initrd_addr <= 32'h0000_06EC; //lan516'd37:initrd_addr <= 32'h0000_0760; //lan616'd38:initrd_addr <= 32'h0000_0764; //lan616'd39:initrd_addr <= 32'h0000_0768; //lan616'd40:initrd_addr <= 32'h0000_076C; //lan616'd41:initrd_addr <= 32'h0000_07E0; //lan716'd42:initrd_addr <= 32'h0000_07E4; //lan716'd43:initrd_addr <= 32'h0000_07E8; //lan716'd44:initrd_addr <= 32'h0000_07EC; //lan716'd45:initrd_addr <= 32'h0000_0020; //复位IPdefault : initrd_addr <= 'd0;endcaseendendmoduleTX JESD204CIP核文件

`timescale 1ns / 1ps

module jesd204_tx_core(input tx_core_reset ,input tx_core_clk ,input tx_sysref ,input axi_clk ,input rst_n ,input [511 : 0] tx_tdata,input [255 : 0] tx_cmd_tdata,input tx_cmd_tvalid,input refclk ,input drpclk ,output tx_aresetn ,output tx_tready ,output tx_soemb ,output [7 : 0] txp_out ,output [7 : 0] txn_out ,input wire [11 : 0] s_axi_awaddr , input wire s_axi_awvalid ,output wire s_axi_awready ,input wire [31 : 0] s_axi_wdata ,input wire [3 : 0] s_axi_wstrb ,input wire s_axi_wvalid ,output wire s_axi_wready ,output wire [1 : 0] s_axi_bresp ,output wire s_axi_bvalid ,input wire s_axi_bready ,input wire [11 : 0] s_axi_araddr ,input wire s_axi_arvalid ,output wire s_axi_arready ,output wire [31 : 0] s_axi_rdata ,output wire [1 : 0] s_axi_rresp ,output wire s_axi_rvalid ,input wire s_axi_rready );wire [63 : 0] gt0_txdata ;

wire [3 : 0] gt0_txcharisk ;

wire [1 : 0] gt0_txheader ;

wire [63 : 0] gt1_txdata ;

wire [3 : 0] gt1_txcharisk ;

wire [1 : 0] gt1_txheader ;

wire [63 : 0] gt2_txdata ;

wire [3 : 0] gt2_txcharisk ;

wire [1 : 0] gt2_txheader ;

wire [63 : 0] gt3_txdata ;

wire [3 : 0] gt3_txcharisk ;

wire [1 : 0] gt3_txheader ;

wire [63 : 0] gt4_txdata ;

wire [3 : 0] gt4_txcharisk ;

wire [1 : 0] gt4_txheader ;

wire [63 : 0] gt5_txdata ;

wire [3 : 0] gt5_txcharisk ;

wire [1 : 0] gt5_txheader ;

wire [63 : 0] gt6_txdata ;

wire [3 : 0] gt6_txcharisk ;

wire [1 : 0] gt6_txheader ;

wire [63 : 0] gt7_txdata ;

wire [3 : 0] gt7_txcharisk ;

wire [1 : 0] gt7_txheader ;

wire tx_reset_gt ;

wire tx_reset_done ;

wire tx_cmd_tready ;

wire irq ;

wire gt_powergood ;jesd204c_0 jesd204c_0_inst ( .s_axi_aclk(axi_clk), // input wire s_axi_aclk.s_axi_aresetn(rst_n), // input wire s_axi_aresetn .s_axi_awaddr(s_axi_awaddr), // input wire [11 : 0] s_axi_awaddr.s_axi_awvalid(s_axi_awvalid), // input wire s_axi_awvalid.s_axi_awready(s_axi_awready), // output wire s_axi_awready.s_axi_wdata(s_axi_wdata), // input wire [31 : 0] s_axi_wdata.s_axi_wstrb(s_axi_wstrb), // input wire [3 : 0] s_axi_wstrb.s_axi_wvalid(s_axi_wvalid), // input wire s_axi_wvalid.s_axi_wready(s_axi_wready), // output wire s_axi_wready.s_axi_bresp(s_axi_bresp), // output wire [1 : 0] s_axi_bresp.s_axi_bvalid(s_axi_bvalid), // output wire s_axi_bvalid.s_axi_bready(s_axi_bready), // input wire s_axi_bready.s_axi_araddr(s_axi_araddr), // input wire [11 : 0] s_axi_araddr.s_axi_arvalid(s_axi_arvalid), // input wire s_axi_arvalid.s_axi_arready(s_axi_arready), // output wire s_axi_arready.s_axi_rdata(s_axi_rdata), // output wire [31 : 0] s_axi_rdata.s_axi_rresp(s_axi_rresp), // output wire [1 : 0] s_axi_rresp.s_axi_rvalid(s_axi_rvalid), // output wire s_axi_rvalid.s_axi_rready(s_axi_rready), // input wire s_axi_rready.tx_core_clk(tx_core_clk), // input wire tx_core_clk.tx_core_reset(tx_core_reset ||(~rst_n)), // input wire tx_core_reset.tx_sysref(tx_sysref), // input wire tx_sysref.irq(irq), // output wire irq.tx_tdata(tx_tdata), // input wire [511 : 0] tx_tdata.tx_tready(tx_tready), // output wire tx_tready.tx_aresetn(tx_aresetn), // output wire tx_aresetn.tx_soemb(tx_soemb), // output wire tx_soemb.tx_cmd_tdata(tx_cmd_tdata), // input wire [255 : 0] tx_cmd_tdata.tx_cmd_tvalid(tx_cmd_tvalid), // input wire tx_cmd_tvalid.tx_cmd_tready(tx_cmd_tready), // output wire tx_cmd_tready.tx_reset_gt(tx_reset_gt), // output wire tx_reset_gt.tx_reset_done(tx_reset_done), // input wire tx_reset_done.gt0_txdata(gt0_txdata), // output wire [63 : 0] gt0_txdata.gt0_txcharisk(gt0_txcharisk), // output wire [3 : 0] gt0_txcharisk.gt0_txheader(gt0_txheader), // output wire [1 : 0] gt0_txheader.gt1_txdata(gt1_txdata), // output wire [63 : 0] gt1_txdata.gt1_txcharisk(gt1_txcharisk), // output wire [3 : 0] gt1_txcharisk.gt1_txheader(gt1_txheader), // output wire [1 : 0] gt1_txheader.gt2_txdata(gt2_txdata), // output wire [63 : 0] gt2_txdata.gt2_txcharisk(gt2_txcharisk), // output wire [3 : 0] gt2_txcharisk.gt2_txheader(gt2_txheader), // output wire [1 : 0] gt2_txheader.gt3_txdata(gt3_txdata), // output wire [63 : 0] gt3_txdata.gt3_txcharisk(gt3_txcharisk), // output wire [3 : 0] gt3_txcharisk.gt3_txheader(gt3_txheader), // output wire [1 : 0] gt3_txheader.gt4_txdata(gt4_txdata), // output wire [63 : 0] gt4_txdata.gt4_txcharisk(gt4_txcharisk), // output wire [3 : 0] gt4_txcharisk.gt4_txheader(gt4_txheader), // output wire [1 : 0] gt4_txheader.gt5_txdata(gt5_txdata), // output wire [63 : 0] gt5_txdata.gt5_txcharisk(gt5_txcharisk), // output wire [3 : 0] gt5_txcharisk.gt5_txheader(gt5_txheader), // output wire [1 : 0] gt5_txheader.gt6_txdata(gt6_txdata), // output wire [63 : 0] gt6_txdata.gt6_txcharisk(gt6_txcharisk), // output wire [3 : 0] gt6_txcharisk.gt6_txheader(gt6_txheader), // output wire [1 : 0] gt6_txheader.gt7_txdata(gt7_txdata), // output wire [63 : 0] gt7_txdata.gt7_txcharisk(gt7_txcharisk), // output wire [3 : 0] gt7_txcharisk.gt7_txheader(gt7_txheader) // output wire [1 : 0] gt7_txheader

);jesd204_phy_0 jesd204_phy_0_inst (.qpll0_refclk(refclk), // input wire qpll0_refclk.drpclk(drpclk), // input wire drpclk.tx_reset_gt(tx_reset_gt), // input wire tx_reset_gt.rx_reset_gt(tx_reset_gt), // input wire rx_reset_gt.tx_sys_reset(~rst_n), // input wire tx_sys_reset.rx_sys_reset(~rst_n), // input wire rx_sys_reset.txp_out(txp_out), // output wire [7 : 0] txp_out.txn_out(txn_out), // output wire [7 : 0] txn_out.rxp_in(8'b0), // input wire [7 : 0] rxp_in.rxn_in(8'b0), // input wire [7 : 0] rxn_in.tx_core_clk(tx_core_clk), // input wire tx_core_clk.rx_core_clk(tx_core_clk), // input wire rx_core_clk.txoutclk(), // output wire txoutclk.rxoutclk(), // output wire rxoutclk.gt0_txdata(gt0_txdata), // input wire [63 : 0] gt0_txdata.gt0_txcharisk(gt0_txcharisk), // input wire [3 : 0] gt0_txcharisk.gt0_txheader(gt0_txheader), // input wire [1 : 0] gt0_txheader.gt1_txdata(gt1_txdata), // input wire [63 : 0] gt1_txdata.gt1_txcharisk(gt1_txcharisk), // input wire [3 : 0] gt1_txcharisk.gt1_txheader(gt1_txheader), // input wire [1 : 0] gt1_txheader.gt2_txdata(gt2_txdata), // input wire [63 : 0] gt2_txdata.gt2_txcharisk(gt2_txcharisk), // input wire [3 : 0] gt2_txcharisk.gt2_txheader(gt2_txheader), // input wire [1 : 0] gt2_txheader.gt3_txdata(gt3_txdata), // input wire [63 : 0] gt3_txdata.gt3_txcharisk(gt3_txcharisk), // input wire [3 : 0] gt3_txcharisk.gt3_txheader(gt3_txheader), // input wire [1 : 0] gt3_txheader.gt4_txdata(gt4_txdata), // input wire [63 : 0] gt4_txdata.gt4_txcharisk(gt4_txcharisk), // input wire [3 : 0] gt4_txcharisk.gt4_txheader(gt4_txheader), // input wire [1 : 0] gt4_txheader.gt5_txdata(gt5_txdata), // input wire [63 : 0] gt5_txdata.gt5_txcharisk(gt5_txcharisk), // input wire [3 : 0] gt5_txcharisk.gt5_txheader(gt5_txheader), // input wire [1 : 0] gt5_txheader.gt6_txdata(gt6_txdata), // input wire [63 : 0] gt6_txdata.gt6_txcharisk(gt6_txcharisk), // input wire [3 : 0] gt6_txcharisk.gt6_txheader(gt6_txheader), // input wire [1 : 0] gt6_txheader.gt7_txdata(gt7_txdata), // input wire [63 : 0] gt7_txdata.gt7_txcharisk(gt7_txcharisk), // input wire [3 : 0] gt7_txcharisk.gt7_txheader(gt7_txheader), // input wire [1 : 0] gt7_txheader.tx_reset_done(tx_reset_done), // output wire tx_reset_done.gt_powergood(gt_powergood), // output wire gt_powergood.gt0_rxdata(), // output wire [63 : 0] gt0_rxdata.gt0_rxcharisk(), // output wire [3 : 0] gt0_rxcharisk.gt0_rxdisperr(), // output wire [3 : 0] gt0_rxdisperr.gt0_rxnotintable(), // output wire [3 : 0] gt0_rxnotintable.gt0_rxheader(), // output wire [1 : 0] gt0_rxheader.gt0_rxmisalign(), // output wire gt0_rxmisalign.gt0_rxblock_sync(), // output wire gt0_rxblock_sync.gt1_rxdata(), // output wire [63 : 0] gt1_rxdata.gt1_rxcharisk(), // output wire [3 : 0] gt1_rxcharisk.gt1_rxdisperr(), // output wire [3 : 0] gt1_rxdisperr.gt1_rxnotintable(), // output wire [3 : 0] gt1_rxnotintable.gt1_rxheader(), // output wire [1 : 0] gt1_rxheader.gt1_rxmisalign(), // output wire gt1_rxmisalign.gt1_rxblock_sync(), // output wire gt1_rxblock_sync.gt2_rxdata(), // output wire [63 : 0] gt2_rxdata.gt2_rxcharisk(), // output wire [3 : 0] gt2_rxcharisk.gt2_rxdisperr(), // output wire [3 : 0] gt2_rxdisperr.gt2_rxnotintable(), // output wire [3 : 0] gt2_rxnotintable.gt2_rxheader(), // output wire [1 : 0] gt2_rxheader.gt2_rxmisalign(), // output wire gt2_rxmisalign.gt2_rxblock_sync(), // output wire gt2_rxblock_sync.gt3_rxdata(), // output wire [63 : 0] gt3_rxdata.gt3_rxcharisk(), // output wire [3 : 0] gt3_rxcharisk.gt3_rxdisperr(), // output wire [3 : 0] gt3_rxdisperr.gt3_rxnotintable(), // output wire [3 : 0] gt3_rxnotintable.gt3_rxheader(), // output wire [1 : 0] gt3_rxheader.gt3_rxmisalign(), // output wire gt3_rxmisalign.gt3_rxblock_sync(), // output wire gt3_rxblock_sync.gt4_rxdata(), // output wire [63 : 0] gt4_rxdata.gt4_rxcharisk(), // output wire [3 : 0] gt4_rxcharisk.gt4_rxdisperr(), // output wire [3 : 0] gt4_rxdisperr.gt4_rxnotintable(), // output wire [3 : 0] gt4_rxnotintable.gt4_rxheader(), // output wire [1 : 0] gt4_rxheader.gt4_rxmisalign(), // output wire gt4_rxmisalign.gt4_rxblock_sync(), // output wire gt4_rxblock_sync.gt5_rxdata(), // output wire [63 : 0] gt5_rxdata.gt5_rxcharisk(), // output wire [3 : 0] gt5_rxcharisk.gt5_rxdisperr(), // output wire [3 : 0] gt5_rxdisperr.gt5_rxnotintable(), // output wire [3 : 0] gt5_rxnotintable.gt5_rxheader(), // output wire [1 : 0] gt5_rxheader.gt5_rxmisalign(), // output wire gt5_rxmisalign.gt5_rxblock_sync(), // output wire gt5_rxblock_sync.gt6_rxdata(), // output wire [63 : 0] gt6_rxdata.gt6_rxcharisk(), // output wire [3 : 0] gt6_rxcharisk.gt6_rxdisperr(), // output wire [3 : 0] gt6_rxdisperr.gt6_rxnotintable(), // output wire [3 : 0] gt6_rxnotintable.gt6_rxheader(), // output wire [1 : 0] gt6_rxheader.gt6_rxmisalign(), // output wire gt6_rxmisalign.gt6_rxblock_sync(), // output wire gt6_rxblock_sync.gt7_rxdata(), // output wire [63 : 0] gt7_rxdata.gt7_rxcharisk(), // output wire [3 : 0] gt7_rxcharisk.gt7_rxdisperr(), // output wire [3 : 0] gt7_rxdisperr.gt7_rxnotintable(), // output wire [3 : 0] gt7_rxnotintable.gt7_rxheader(), // output wire [1 : 0] gt7_rxheader.gt7_rxmisalign(), // output wire gt7_rxmisalign.gt7_rxblock_sync(), // output wire gt7_rxblock_sync.rx_reset_done(), // output wire rx_reset_done.common0_qpll0_clk_out(), // output wire common0_qpll0_clk_out.common0_qpll0_refclk_out(), // output wire common0_qpll0_refclk_out.common0_qpll0_lock_out(), // output wire common0_qpll0_lock_out.common1_qpll0_clk_out(), // output wire common1_qpll0_clk_out.common1_qpll0_refclk_out(), // output wire common1_qpll0_refclk_out.common1_qpll0_lock_out() // output wire common1_qpll0_lock_out

);endmodule

TX初始化顶层文件

module rxjesd_init #(parameter integer C_M_AXI_ADDR_WIDTH = 32,parameter integer C_M_AXI_DATA_WIDTH = 32)(input clk,input rst,input rx_wr_op ,input rx_rd_op ,input [15:0] rx_wrsa_addr ,input [15:0] rx_rdsa_addr ,output rx_wr_done ,output [C_M_AXI_DATA_WIDTH-1 : 0] rx_rd_data ,output rx_idle_signal,output inter_error,///写地址通道output [C_M_AXI_ADDR_WIDTH-1 : 0] M_AXI_AWADDR,output [2 : 0] M_AXI_AWPROT,output M_AXI_AWVALID,input M_AXI_AWREADY,// 写数据通道output [C_M_AXI_DATA_WIDTH-1 : 0] M_AXI_WDATA,output [C_M_AXI_DATA_WIDTH/8-1 : 0] M_AXI_WSTRB, output M_AXI_WVALID,input M_AXI_WREADY,//写响应通道 表示写传输状态0input [1 : 0] M_AXI_BRESP,input M_AXI_BVALID,output M_AXI_BREADY,//读地址通道output [C_M_AXI_ADDR_WIDTH-1 : 0] M_AXI_ARADDR,output [2 : 0] M_AXI_ARPROT,output M_AXI_ARVALID,input M_AXI_ARREADY,// 读数据通道input [C_M_AXI_DATA_WIDTH-1 : 0] M_AXI_RDATA,input [1 : 0] M_AXI_RRESP,input M_AXI_RVALID,output M_AXI_RREADY );wire [C_M_AXI_DATA_WIDTH-1 : 0] wr_data;

wire [C_M_AXI_DATA_WIDTH-1 : 0] rd_data;

wire [C_M_AXI_ADDR_WIDTH-1 : 0] wr_addr;

wire [C_M_AXI_ADDR_WIDTH-1 : 0] rd_addr;

wire waddate_valid;

wire wr_ok;

wire rdaddr_valid;

wire rdata_valid;JESD204_RxInitcode#(.M_AXI_ADDR_WIDTH(C_M_AXI_ADDR_WIDTH),.M_AXI_DATA_WIDTH(C_M_AXI_DATA_WIDTH)

)

JESD204_RxInitcode_inst(.rst (rst),.clk (clk),.wr_op (rx_wr_op),.rx_wrsa_addr (rx_wrsa_addr),.rd_op (rx_rd_op),.rx_rdsa_addr (rx_rdsa_addr),.wr_done (rx_wr_done),.rx_rd_data (rx_rd_data),.wr_data (wr_data),.wr_addr (wr_addr),.waddate_valid (waddate_valid),.wr_ok (wr_ok),.rd_addr (rd_addr),.rdaddr_valid (rdaddr_valid),.rd_data (rd_data),.rdata_valid (rdata_valid),.idle_signal (rx_idle_signal)); JESD204_Interface_Axi #(.C_M_AXI_ADDR_WIDTH(C_M_AXI_ADDR_WIDTH),.C_M_AXI_DATA_WIDTH(C_M_AXI_DATA_WIDTH))JESD204_Interface_Axi_inst(.wr_addr (wr_addr),.wr_data (wr_data),.waddate_valid (waddate_valid),//wr ack one clock cycle.wr_ok (wr_ok),//rd address channel.rd_addr (rd_addr),.rdaddr_valid (rdaddr_valid),//rd data channel .rd_data (rd_data),.rdata_valid (rdata_valid), //one clock cycle.error_reg (inter_error),.M_AXI_ACLK (clk),.M_AXI_ARESETN (~rst),///写地址通道.M_AXI_AWADDR (M_AXI_AWADDR),.M_AXI_AWPROT (M_AXI_AWPROT),.M_AXI_AWVALID (M_AXI_AWVALID),.M_AXI_AWREADY (M_AXI_AWREADY),// 写数据通道 .M_AXI_WDATA (M_AXI_WDATA),.M_AXI_WSTRB (M_AXI_WSTRB), .M_AXI_WVALID (M_AXI_WVALID),.M_AXI_WREADY (M_AXI_WREADY),//写响应通道 表示写传输状态0.M_AXI_BRESP (M_AXI_BRESP),.M_AXI_BVALID (M_AXI_BVALID),.M_AXI_BREADY (M_AXI_BREADY),//读地址通道 .M_AXI_ARADDR (M_AXI_ARADDR),.M_AXI_ARPROT (M_AXI_ARPROT),.M_AXI_ARVALID (M_AXI_ARVALID),.M_AXI_ARREADY (M_AXI_ARREADY), // 读数据通道 .M_AXI_RDATA (M_AXI_RDATA),.M_AXI_RRESP (M_AXI_RRESP),.M_AXI_RVALID (M_AXI_RVALID),.M_AXI_RREADY (M_AXI_RREADY));

endmodule

RX查找表

RX初始化主状态机、初始化顶层文件、AXI接口转化与TX一致,这里不在赘述。

module rxinitcode_save#(parameter integer M_AXI_ADDR_WIDTH = 32,parameter integer M_AXI_DATA_WIDTH = 32)(input clk,input rst,input [15:0] wr_sa_addr,input [15:0] rd_sa_addr,input sa_enable,output reg [M_AXI_DATA_WIDTH-1 : 0] initwr_data,output reg [M_AXI_ADDR_WIDTH-1 : 0] initwr_addr,output reg [M_AXI_ADDR_WIDTH-1 : 0] initrd_addr,output reg initata_valid);always @(posedge clk) initata_valid <= sa_enable;always @(posedge clk)if(rst)initwr_data <= 32'h0000_0000;elseif(sa_enable)begincase(wr_sa_addr)// 16'd0: initwr_data <= 32'h0000_0000; //复位 16'd0 :initwr_data <= 32'h0000_0002; // AXI4 stream data yes16'd1 :initwr_data <= 32'h0000_0001; //扩展多块E = 116'd2 :initwr_data <= 32'h0000_0001; //子类116'd3 :initwr_data <= 32'h0000_0001; //Meta Mode N/A16'd4 :initwr_data <= 32'h0000_0008; //通道数16'd5 :initwr_data <= 32'h0000_0000; //no release receiver buffer 16'd6 :initwr_data <= 32'h0000_0000; //GT loopback TEST_MODE16'd7 :initwr_data <= 32'h0000_0000; //MB 需要多少正确/不正确的多块对齐标记才能实现/丢失多块。实际使用的值是1加上此寄存器中的数字。16'd8 :initwr_data <= 32'h0000_0000; //SYSREF always and ......16'd9 :initwr_data <= 32'h0000_0000; //中断NO 16'd10:initwr_data <= 32'h0000_0000; //静止传输 空闲信号 TX断电 TX极性反转 NO lan016'd11:initwr_data <= 32'h0000_0000; //rx极性反转NO16'd12:initwr_data <= 32'h0000_0000; //lan016'd13:initwr_data <= 32'h0000_0000; //lan016'd14:initwr_data <= 32'h0000_0000; 16'd15:initwr_data <= 32'h0000_0000;16'd16:initwr_data <= 32'h0000_0000;16'd17:initwr_data <= 32'h0000_0000;16'd18:initwr_data <= 32'h0000_0000;16'd19:initwr_data <= 32'h0000_0000;16'd20:initwr_data <= 32'h0000_0000;16'd21:initwr_data <= 32'h0000_0000;16'd22:initwr_data <= 32'h0000_0000;16'd23:initwr_data <= 32'h0000_0000;16'd24:initwr_data <= 32'h0000_0000;16'd25:initwr_data <= 32'h0000_0000;16'd26:initwr_data <= 32'h0000_0000;16'd27:initwr_data <= 32'h0000_0000;16'd28:initwr_data <= 32'h0000_0000;16'd29:initwr_data <= 32'h0000_0000;16'd30:initwr_data <= 32'h0000_0000;16'd31:initwr_data <= 32'h0000_0000;16'd32:initwr_data <= 32'h0000_0000;16'd33:initwr_data <= 32'h0000_0000;16'd34:initwr_data <= 32'h0000_0000;16'd35:initwr_data <= 32'h0000_0000;16'd36:initwr_data <= 32'h0000_0000;16'd37:initwr_data <= 32'h0000_0000;16'd38:initwr_data <= 32'h0000_0000;16'd39:initwr_data <= 32'h0000_0000;16'd40:initwr_data <= 32'h0000_0000;16'd41:initwr_data <= 32'h0000_0000;16'd42:initwr_data <= 32'h0000_0001; //复位IP16'd43:initwr_data <= 32'h0000_0000; //复位IPdefault : initwr_data <= 'd0;endcaseendalways @(posedge clk)if(rst)initwr_addr <= 32'h0000_0000;elseif(sa_enable)begincase(wr_sa_addr)// 16'd0: initwr_addr <= 32'h0000_0020;16'd0 :initwr_addr <= 32'h0000_0024;16'd1 :initwr_addr <= 32'h0000_0030;16'd2 :initwr_addr <= 32'h0000_0034;16'd3 :initwr_addr <= 32'h0000_0038;16'd4 :initwr_addr <= 32'h0000_0040;16'd5 :initwr_addr <= 32'h0000_0044;16'd6 :initwr_addr <= 32'h0000_0048;16'd7 :initwr_addr <= 32'h0000_004C;16'd8 :initwr_addr <= 32'h0000_0050;16'd9 :initwr_addr <= 32'h0000_0064;16'd10:initwr_addr <= 32'h0000_0460; //lan016'd11:initwr_addr <= 32'h0000_0464; //lan016'd12:initwr_addr <= 32'h0000_0468; //lan016'd13:initwr_addr <= 32'h0000_046C; //lan016'd14:initwr_addr <= 32'h0000_04E0; //lan116'd15:initwr_addr <= 32'h0000_04E4; //lan116'd16:initwr_addr <= 32'h0000_04E8; //lan116'd17:initwr_addr <= 32'h0000_04FC; //lan116'd18:initwr_addr <= 32'h0000_0560; //lan216'd19:initwr_addr <= 32'h0000_0564; //lan216'd20:initwr_addr <= 32'h0000_0568; //lan216'd21:initwr_addr <= 32'h0000_056C; //lan216'd22:initwr_addr <= 32'h0000_05E0; //lan316'd23:initwr_addr <= 32'h0000_05E4; //lan316'd24:initwr_addr <= 32'h0000_05E8; //lan316'd25:initwr_addr <= 32'h0000_05EC; //lan316'd26:initwr_addr <= 32'h0000_0660; //lan416'd27:initwr_addr <= 32'h0000_0664; //lan416'd28:initwr_addr <= 32'h0000_0668; //lan416'd29:initwr_addr <= 32'h0000_066C; //lan416'd30:initwr_addr <= 32'h0000_06E0; //lan516'd31:initwr_addr <= 32'h0000_06E4; //lan516'd32:initwr_addr <= 32'h0000_06E8; //lan516'd33:initwr_addr <= 32'h0000_06EC; //lan516'd34:initwr_addr <= 32'h0000_0760; //lan616'd35:initwr_addr <= 32'h0000_0764; //lan616'd36:initwr_addr <= 32'h0000_0768; //lan616'd37:initwr_addr <= 32'h0000_076C; //lan616'd38:initwr_addr <= 32'h0000_07E0; //lan716'd39:initwr_addr <= 32'h0000_07E4; //lan716'd40:initwr_addr <= 32'h0000_07E8; //lan716'd41:initwr_addr <= 32'h0000_07EC; //lan716'd42:initwr_addr <= 32'h0000_0020; //复位IP16'd43:initwr_addr <= 32'h0000_0020; //复位IPdefault : initwr_addr <= 'd0;endcaseendalways @(posedge clk)if(rst)initrd_addr <= 32'h0000_0000;elseif(sa_enable)begincase(rd_sa_addr)// 16'd0: initwr_addr <= 32'h0000_0020;16'd0 :initrd_addr <= 32'h0000_0000;16'd1 :initrd_addr <= 32'h0000_0004;16'd2 :initrd_addr <= 32'h0000_0020;16'd3 :initrd_addr <= 32'h0000_0024;16'd4 :initrd_addr <= 32'h0000_0030;16'd5 :initrd_addr <= 32'h0000_0034;16'd6 :initrd_addr <= 32'h0000_0038;16'd7 :initrd_addr <= 32'h0000_0040;16'd8 :initrd_addr <= 32'h0000_0044;16'd9 :initrd_addr <= 32'h0000_0048;16'd10:initrd_addr <= 32'h0000_004C;16'd11:initrd_addr <= 32'h0000_0050;16'd12:initrd_addr <= 32'h0000_0054;16'd13:initrd_addr <= 32'h0000_0060;16'd14:initrd_addr <= 32'h0000_0064;16'd15:initrd_addr <= 32'h0000_0068;16'd16:initrd_addr <= 32'h0000_0400; //lan016'd17:initrd_addr <= 32'h0000_0410; //lan016'd18:initrd_addr <= 32'h0000_0414; //lan016'd19:initrd_addr <= 32'h0000_0460; //lan016'd20:initrd_addr <= 32'h0000_0464; //lan016'd21:initrd_addr <= 32'h0000_0468; //lan016'd22:initrd_addr <= 32'h0000_046C; //lan016'd23:initrd_addr <= 32'h0000_0480; //lan116'd24:initrd_addr <= 32'h0000_0490; //lan116'd25:initrd_addr <= 32'h0000_0494; //lan116'd26:initrd_addr <= 32'h0000_04E0; //lan116'd27:initrd_addr <= 32'h0000_04E4; //lan116'd28:initrd_addr <= 32'h0000_04E8; //lan116'd29:initrd_addr <= 32'h0000_04FC; //lan1 16'd30:initrd_addr <= 32'h0000_0500; //lan216'd31:initrd_addr <= 32'h0000_0510; //lan216'd32:initrd_addr <= 32'h0000_0514; //lan216'd33:initrd_addr <= 32'h0000_0560; //lan216'd34:initrd_addr <= 32'h0000_0564; //lan216'd35:initrd_addr <= 32'h0000_0568; //lan216'd36:initrd_addr <= 32'h0000_056C; //lan216'd37:initrd_addr <= 32'h0000_0580; //lan316'd38:initrd_addr <= 32'h0000_0590; //lan316'd39:initrd_addr <= 32'h0000_0594; //lan316'd40:initrd_addr <= 32'h0000_05E0; //lan316'd41:initrd_addr <= 32'h0000_05E4; //lan316'd42:initrd_addr <= 32'h0000_05E8; //lan316'd43:initrd_addr <= 32'h0000_05EC; //lan316'd44:initrd_addr <= 32'h0000_0600; //lan416'd45:initrd_addr <= 32'h0000_0610; //lan416'd46:initrd_addr <= 32'h0000_0614; //lan416'd47:initrd_addr <= 32'h0000_0660; //lan416'd48:initrd_addr <= 32'h0000_0664; //lan416'd49:initrd_addr <= 32'h0000_0668; //lan416'd50:initrd_addr <= 32'h0000_066C; //lan416'd51:initrd_addr <= 32'h0000_0680; //lan516'd52:initrd_addr <= 32'h0000_0690; //lan516'd53:initrd_addr <= 32'h0000_0694; //lan516'd54:initrd_addr <= 32'h0000_06E0; //lan516'd55:initrd_addr <= 32'h0000_06E4; //lan516'd56:initrd_addr <= 32'h0000_06E8; //lan516'd57:initrd_addr <= 32'h0000_06EC; //lan516'd58:initrd_addr <= 32'h0000_0700; //lan616'd59:initrd_addr <= 32'h0000_0710; //lan616'd60:initrd_addr <= 32'h0000_0714; //lan616'd61:initrd_addr <= 32'h0000_0760; //lan616'd62:initrd_addr <= 32'h0000_0764; //lan616'd63:initrd_addr <= 32'h0000_0768; //lan616'd64:initrd_addr <= 32'h0000_076C; //lan616'd65:initrd_addr <= 32'h0000_0780; //lan716'd66:initrd_addr <= 32'h0000_0790; //lan716'd67:initrd_addr <= 32'h0000_0794; //lan716'd68:initrd_addr <= 32'h0000_07E0; //lan716'd69:initrd_addr <= 32'h0000_07E4; //lan716'd70:initrd_addr <= 32'h0000_07E8; //lan716'd71:initrd_addr <= 32'h0000_07EC; //lan716'd72:initrd_addr <= 32'h0000_0020; //复位IPdefault : initrd_addr <= 'd0;endcaseend

endmodule

RX JESD204CIP文件

`timescale 1ns / 1ps

module jesd204c_rx_core(

input rx_sysref ,

input rx_core_clk ,

input axi_clk ,

input rst_n ,input refclk ,

input drpclk ,output [511 : 0] rx_tdata ,

output rx_tvalid ,

output rx_aresetn ,

output rx_soemb ,

output rx_crc_err ,

output rx_emb_err ,

output [255 : 0] rx_cmd_tdata ,

output rx_cmd_tvalid ,

output [7 : 0] rx_cmd_tuser ,

input rx_cmd_tready ,input [7 : 0] rxp_in ,

input [7 : 0] rxn_in ,input wire [11 : 0] s_axi_awaddr ,

input wire s_axi_awvalid ,

output wire s_axi_awready ,

input wire [31 : 0] s_axi_wdata ,

input wire [3 : 0] s_axi_wstrb ,

input wire s_axi_wvalid ,

output wire s_axi_wready ,

output wire [1 : 0] s_axi_bresp ,

output wire s_axi_bvalid ,

input wire s_axi_bready ,

input wire [11 : 0] s_axi_araddr ,

input wire s_axi_arvalid ,

output wire s_axi_arready ,

output wire [31 : 0] s_axi_rdata ,

output wire [1 : 0] s_axi_rresp ,

output wire s_axi_rvalid ,

input wire s_axi_rready );wire rx_reset_done ;

wire gt_powergood ;

wire rx_reset_gt ;

wire [63 : 0] gt0_rxdata ;

wire [3 : 0] gt0_rxcharisk ;

wire [3 : 0] gt0_rxdisperr ;

wire [3 : 0] gt0_rxnotintable ;

wire [1 : 0] gt0_rxheader ;

wire gt0_rxmisalign ;

wire gt0_rxblock_sync ;

wire [63 : 0] gt1_rxdata ;

wire [3 : 0] gt1_rxcharisk ;

wire [3 : 0] gt1_rxdisperr ;

wire [3 : 0] gt1_rxnotintable ;

wire [1 : 0] gt1_rxheader ;

wire gt1_rxmisalign ;

wire gt1_rxblock_sync ;

wire [63 : 0] gt2_rxdata ;

wire [3 : 0] gt2_rxcharisk ;

wire [3 : 0] gt2_rxdisperr ;

wire [3 : 0] gt2_rxnotintable ;

wire [1 : 0] gt2_rxheader ;

wire gt2_rxmisalign ;

wire gt2_rxblock_sync ;

wire [63 : 0] gt3_rxdata ;

wire [3 : 0] gt3_rxcharisk ;

wire [3 : 0] gt3_rxdisperr ;

wire [3 : 0] gt3_rxnotintable ;

wire [1 : 0] gt3_rxheader ;

wire gt3_rxmisalign ;

wire gt3_rxblock_sync ;

wire [63 : 0] gt4_rxdata ;

wire [3 : 0] gt4_rxcharisk ;

wire [3 : 0] gt4_rxdisperr ;

wire [3 : 0] gt4_rxnotintable ;

wire [1 : 0] gt4_rxheader ;

wire gt4_rxmisalign ;

wire gt4_rxblock_sync ;

wire [63 : 0] gt5_rxdata ;

wire [3 : 0] gt5_rxcharisk ;

wire [3 : 0] gt5_rxdisperr ;

wire [3 : 0] gt5_rxnotintable ;

wire [1 : 0] gt5_rxheader ;

wire gt5_rxmisalign ;

wire gt5_rxblock_sync ;

wire [63 : 0] gt6_rxdata ;

wire [3 : 0] gt6_rxcharisk ;

wire [3 : 0] gt6_rxdisperr ;

wire [3 : 0] gt6_rxnotintable ;

wire [1 : 0] gt6_rxheader ;

wire gt6_rxmisalign ;

wire gt6_rxblock_sync ;

wire [63 : 0] gt7_rxdata ;

wire [3 : 0] gt7_rxcharisk ;

wire [3 : 0] gt7_rxdisperr ;

wire [3 : 0] gt7_rxnotintable ;

wire [1 : 0] gt7_rxheader ;

wire gt7_rxmisalign ;

wire gt7_rxblock_sync ;jesd204c_1 jesd204c_1_inst (.s_axi_aclk(axi_clk), // input wire s_axi_aclk.s_axi_aresetn(rst_n), // input wire s_axi_aresetn.s_axi_awaddr(s_axi_awaddr), // input wire [11 : 0] s_axi_awaddr.s_axi_awvalid(s_axi_awvalid), // input wire s_axi_awvalid/.s_axi_awready(s_axi_awready), // output wire s_axi_awready.s_axi_wdata(s_axi_wdata), // input wire [31 : 0] s_axi_wdata.s_axi_wstrb(s_axi_wstrb), // input wire [3 : 0] s_axi_wstrb.s_axi_wvalid(s_axi_wvalid), // input wire s_axi_wvalid.s_axi_wready(s_axi_wready), // output wire s_axi_wready.s_axi_bresp(s_axi_bresp), // output wire [1 : 0] s_axi_bresp.s_axi_bvalid(s_axi_bvalid), // output wire s_axi_bvalid.s_axi_bready(s_axi_bready), // input wire s_axi_bready.s_axi_araddr(s_axi_araddr), // input wire [11 : 0] s_axi_araddr.s_axi_arvalid(s_axi_arvalid), // input wire s_axi_arvalid.s_axi_arready(s_axi_arready), // output wire s_axi_arready.s_axi_rdata(s_axi_rdata), // output wire [31 : 0] s_axi_rdata.s_axi_rresp(s_axi_rresp), // output wire [1 : 0] s_axi_rresp.s_axi_rvalid(s_axi_rvalid), // output wire s_axi_rvalid.s_axi_rready(s_axi_rready), // input wire s_axi_rready.rx_core_clk(rx_core_clk), // input wire rx_core_clk.rx_core_reset(!rst_n), // input wire rx_core_reset.rx_sysref(rx_sysref), // input wire rx_sysref.irq(), // output wire irq.rx_tdata(rx_tdata), // output wire [511 : 0] rx_tdata.rx_tvalid(rx_tvalid), // output wire rx_tvalid.rx_aresetn(rx_aresetn), // output wire rx_aresetn.rx_soemb(rx_soemb), // output wire rx_soemb.rx_crc_err(rx_crc_err), // output wire rx_crc_err.rx_emb_err(rx_emb_err), // output wire rx_emb_err.rx_cmd_tdata(rx_cmd_tdata), // output wire [255 : 0] rx_cmd_tdata.rx_cmd_tvalid(rx_cmd_tvalid), // output wire rx_cmd_tvalid.rx_cmd_tuser(rx_cmd_tuser), // output wire [7 : 0] rx_cmd_tuser.rx_cmd_tready(rx_cmd_tready), // input wire rx_cmd_tready.rx_reset_gt(rx_reset_gt), // output wire rx_reset_gt.rx_reset_done(rx_reset_done), // input wire rx_reset_done.gt0_rxdata(gt0_rxdata), // input wire [63 : 0] gt0_rxdata.gt0_rxcharisk(gt0_rxcharisk), // input wire [3 : 0] gt0_rxcharisk.gt0_rxdisperr(gt0_rxdisperr), // input wire [3 : 0] gt0_rxdisperr.gt0_rxnotintable(gt0_rxnotintable), // input wire [3 : 0] gt0_rxnotintable.gt0_rxheader(gt0_rxheader), // input wire [1 : 0] gt0_rxheader.gt0_rxmisalign(gt0_rxmisalign), // input wire gt0_rxmisalign.gt0_rxblock_sync(gt0_rxblock_sync), // input wire gt0_rxblock_sync.gt1_rxdata(gt1_rxdata), // input wire [63 : 0] gt1_rxdata.gt1_rxcharisk(gt1_rxcharisk), // input wire [3 : 0] gt1_rxcharisk.gt1_rxdisperr(gt1_rxdisperr), // input wire [3 : 0] gt1_rxdisperr.gt1_rxnotintable(gt1_rxnotintable), // input wire [3 : 0] gt1_rxnotintable.gt1_rxheader(gt1_rxheader), // input wire [1 : 0] gt1_rxheader.gt1_rxmisalign(gt1_rxmisalign), // input wire gt1_rxmisalign.gt1_rxblock_sync(gt1_rxblock_sync), // input wire gt1_rxblock_sync.gt2_rxdata(gt2_rxdata), // input wire [63 : 0] gt2_rxdata.gt2_rxcharisk(gt2_rxcharisk), // input wire [3 : 0] gt2_rxcharisk.gt2_rxdisperr(gt2_rxdisperr), // input wire [3 : 0] gt2_rxdisperr.gt2_rxnotintable(gt2_rxnotintable), // input wire [3 : 0] gt2_rxnotintable.gt2_rxheader(gt2_rxheader), // input wire [1 : 0] gt2_rxheader.gt2_rxmisalign(gt2_rxmisalign), // input wire gt2_rxmisalign.gt2_rxblock_sync(gt2_rxblock_sync), // input wire gt2_rxblock_sync.gt3_rxdata(gt3_rxdata), // input wire [63 : 0] gt3_rxdata.gt3_rxcharisk(gt3_rxcharisk), // input wire [3 : 0] gt3_rxcharisk.gt3_rxdisperr(gt3_rxdisperr), // input wire [3 : 0] gt3_rxdisperr.gt3_rxnotintable(gt3_rxnotintable), // input wire [3 : 0] gt3_rxnotintable.gt3_rxheader(gt3_rxheader), // input wire [1 : 0] gt3_rxheader.gt3_rxmisalign(gt3_rxmisalign), // input wire gt3_rxmisalign.gt3_rxblock_sync(gt3_rxblock_sync), // input wire gt3_rxblock_sync.gt4_rxdata(gt4_rxdata), // input wire [63 : 0] gt4_rxdata.gt4_rxcharisk(gt4_rxcharisk), // input wire [3 : 0] gt4_rxcharisk.gt4_rxdisperr(gt4_rxdisperr), // input wire [3 : 0] gt4_rxdisperr.gt4_rxnotintable(gt4_rxnotintable), // input wire [3 : 0] gt4_rxnotintable.gt4_rxheader(gt4_rxheader), // input wire [1 : 0] gt4_rxheader.gt4_rxmisalign(gt4_rxmisalign), // input wire gt4_rxmisalign.gt4_rxblock_sync(gt4_rxblock_sync), // input wire gt4_rxblock_sync.gt5_rxdata(gt5_rxdata), // input wire [63 : 0] gt5_rxdata.gt5_rxcharisk(gt5_rxcharisk), // input wire [3 : 0] gt5_rxcharisk.gt5_rxdisperr(gt5_rxdisperr), // input wire [3 : 0] gt5_rxdisperr.gt5_rxnotintable(gt5_rxnotintable), // input wire [3 : 0] gt5_rxnotintable.gt5_rxheader(gt5_rxheader), // input wire [1 : 0] gt5_rxheader.gt5_rxmisalign(gt5_rxmisalign), // input wire gt5_rxmisalign.gt5_rxblock_sync(gt5_rxblock_sync), // input wire gt5_rxblock_sync.gt6_rxdata(gt6_rxdata), // input wire [63 : 0] gt6_rxdata.gt6_rxcharisk(gt6_rxcharisk), // input wire [3 : 0] gt6_rxcharisk.gt6_rxdisperr(gt6_rxdisperr), // input wire [3 : 0] gt6_rxdisperr.gt6_rxnotintable(gt6_rxnotintable), // input wire [3 : 0] gt6_rxnotintable.gt6_rxheader(gt6_rxheader), // input wire [1 : 0] gt6_rxheader.gt6_rxmisalign(gt6_rxmisalign), // input wire gt6_rxmisalign.gt6_rxblock_sync(gt6_rxblock_sync), // input wire gt6_rxblock_sync.gt7_rxdata(gt7_rxdata), // input wire [63 : 0] gt7_rxdata.gt7_rxcharisk(gt7_rxcharisk), // input wire [3 : 0] gt7_rxcharisk.gt7_rxdisperr(gt7_rxdisperr), // input wire [3 : 0] gt7_rxdisperr.gt7_rxnotintable(gt7_rxnotintable), // input wire [3 : 0] gt7_rxnotintable.gt7_rxheader(gt7_rxheader), // input wire [1 : 0] gt7_rxheader.gt7_rxmisalign(gt7_rxmisalign), // input wire gt7_rxmisalign.gt7_rxblock_sync(gt7_rxblock_sync) // input wire gt7_rxblock_sync

); jesd204_phy_0 jesd204_phy_0_inst (.qpll0_refclk(refclk), // input wire qpll0_refclk.drpclk(drpclk), // input wire drpclk.tx_reset_gt(rx_reset_gt), // input wire tx_reset_gt.rx_reset_gt(rx_reset_gt), // input wire rx_reset_gt.tx_sys_reset(!rst_n), // input wire tx_sys_reset.rx_sys_reset(!rst_n), // input wire rx_sys_reset.txp_out(), // output wire [7 : 0] txp_out.txn_out(), // output wire [7 : 0] txn_out.rxp_in(rxp_in), // input wire [7 : 0] rxp_in.rxn_in(rxn_in), // input wire [7 : 0] rxn_in.tx_core_clk(rx_core_clk), // input wire tx_core_clk.rx_core_clk(rx_core_clk), // input wire rx_core_clk.txoutclk(), // output wire txoutclk.rxoutclk(), // output wire rxoutclk.gt0_txdata(), // input wire [63 : 0] gt0_txdata.gt0_txcharisk(), // input wire [3 : 0] gt0_txcharisk.gt0_txheader(), // input wire [1 : 0] gt0_txheader.gt1_txdata(), // input wire [63 : 0] gt1_txdata.gt1_txcharisk(), // input wire [3 : 0] gt1_txcharisk.gt1_txheader(), // input wire [1 : 0] gt1_txheader.gt2_txdata(), // input wire [63 : 0] gt2_txdata.gt2_txcharisk(), // input wire [3 : 0] gt2_txcharisk.gt2_txheader(), // input wire [1 : 0] gt2_txheader.gt3_txdata(), // input wire [63 : 0] gt3_txdata.gt3_txcharisk(), // input wire [3 : 0] gt3_txcharisk.gt3_txheader(), // input wire [1 : 0] gt3_txheader.gt4_txdata(), // input wire [63 : 0] gt4_txdata.gt4_txcharisk(), // input wire [3 : 0] gt4_txcharisk.gt4_txheader(), // input wire [1 : 0] gt4_txheader.gt5_txdata(), // input wire [63 : 0] gt5_txdata.gt5_txcharisk(), // input wire [3 : 0] gt5_txcharisk.gt5_txheader(), // input wire [1 : 0] gt5_txheader.gt6_txdata(), // input wire [63 : 0] gt6_txdata.gt6_txcharisk(), // input wire [3 : 0] gt6_txcharisk.gt6_txheader(), // input wire [1 : 0] gt6_txheader.gt7_txdata(), // input wire [63 : 0] gt7_txdata.gt7_txcharisk(), // input wire [3 : 0] gt7_txcharisk.gt7_txheader(), // input wire [1 : 0] gt7_txheader.tx_reset_done(), // output wire tx_reset_done.gt_powergood(gt_powergood), // output wire gt_powergood.gt0_rxdata(gt0_rxdata), // output wire [63 : 0] gt0_rxdata.gt0_rxcharisk(gt0_rxcharisk), // output wire [3 : 0] gt0_rxcharisk.gt0_rxdisperr(gt0_rxdisperr), // output wire [3 : 0] gt0_rxdisperr.gt0_rxnotintable(gt0_rxnotintable), // output wire [3 : 0] gt0_rxnotintable.gt0_rxheader(gt0_rxheader), // output wire [1 : 0] gt0_rxheader.gt0_rxmisalign(gt0_rxmisalign), // output wire gt0_rxmisalign.gt0_rxblock_sync(gt0_rxblock_sync), // output wire gt0_rxblock_sync.gt1_rxdata(gt1_rxdata), // output wire [63 : 0] gt1_rxdata.gt1_rxcharisk(gt1_rxcharisk), // output wire [3 : 0] gt1_rxcharisk.gt1_rxdisperr(gt1_rxdisperr), // output wire [3 : 0] gt1_rxdisperr.gt1_rxnotintable(gt1_rxnotintable), // output wire [3 : 0] gt1_rxnotintable.gt1_rxheader(gt1_rxheader), // output wire [1 : 0] gt1_rxheader.gt1_rxmisalign(gt1_rxmisalign), // output wire gt1_rxmisalign.gt1_rxblock_sync(gt1_rxblock_sync), // output wire gt1_rxblock_sync.gt2_rxdata(gt2_rxdata), // output wire [63 : 0] gt2_rxdata.gt2_rxcharisk(gt2_rxcharisk), // output wire [3 : 0] gt2_rxcharisk.gt2_rxdisperr(gt2_rxdisperr), // output wire [3 : 0] gt2_rxdisperr.gt2_rxnotintable(gt2_rxnotintable), // output wire [3 : 0] gt2_rxnotintable.gt2_rxheader(gt2_rxheader), // output wire [1 : 0] gt2_rxheader.gt2_rxmisalign(gt2_rxmisalign), // output wire gt2_rxmisalign.gt2_rxblock_sync(gt2_rxblock_sync), // output wire gt2_rxblock_sync.gt3_rxdata(gt3_rxdata), // output wire [63 : 0] gt3_rxdata.gt3_rxcharisk(gt3_rxcharisk), // output wire [3 : 0] gt3_rxcharisk.gt3_rxdisperr(gt3_rxdisperr), // output wire [3 : 0] gt3_rxdisperr.gt3_rxnotintable(gt3_rxnotintable), // output wire [3 : 0] gt3_rxnotintable.gt3_rxheader(gt3_rxheader), // output wire [1 : 0] gt3_rxheader.gt3_rxmisalign(gt3_rxmisalign), // output wire gt3_rxmisalign.gt3_rxblock_sync(gt3_rxblock_sync), // output wire gt3_rxblock_sync.gt4_rxdata(gt4_rxdata), // output wire [63 : 0] gt4_rxdata.gt4_rxcharisk(gt4_rxcharisk), // output wire [3 : 0] gt4_rxcharisk.gt4_rxdisperr(gt4_rxdisperr), // output wire [3 : 0] gt4_rxdisperr.gt4_rxnotintable(gt4_rxnotintable), // output wire [3 : 0] gt4_rxnotintable.gt4_rxheader(gt4_rxheader), // output wire [1 : 0] gt4_rxheader.gt4_rxmisalign(gt4_rxmisalign), // output wire gt4_rxmisalign.gt4_rxblock_sync(gt4_rxblock_sync), // output wire gt4_rxblock_sync.gt5_rxdata(gt5_rxdata), // output wire [63 : 0] gt5_rxdata.gt5_rxcharisk(gt5_rxcharisk), // output wire [3 : 0] gt5_rxcharisk.gt5_rxdisperr(gt5_rxdisperr), // output wire [3 : 0] gt5_rxdisperr.gt5_rxnotintable(gt5_rxnotintable), // output wire [3 : 0] gt5_rxnotintable.gt5_rxheader(gt5_rxheader), // output wire [1 : 0] gt5_rxheader.gt5_rxmisalign(gt5_rxmisalign), // output wire gt5_rxmisalign.gt5_rxblock_sync(gt5_rxblock_sync), // output wire gt5_rxblock_sync.gt6_rxdata(gt6_rxdata), // output wire [63 : 0] gt6_rxdata.gt6_rxcharisk(gt6_rxcharisk), // output wire [3 : 0] gt6_rxcharisk.gt6_rxdisperr(gt6_rxdisperr), // output wire [3 : 0] gt6_rxdisperr.gt6_rxnotintable(gt6_rxnotintable), // output wire [3 : 0] gt6_rxnotintable.gt6_rxheader(gt6_rxheader), // output wire [1 : 0] gt6_rxheader.gt6_rxmisalign(gt6_rxmisalign), // output wire gt6_rxmisalign.gt6_rxblock_sync(gt6_rxblock_sync), // output wire gt6_rxblock_sync.gt7_rxdata(gt7_rxdata), // output wire [63 : 0] gt7_rxdata.gt7_rxcharisk(gt7_rxcharisk), // output wire [3 : 0] gt7_rxcharisk.gt7_rxdisperr(gt7_rxdisperr), // output wire [3 : 0] gt7_rxdisperr.gt7_rxnotintable(gt7_rxnotintable), // output wire [3 : 0] gt7_rxnotintable.gt7_rxheader(gt7_rxheader), // output wire [1 : 0] gt7_rxheader.gt7_rxmisalign(gt7_rxmisalign), // output wire gt7_rxmisalign.gt7_rxblock_sync(gt7_rxblock_sync), // output wire gt7_rxblock_sync.rx_reset_done(rx_reset_done), // output wire rx_reset_done.common0_qpll0_clk_out(), // output wire common0_qpll0_clk_out.common0_qpll0_refclk_out(), // output wire common0_qpll0_refclk_out.common0_qpll0_lock_out(), // output wire common0_qpll0_lock_out.common1_qpll0_clk_out(), // output wire common1_qpll0_clk_out.common1_qpll0_refclk_out(), // output wire common1_qpll0_refclk_out.common1_qpll0_lock_out() // output wire common1_qpll0_lock_out

);

endmodule

仿真结果

TX输出的数据依次是1000;2000;3000

RX接收并解析的数据依次是1000;2000;3000

RX接收并解析的数据依次是1000;2000;3000

TX与RX数据一致。

![将元组类型的日期时间转换为字符串格式time.asctime([t])](https://i-blog.csdnimg.cn/direct/a68650309e3f433bbf07d78318ed83c2.png)