DC 板 boot 测 nor 兼容性记录(qspi )

软件问题:

1、DC板在跑 qspi时,在跑ddr 初始化部分需要修改以下参数,否则会在fsbl stage1 或者 stage 3 出错。

Board配置选 ad101_v10;

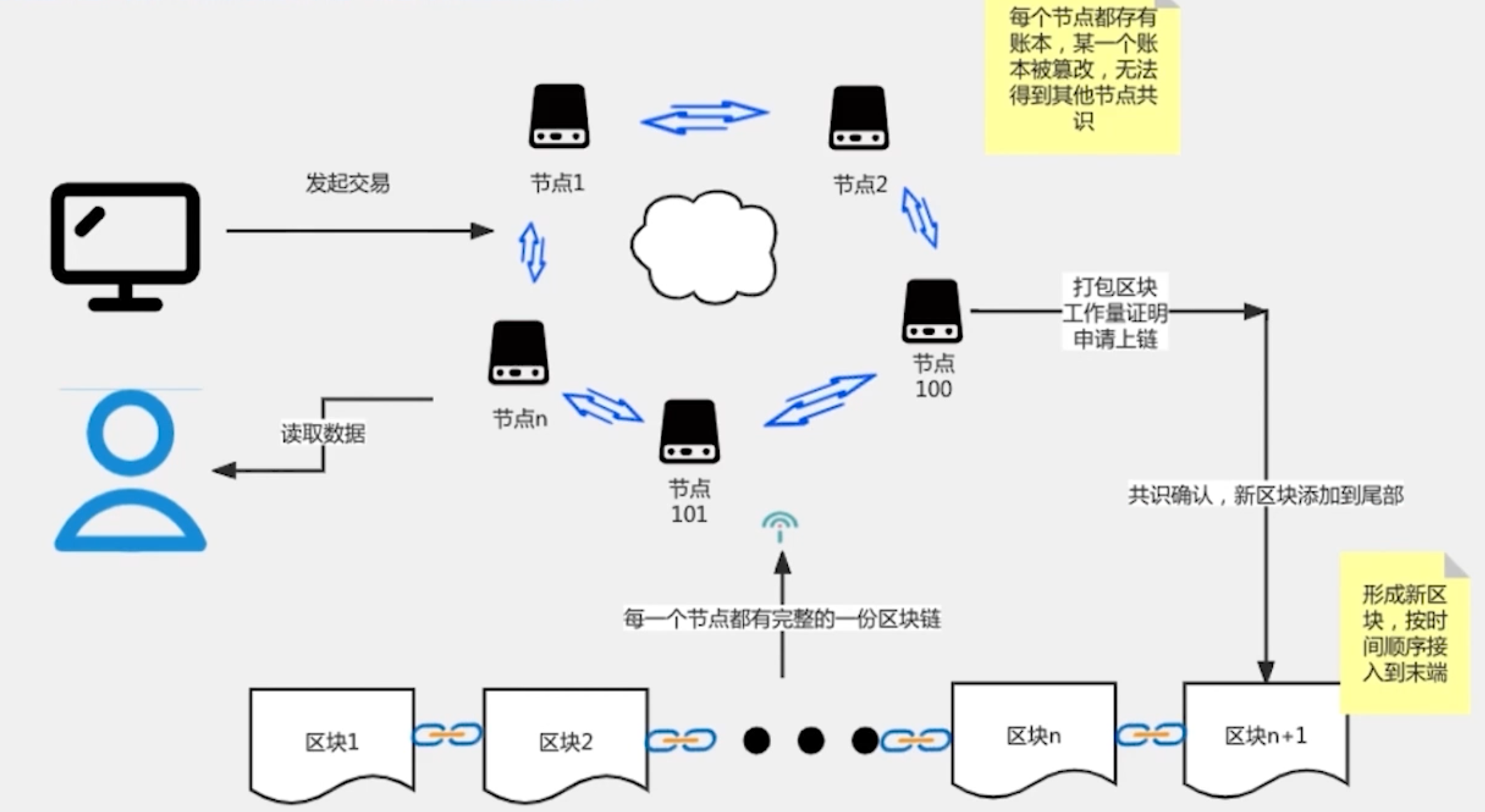

2、由于socket与DC板接触可能不是很好,所以怀疑在数据传输过程中如果 IO频率过高会导致数据读出来的和flash中原本存储的数据对不上,这个一般会怀疑是驱动问题,但其实只是频率问题,所以遇到flash 读写有问题时,可以先考虑将qspi降成 spi模式,也就是将 4线模式转换成 1 线模式,或者是降低 IO频率;模型如下图所示。IO 频率在驱动的硬件cfg 参数中修改即可。

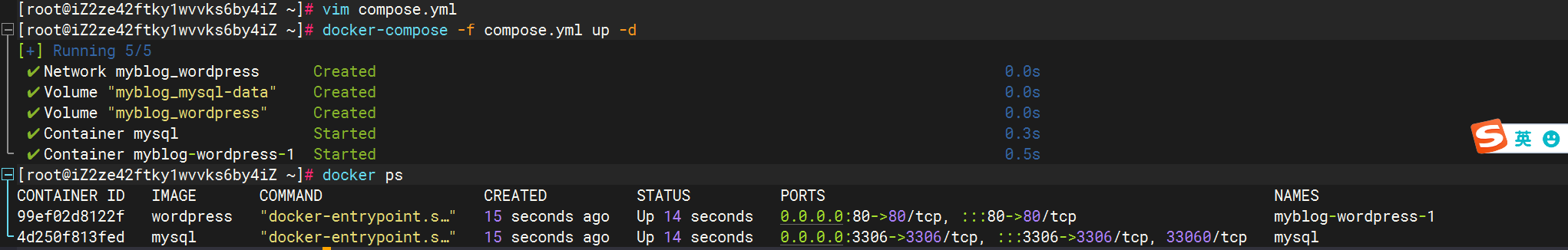

3、修改上面的qspi 的IO 参数只会在 fsbl 阶段生效,进uboot 和 kernel 时,还需要修改设备树中的 qspi 驱动的 IO频率(这里其实我不是很清楚,好像u-boot 中使用到的 qspi 的 io 频率和fsbl 阶段是一致的)。具体的做法是可以编译一个 baremental下的 fsbl,然后替换进 fsbl下的fsbl.elf ,把 build.sh 中的build_fsbl注掉;然后将 spi-anlogic-qspi.h 中设置分频系数的qspi_set_clk 函数中的实现注掉,不需要进行设置 clk;将anlogic_qspi.c中的 al_write(priv, AL_QSPI_BAUDR, clk_div);注掉;将sdk/fsbl 下的 qspi 的io freq改成 10M ;修改下面两个设备树中的频率和sample-delay:

硬件问题:

1、EC前芯片能使能各项外设,在测试过程中发现能够读 flash ID ,但是在boot的过程中会遇到问题,包括之前boot的大电流问题;测试过程中还发现nand 也会存在这个问题,所以当存在boot 失败的情况,可以先考虑换芯片;

2、芯片的 socket 在安装时要旋紧,如果怀疑芯片存在接触问题,可以考虑在芯片上方塞张纸片,使得芯片与底座接触更加紧密。

3、Nor flash socket接触问题,因为 sop-8 以及 sop-16 的引脚与老化座接触 或者老化座与 DC 板接触可能存在问题,所以如果代码跑不通,或者读flash id 存在问题时,可以尝试把 flash 按住,帮忙紧固,跑一遍测试程序,或者调整一下 dummy / sample-delay参数,对于 m90 而言,当 qspi io 的频率在 33 M以上时,sample-delay值为 1 或2或 3,在 33M 以下时,sample delay 值为 0 . 否则会出以下问题:

4、老化座安装flash 时,需要注意片选信号和flash 供电电压,对比原理图和 DC 板,看电路的导通情况,以及mio 端电阻的导通情况,一般是两个 老化座 会选一个导通,nand 和 nor 会选一个导通,也要注意 nor 的供电电压情况,安装flash 之前要先检查 flash 的容量和供电电压,电压不对会导致芯片发烫,会烧坏芯片,flash 容量不对会导致烧录过程fail 或者校验过程fail ,在一个 8M 的flash 烧录 image.bin 时发现了只能跑完 u-boot ,这是因为image烧录不完整,要先检查;

5、DC 板上的 emmc 是0 ; mlk 板子上的 emmc 是 1 ;

6、jtag 不通时,可以使用直流电源或者交流电源对各个模块分开供电;