1 目录

(a)FPGA简介

(b)Verilog简介

(c)时钟简介

(d)时序收敛二

(e)结束

1 FPGA简介

(a)FPGA(Field Programmable Gate Array)是在PAL (可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

(b)FPGA工程师就业应用于通信、航空航天、汽车电子,还是人工智能、物联网等新兴领域。

(c)尽管FPGA在芯片领域具有如此重要的地位,FPGA工程师具有薪资高、待遇好、前景广阔、晋升快,但目前全球FPGA人才缺口任高达数十万,国内更是供不应求。

2 时序收敛

(a)时序收敛的定义和重要性

时序收敛(Timing closure)是现场可编程逻辑门阵列(FPGA)和专用集成电路(ASIC)等集成电路设计过程中的一个重要概念。它指的是调整、修改设计,从而使设计的电路满足时序要求的过程。时序收敛对于确保电路能够按既定的顺序执行特定功能至关重要,系统内不同单元电路的处理速度和走线延迟等因素都会影响时序收敛。

(b)时序收敛的过程和方法

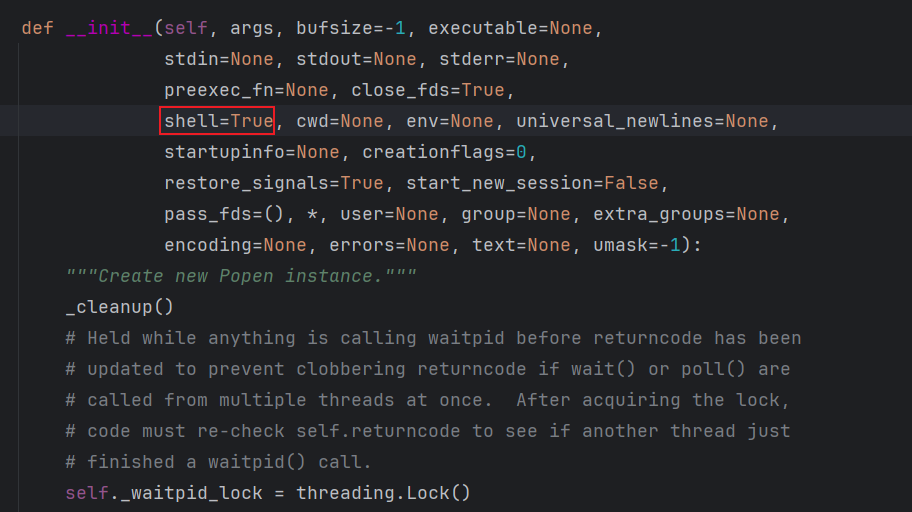

解决FPGA设计中时序不收敛问题的方法包括考虑模块运行时钟频率、优化HDL代码风格和逻辑、管理组合逻辑