- 组合逻辑电路输入和输出之间是确定关系,与之前的历史记录没有任何关系。

- 时序逻辑电路则有相应的存储元件,要把之前的状态保存起来。

要构成时序逻辑电路,必须要有相应的存储元件,第五章讲述相应的存储元件

一、半导体存储电路概述

1.存储电路及其分类

寄存器和半导体存储器都包含了许多单元。

2.存储单元的分类

动态存储单元的工作速度要比静态的慢

动态存储单元的工作速度要比静态的慢

3.存储单元的触发方式与逻辑功能

4.存储单元按触发方式分类

二、由两个或非门构成的SR锁存器

1.SR锁存器的电路结构

2.由两个或非门组成的SR锁存器的工作原理

分析过程:将初始状态标上去,然后做反馈

约束条件就是不允许的条件

约束条件就是不允许的条件

3.由两个或非门组成的SR锁存器的真值表/特性表

4.有两个或非门组成的SR锁存器的逻辑函数/特性方程

5.由两个或非门组成的SR锁存器的图形符号

5.由两个或非门组成的SR锁存器的图形符号

三、由两个与非门构成的SR锁存器

或非门是高电平有效,与非门是低电平有效

1.由两个与非门组成的SR锁存器的图形符号

2.由两个与非门组成的SR锁存器的工作原理

3.由两个与非门组成的SR锁存器的真值表/特性表

4.由两个与非门组成的SR锁存器的逻辑函数/特性方程

由此可以发现,或非门和与非门组成的逻辑函数和逻辑功能是一样的,只是电路组成不一样,以后看到SR,就可以知道,他们是实现同一类逻辑功能的电路

5.SR锁存器的动作特点

同时消失时,才为不定状态

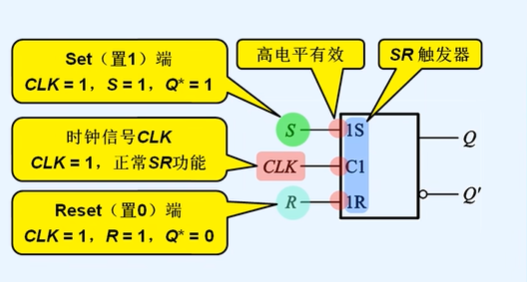

四、电平触发的SR触发器

1.电路结构

锁存器的基础上,增加一个触发信号输入端

2.工作原理

3.真值表/特性表

4.图形符号

5.带异步置位、复位端的电平触发的SR锁存器

6.电平触发方式的动作特点

例题

为了适应只有一个信号的单端触发的需求,对电路结构做出改变,引出了D触发器

五、电平触发的D触发器

1.电路结构

2. 工作原理

3.特性表与特性方程

4.图形符号

5.利用CMOS传输门组成电平触发的D触发器

例题

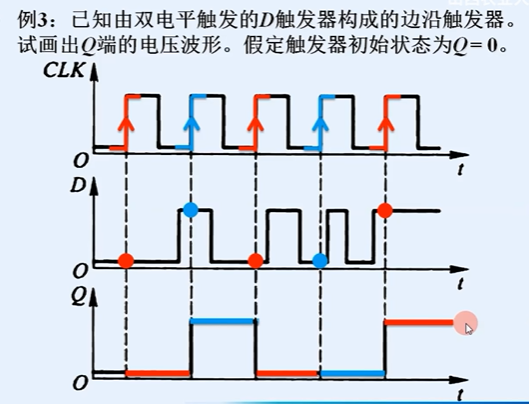

六、边沿触发的D触发器

1.电路结构

为提高触发器的可靠性,增强抗干扰能力,希望触发器的次态仅仅取决于CLK的下降沿(或上升沿)到来时的输入信号状态

2.工作原理

3.特性表与特性方程

4.图形符号

5.带异步置位、复位端的边沿触发的D触发器

6.边沿触发的两类触发方式

7.边沿触发方式的动作特点

例题

七、脉冲触发的SR触发器

1.电路结构

2.工作原理

上升沿到来不影响输出

下降沿到来不影响输出,要加一个完整的高电平再加下降沿

2.工作原理

3.输出特性

4.特性表与特性方程

5.图形符号

6.脉冲触发的两类触发方式

7.主触发器的翻转特性

脉冲触发需要考虑整个高电平期间的影响,而边沿触发只考虑一瞬间

例题

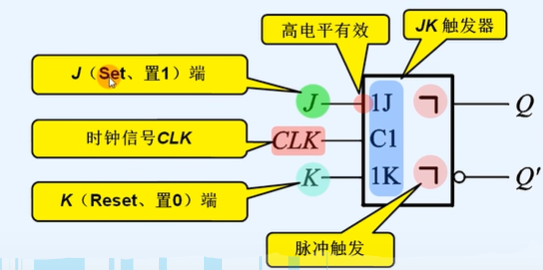

八、脉冲触发的JK触发器

为了接触约束条件

1.电路结构

2.工作原理

引入反馈端主要是为了解决同时为1的情况

3.特性表与特性方程

4.图形符号

5.主触发器的翻转特性

6.脉冲触发方式的动作特点

例题

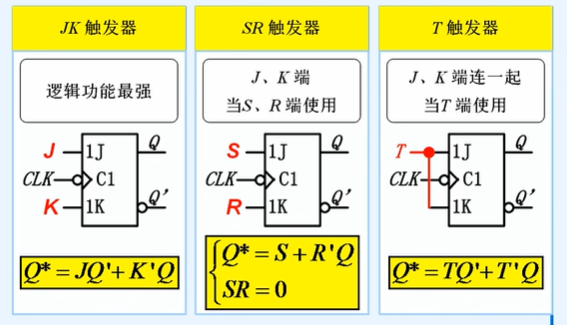

九、触发器按逻辑功能的分类

1.触发器按逻辑功能的分类

2.SR触发器

3.JK触发器

3.D触发器

4.T触发器

5.不同触发器间的关系

目前,触发器的定型产品中,只有JK触发器和D触发器。

![[Raspberry Pi]如何將看門狗(WatchDog)服務建置在樹莓派的Ubuntu作業系統中?](https://i-blog.csdnimg.cn/direct/d5b282134bf5461a9c278caac923d354.png)