来源:铁头山羊

基本概念

①ADC是模数转换器的统称,stm32f103c8t6内部集成了2个12位主次逼近型ADC,外设名称为ADC1、ADC2。

② 采样深度为12位意味着ADC可以将0~3.3V的模拟电压等比转换为0~4095的数字值(分割为2的12次方份)。采样深度表示用多少位二进制数来表示一个采样点,采样深度越深转换结果越精细。

③不同类型ADC的对比

④内部等效集成电路模型

采样原理

基本结构框图

太复杂了简化一下

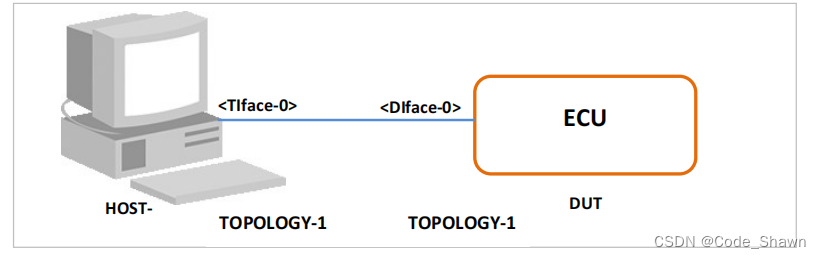

ADC有两种使用(触发采样)方式,常规序列与注入序列,外设检测到输入脉冲之后会开始采集。

采样时间与转换时间

逐次逼近型ADC的电压信号采样原理和使用砝码天平称重十分类似,砝码的来源是VSS引脚(夹带个私货,高精尖的东西推荐大家使用高精度基准芯片,而不是简单用Π型滤波器和VCC连上)。12位的二进制数值中高位的“1”就好比较重的砝码,低位的“1”就好比较轻的砝码。采样时间就相当于放重物的时间,转换时间相当于调整砝码的时间。

ADC的时钟源

从时钟树上可以判断出来,ADC1与ADC2外设挂载在APB2上。

但是出于对采样精度的考量,ADC和APB2总线之间隔着一个分频器,分频后ADC接收的时钟信号不能超过14MHz。注意ADC的采样时间与转化时间都是时钟周期的倍数。

计时方式

假设输入ADC的时钟频率就是14MHz,那么时钟周期就是1/14M=1/14us。如果我们设置采样时间为0.1us,那么就可以设置为1.5个时钟周期(1.5 cycle),转换时间也是同理。

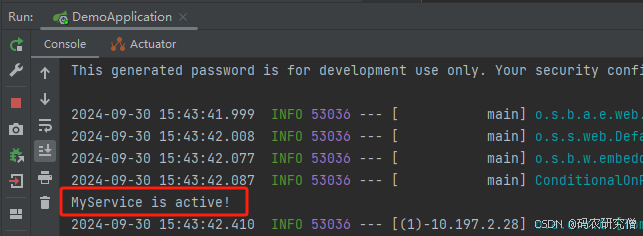

转换时间的计算方式

固定值如上图片所示

采样时间的计算方式

“开关”、“电容”都是上述采样保持电路中的模型,电容两端的电压和充电电压之间存在误差,但是充电时间越长误差就越小,所以采样时间越长误差就越小。

但我们也不能无限延长采样时间,采样误差应该小于ADC分辨率的四分之一。

带内阻的信号源框图

由于采样保持电容和信号源内阻是串联关系,内阻越大充电电流就越小,充电速度也就越低,采样时间也就越长。

最佳采样时间计算公式:

其中Radc约等于1KΩ,Cadc约等于8pF,N是采样深度,此处为12,综上推导出:

注意ADC的实际采样时间只有几个固定挡位,参考ADC->Parameter Settings->ADC_Regular_ConversionMode->Rank->Sampling Time