一、matlab生成任意长度余弦波coe文件

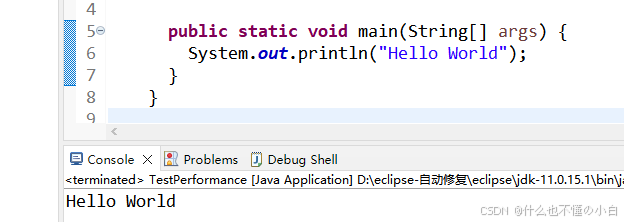

clear

clc

close all

width=32; %rom的位宽

depth=3600; %rom的深度

x=linspace(0,2*pi,depth); %在一个周期内产生3600个采样点

y_cos=cos(x); %生成余弦数据

y_cos=round(y_cos*(2^(width-1)-1))+2^(width-1)-1; %将余弦数据全部转换为整数

%y_cos=dec2hex(y_cos);

fid=fopen('C:\rom_coe\rom_cos_3600x32b.coe','w'); %创建.coe文件

% 写入 COE 文件头

fprintf(fid, 'memory_initialization_radix=16;\n');

fprintf(fid, 'memory_initialization_vector=\n');

for i = 1:length(y_cos)fprintf(fid,'%x',y_cos(i)); %向.coe文件中写入数据if i < length(x)fprintf(fid, ',');elsefprintf(fid, ';');endfprintf(fid, '\n');

end

%关闭.coe文件

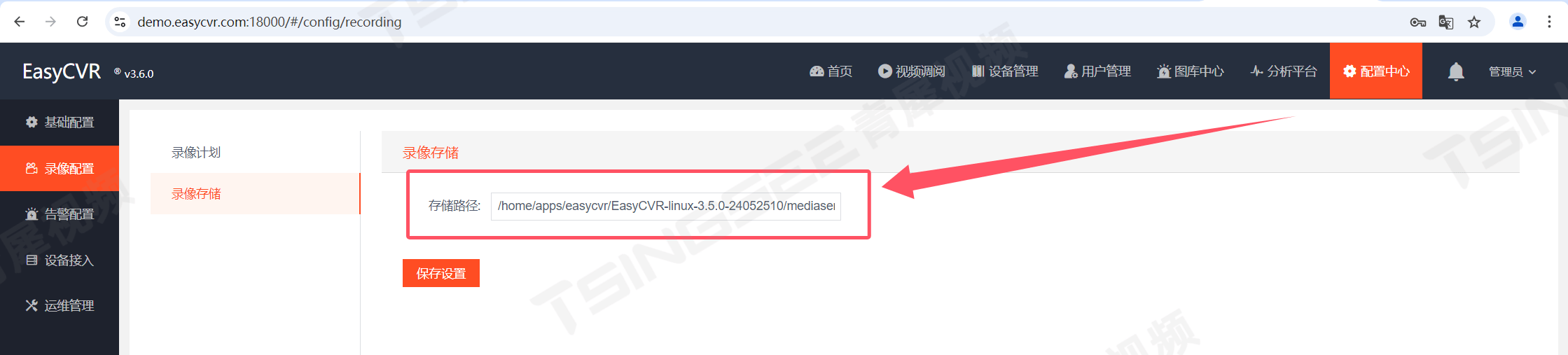

fclose(fid); 二、Block RAM IP配置

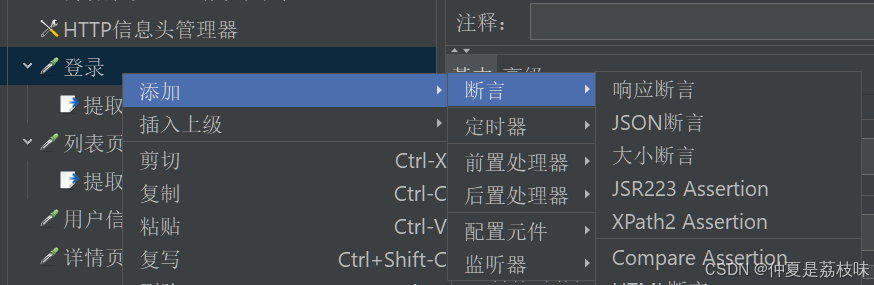

三、verilog tb测试文件

matlab生成的是带偏置的波形,在verilog中减去偏置即可。

module sim_1_read_cos( );reg clk_100m=1'b1;

reg [11:0] rd_addra=12'd0;wire [31:0] dout_32b;

reg [31:0] dout_32b_rectify;

integer i;

initial beginrd_addra = 12'd0;#100for(i=0;i<=4095;i=i+1)begin#10 rd_addra = rd_addra + 1'b1;end

endalways #5 clk_100m = ~clk_100m;

//减去偏置

always@(posedge clk_100m) begindout_32b_rectify <= dout_32b - 32'h8000_0000;

endbrom_4096x32b u_brom_4096x32b (.clka ( clk_100m ), // input wire clka.addra( rd_addra ), // input wire [11 : 0] addra.douta( dout_32b ) // output wire [31 : 0] douta

);

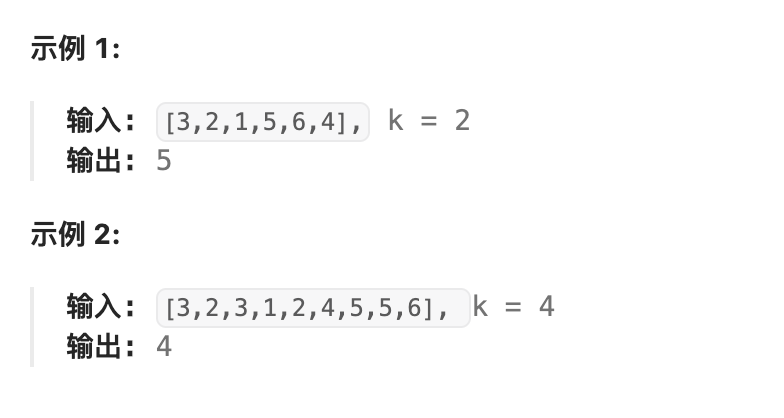

endmodule四、仿真结果