3 PCIe 4.0 SerDes

和 5.0 SerDes 要求比较

表 2 总结 PCIe 4.0 和 5.0 SerDes 要求之间的差

异。PCIe 标准包含三个相互依赖的规范,这些规范

旨在确保不同供应商的 SerDes 和通道的互操作性:

● PCIe BASE 规范定义了整个协议栈的芯片

级性能,是一份超过一千页的综合性文件。

● PCIe CEM(卡机电)规范规定了插卡连接器

处设备的最低性能。

● 测试规范规定了一致性测试的规则。

从表 2 看出,PCIe 4.0 和 5.0 有很多共同之处。

两者都使用 NRZ 调制、128B/130B 编码、相同的

10 -12 比特误码率目标,并且具有相同的连接器引脚。

发射机使用相同的前馈均衡器(FFE)方案,并有 11

组抽头 Preset,P0-P10。主要特征:

一是 PCIe 5.0 的参考接收机均衡方案更复杂;

其与 PCIe 4.0 中使用的 2 极点 1 零点的连续时间线

性均衡器(CTLE)响应不同,PCIe 5.0 使用的是 4 极

点 2 零点的 CTLE 滤波器响应(见图 2)。

二是新的 CTLE 更灵活,增益更大,从 -5 到

-15 dB。PCIe 5.0 也增加了参考接收机判决反馈均

衡器(DFE)的第 3 个抽头。

三是发射机摆幅要求不变。在 PCIe 4.0 和 5.0 中,

抖动要求以 UI 为单位是相同的,以 ps 为单位是按比

例变窄。分布式参考时钟或公共时钟(CC)结构在

PCIe 4.0 中是可选的,但现在 PCIe 5.0 中是必需的。

四是由于从 16 GT/s 提高到 32 GT/s 的最大困

难是最大允许损耗从 -28 dB 增加到 -36 dB,因此

毫不奇怪,通道要求已经重新定义,CEM 规范中的

插卡只允许使用表面安装连接器,也就是说,不允许

使用过孔连接器。

五是损耗的增加使 PCIe 5.0 引入新的一致性测

试板。可接受的用于一致性测试的 PCIe 测试夹具只

能从 PCI-SIG 协会获得。测试夹具包括模拟主板的

合规基板 (CBB) 和模拟插卡和通道的合规载板

(CLB);两者都可以通过复位和发射机 Preset 切换

进行外部控制。

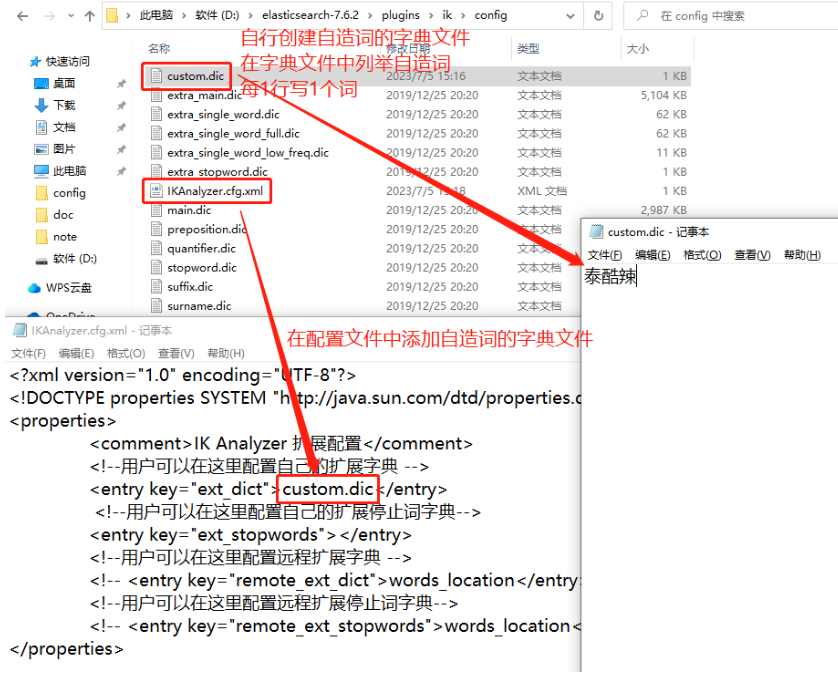

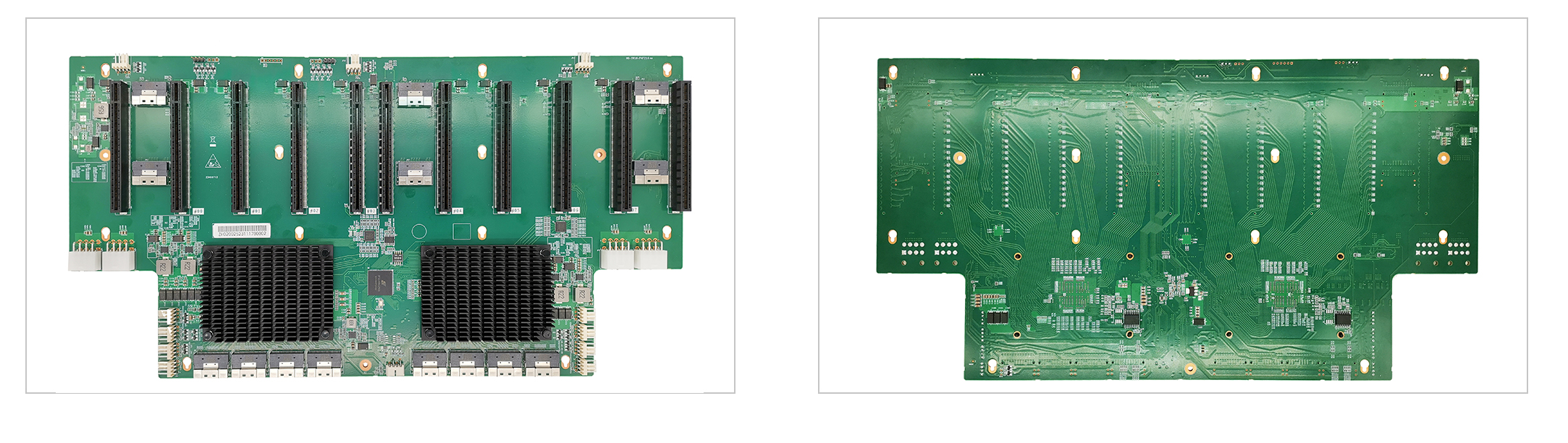

============10槽PCIe Switch GPU底板(PCIe 4.0/PCIe5.0)==========

• 1个直连的单宽槽位;

• 14* SFF-8654x4 PCIe4.0/5.0主机接口;

• 11* PCIe4.0 x16插槽;

• 4*CPU 8Pin 电源接口;

• 11* 4 针风扇接口;

• 1*IPMB接⼝;

功能特性

| 产品规格 | 10槽 switch 底板(PCIe 4.0) |

| 型号 | MG-SW10-P4F216-V11 |

| 主机接口 | 14* SFF-8654x8 PCIe4.0 |

| PCIe插槽数 | 11* PCIe4.0 x16 |

| 电源接口 | 4* CPU 8PIN |

| IPMB接口 | 1*4Pin BMC I2C |

| 尺寸 | 420(长) x 225(宽) x 2.5(高) (mm) |

☑支持OEM/ODM定制服务