UCIE协议系列-1

- 1 UCIE背景

- 1.1 UCIE产生背景

- 1.2 UCIE主要特性

- 2 UCIE分层协议

- 2.1 Protocol 层

- 2.1.1 Mode VS protocal

- 2.1.2 PCIe 6.0

- 2.1.2.1 Raw Mode for PCIe 6.0

- 2.1.2.2 Flit Mode: Standard 256B Flit for PCIe 6.0

- 2.1.3 CXL3.0 256B Flit Mode

- 2.1.3.1 Raw Mode for CXL 2.0 or "CXL 68B-Enhanced Flit Mode

- 2.1.3.2 Flit Mode: 68B Flit for CXL 2.0 or "CXL 68B-Enhanced Flit Mode"

- 2.1.4 Streaming Protocal

- 2.1.4.1 Raw Mode for Streaming protocol

- 2.2 Adapter层

- 2.2.1 Link Initialization

- 2.2.2 Modes of operation and protocols

- 2.3 Phy 层

- 2.3.1 UI双时钟沿传输

UCIE(Uviversal Chiplet Interconnect Express)–旨在构建一种通用、开放、支持CXL/PCIE/自定义协议等多协议的用于连接同一封装中的多个片上Chiplet(芯粒)间互联互通的标准;

UCIE协议虽然是2022年新出的,但是在具体理解UCIE协议时可以类比着熟悉的PCIE协议进行对照理解;

1 UCIE背景

1.1 UCIE产生背景

UCIE为什么会产生?其本质还是为什么Chiplet会产生?

UCIE的产生是建立在多Chiplet产生后的需求上。

1.摩尔定律放缓(失效):先进工艺制程不能无限制小;通过将多个 Chiplets 集成,利用 UCIE 这样的先进互连技术,可以在不依赖于制程节点进一步缩小的情况下,实现性能的提升和功能的创新;

2.降低成本、模块专业化:Chiplet 技术可以将大型芯片分解成多个小型Chiplets,每个Chiplet可以使用不同的工艺制程,比如CPU,GPU,NPU,I/O等可以分别专门定制一个适合自己制程节点的Chiplet;这种设计方式可以极大提高良率,降低流片成本,基础前提是制程越先进,他的良率越低流片越贵,一方面也是降低了芯片流片失败的风险;定制专门的Chiplet也可以像类似IP一样进行卖出去;

3.标准化、灵活和可拓展性:由于Chiplet的通用标准,可以使得封装的芯片来自不同的厂家,UCIE可以允许将不同功能的 Chiplets 进行灵活组合,使得芯片设计可以根据具体的应用需求进行定制,提高了设计的可扩展性;

类比想象:搭积木拼接的样子,有的是大粒度的积木,有的是小粒度的积木,有的是来自A厂家,有的是来自B厂家,有的是自研,但最后拼成一个需求的积木

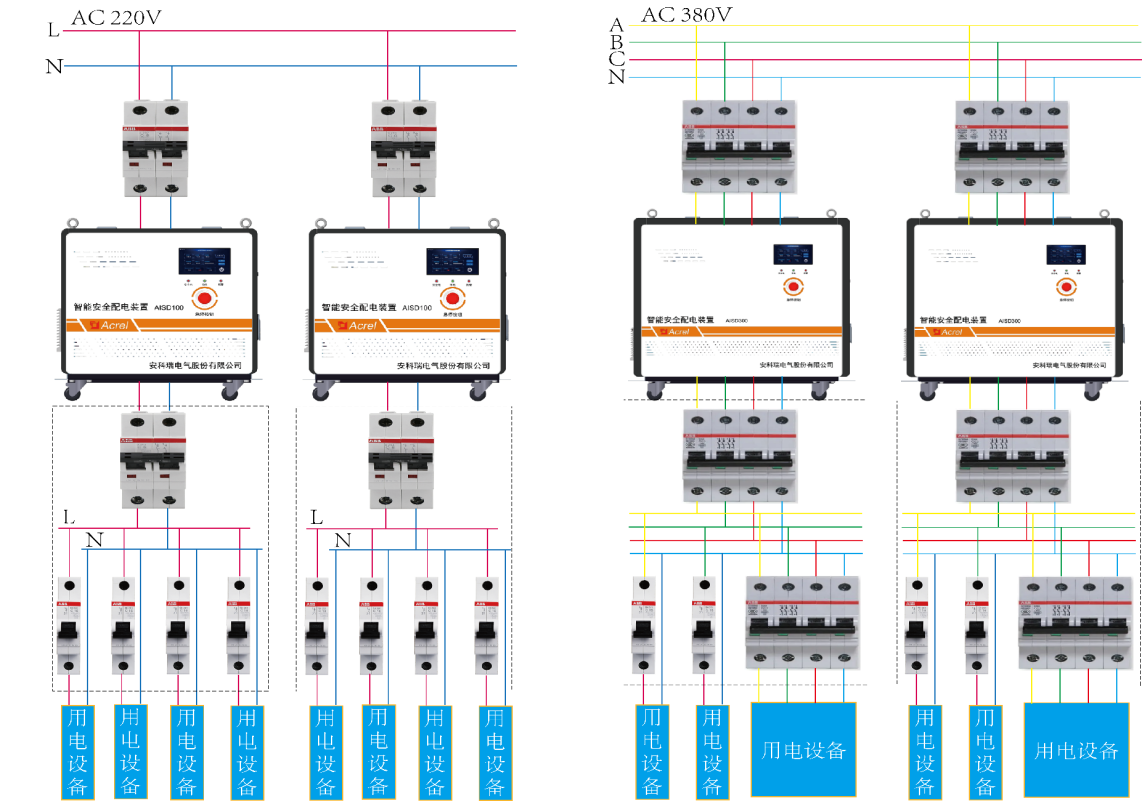

下图UCIE标准协议手册非常形象的表达:

1.2 UCIE主要特性

UCIe 主要特性如下:

- UCIe 从 PCIe 扩展而来,是个分层协议,协议层支持 PCIe 6.0 及 CXL 2.0/3.0 的生态以及Streaming Protocal自定义协议。

- UCIe 支持 X16 Standard 及 X64 Advanced Package 两种封装模式,不同条件下单 Lane 支持的传输速率有 4, 8, 12, 16, 24, 32 GT/s。

- UCIe 物理链路上有 Mainband 及 Sideband 两大数据通路。

- 单个 UCIe Adapter 可桥接多协议栈,支持多个物理层 Module。

- UCIe 主要应用为 On-Package Chiplet 板上互连,也支持基于 Retimer 的 Off-Package 长距离互连。

- 误码率极低,低速时 BER<1e-27,高速时 BER<1e-15。

- 不同工艺制程的 Chiplet 可以通过 UCIe 链路互连。

- 主打低延时、低功耗、高带宽密度。

2 UCIE分层协议

UCIE协议是一个规范标准,是基于分层的协议,其协议层各司其职,便于通用和复用,明确每层要支持的功能;按照层级可分为:PHY层、Adapter层和Protocal层;层与层之间为标准接口进行连接:PHY层和Adapter层之间接口为RDI;Adapter层和Protocol层之间接口为FDI;

2.1 Protocol 层

2.1.1 Mode VS protocal

- Raw Mode:PCIE6.0、CXL2.0/3.0都支持一种模式叫Raw Mode,用于自定义的Streaming协议只支持RAW Mode,在这模式下,所有64B或者256B数据都由协议层来负责填充,bypass适配层,CRC、FEC和Retry都由协议层来处理;

- Flit Mode:适配层要对协议层进行添加做2B hdr和2B CRC;协商过程中,适配层通过FDI接口把这些信息作为Link Trainning的一部分传给协议层;

UCIE协议层支持映射PCIE6.0、CXL2.0/3.0协议,同时还支持Steaming协议(用来映射自定义传输协议);

– PCIe 6.0 Flit Mode

– CXL 2.0,“CXL 68B-Enhanced Flit Mode”,“CXL 256B Flit Mode”:如果协商使用CXL,将独立协商CXL.io、CXL.cache和CXL.mem协议。

– 流式传输协议:这提供了用于通过UCIe传输用户定义协议的通用模式。

协议层的互操作性要求如下(这个协议互操作的标准要求,是协议规定的,可以暂且压在这不表):

- 如果协议层宣称支持PCIe,它必须支持CXL 2.0规范中定义的CXL.io协议的68B Flit Mode。

- 如果协议层支持"CXL 256B Flit Mode",它必须支持PCIe 6.0 Flit Mode和CXL 2.0规范中定义的CXL.io协议的68B Flit Mode。

- 宣称支持CXL的协议层只允许支持CXL 2.0或CXL 68B-Enhanced Flit Mode,而不支持"CXL 256B Flit Mode"或PCIe 6.0 Flit Mode。

2.1.2 PCIe 6.0

UCIe仅支持PCI Express Base Specification Revision 6.0中定义的Flit模式。对于PCIe,UCIe支持两种操作模式,这些模式将在下面具体进行介绍。灰色的字节表示适配器插入的信息,在这些信息作为Flit的一部分显示的情况下(例如在标准的256B Flit中),协议层必须在发送端将其设置为0,并在接收端忽略它们。

2.1.2.1 Raw Mode for PCIe 6.0

这种模式是可选的,但是PCIE协议支持的模式;在UCIE中其预期用途是用于传输PCIe协议的UCIe Retimers。一个示例用途是,当CPU和I/O设备位于不同的机架/机箱中,并通过使用Off-Package Interconnect的UCIe Retimer来连接。其协议格式如下图所示:对于原始模式,重传、CRC和FEC全部由协议层处理,bypass 适配层,其所有64个字节都由协议层填充。

2.1.2.2 Flit Mode: Standard 256B Flit for PCIe 6.0

当支持PCIe协议时,这种模式是强制性的,是PCIE6.0中定义的标准Flit格式。协议层必须按照FDI上的Flit传输的Flit格式,在保留给Die-to-Die Adapter的字段上设置为0。

其具体协议格式如下:

2.1.3 CXL3.0 256B Flit Mode

该协议有四种可能的操作模式,这些模式在下面的子节中定义。适配器会插入灰色字节。在这些字节被显示为主数据路径的一部分的情况下(例如在标准的256B Flit中),协议层必须在发送端将其设置为0,并在接收端忽略它们。

2.1.3.1 Raw Mode for CXL 2.0 or "CXL 68B-Enhanced Flit Mode

重传和CRC由协议层处理。所有的64个字节都由协议层填充。这个和上面是类似的;

2.1.3.2 Flit Mode: 68B Flit for CXL 2.0 or “CXL 68B-Enhanced Flit Mode”

协议层在FDI上呈现Flit的64B(不包括协议ID和CRC),而Die-to-Die适配器则插入2B的Flit头和2B的CRC,并执行所需的字节移位,以按下图所示的格式排列Flits。

2.1.4 Streaming Protocal

如果不打算向远程链路使用和协商任何PCIe或CXL协议,可以根据自己的要求对UCIe协议进行扩展,以实现更多的功能或适应特定的应用场景,就是Streaming Protocal.

2.1.4.1 Raw Mode for Streaming protocol

这种模式是流式协议支持的强制要求。协议层将使用64个字节的数据进行传输,这些数据全由协议层填充,并通过物理链路进行传输。

【小结】:协议层关注帧格式的字节填充,以上只是举部分例子帮助理解;

2.2 Adapter层

Die-to-Die适配器的职责包括:

• 可靠的数据传输(在适用时执行CRC计算和重传,或进行奇偶校验计算)

• 管理仲裁和多路复用(针对多个协议层)

• 链路状态管理

• 与远程链路伙伴进行协议和参数协商。

当协议层发送64B Flit数据,会在前加上2B hdr(Protocol ID,Stack ID)和后面加上2B CRC值;对于256B Flit需要额外增加2B CRC;

UCIe允许在同一物理链路上多路复用两个协议栈。当每个协议栈需要物理层提供带宽的一半时,支持在同一物理链路上多路复用两个协议栈。

2.2.1 Link Initialization

链路初始化在主通道上开始协议Flit传输之前需要经过四个阶段:

- 第0阶段是特定于每个芯片的,并且独立进行;

- 第1阶段涉及旁路检测和训练;

- 第2阶段涉及主通道训练和修复;

- 第3阶段涉及适配器之间的参数交换,以协商协议和Flit格式;

FDI bringup: 一旦参数交换成功完成,适配器将结果反映到FDI上的协议层,一旦FDI处于活动状态,就完成了链路初始化的第3阶段,协议Flit传输可以开始。

2.2.2 Modes of operation and protocols

下面灰色的部分字节才由适配器层来填充;

- Raw Mode for all protocols

原始模式只能用于不需要适配器支持重传的场景。如果针对CXL或PCIe协议协商了原始模式,那么适配器将在协议层和物理层之间传输数据而不进行任何修改。

2.CXL 2.0 or “CXL 68B-Enhanced Flit Mode”

协议层发送64字节的协议信息。适配器在其前面添加了两个字节的Flit头部和两个字节的CRC后缀(计算协议层的64字节数据和适配器的2字节Flit头部)。

3.PCIe 6.0 or “CXL 256B Flit Mode” with Standard 256B Flit

协议层以256B Flit的形式发送数据,但在适配器保留的字节上驱动0(在图29、图30和图31中以灰色显示),由适配器填充;

- “CXL 256B Flit Mode” with Latency-Optimized 256B Flit

这里也是直接协议格式看看即可:

2.3 Phy 层

物理层主要包括以下功能:

• 链路初始化、训练和电源管理状态

• 字节到Lane的映射,用于通过Lane传输数据

• 互连冗余重映射(在需要时)

• 发送和接收侧带消息

• 扰码和训练模式生成

• Lane反转

• 宽度降级(如果应用)

物理层分为逻辑物理层和电气物理层;我们只需要关注逻辑物理层:即Lane概念;

数据包是通过Byte形式发出的,一个Byte占用一个Lane使用4个clk传输;Main_band采用DDR的双沿采样;

2.3.1 UI双时钟沿传输

每个字节都在单独的Lane上进行传输。字节0(B0)在Lane 0上传输,字节1在Lane 1上传输,以此类推。

一个Lane上传输一个Byte,一个Byte需要传输8(0~7)个UI;这样就方便看下图了:

- 64个lane传输256个Byte只需要32个UI;

- 32个Lane传输256个Byte需要64个UI;

- 16个lane传输256个Byte需要128个UI;

以上主要介绍了UCIE的分层协议介绍;

【REF】

1.https://mangopapa.blog.csdn.net/article/details/126554806

2.https://blog.csdn.net/weixin_56793272/article/details/133771548